# 8088 System Board with Signal Reception Interface

P1272 Project Work

1989 - 90

Submitted in partial fulfilment of the requirements

for the Award of the Degree of Bachelor of Engineering in

Electronics and Communication Engineering

of the Bharathiar University, Coimbatore-641 (46)

Submitted by

M. Tenugopal

R. Nambirajan

R. Vaidyanathan

U. S. Neelakantan

Under the Guidance of

Dr. S. Padmanabhan, B.E(Hons.), M. Tech .. M.E. Ph.D.

Department of Electronics and Communication Engineering

Kumaraguru College of Technology

Coimbatore - 641 006

## Department of Electronics and Communication Engineering Kumaraguru College of Jechnology

Coimbatore - 641 006

| This is certify that                      | the rep   | ori entitle                             | d         |        |            |

|-------------------------------------------|-----------|-----------------------------------------|-----------|--------|------------|

| 8088 System Board with S                  | Signal    | Rec <b>ept</b> io                       | n Inte    | rface  |            |

| has been su                               | ıbmitted  | ву                                      |           |        |            |

| Mr                                        |           |                                         |           |        |            |

| In partial fulfilment                     | for the   | award of                                |           |        |            |

| Bachelor of Engineering in Electronic     | es and C  | ommunicati                              | ion Engin | eering |            |

| Branch of Bharathiar Univ                 | ersity, C | oimbator <b>e</b> -6                    | 41 046    |        |            |

| during the acaden                         | nic year  | 1989-90                                 |           |        |            |

| Guide Guide                               | ,         |                                         | Cead of 1 |        |            |

| Certified that the candidate was Examined |           |                                         | project   | work   | Uwa - Voce |

| Examination held on                       |           |                                         |           |        |            |

| University Register Number was            |           |                                         |           |        |            |

|                                           |           |                                         |           |        |            |

| Internal Examiner                         |           | *************************************** | External  | Exam   | line       |

## **ACKNOWLEDGEMENT**

We wish to thank our Principal Prof. R. PALANIVELU for providing ample facilities for the completion of this project work.

We also wish to thank and express our heart felt gratitude to our Professor and Head of the Department Dr. S. PADMANABHAN, for having given us the idea about this project and for guiding us through this work.

We also thank the staff members, students and friends for giving support and encouraging us through this work.

## SYNOPSIS

The project comprises of the design and fabrication of an 8088 Add-on board to the existing 8085 and Z80 kits. This involves the design and fabrication of the proto type card, developing the monitor program for the use and testing sample programs in the developed board. The board is designed such that it can be inserted in the same edge connector sockets of the 8085/Z84 board.

A signal receiver card using the ADC 0804 is also developed. The software for signal reception is also dealt with and discussed.

## CONTENTS

| Chapter | No. |                                       | Page | No.        |

|---------|-----|---------------------------------------|------|------------|

|         |     | Particulars                           |      |            |

|         |     | INTRODUCTION                          |      | 1          |

| 1       |     | DESCRIPTION OF THE CIRCUIT            |      | 3          |

|         |     | 1.1 SYSTEM BOARD                      |      | 3          |

|         |     | 1.2 SYSTEM PROCESSOR                  |      | 7          |

|         |     | 1.2.1 The 8088 MPU                    |      | 8          |

|         |     | 1.2.2 Segmented Memory                |      | 13         |

|         |     | 1.3 MEMORY DEVICES                    |      | 15         |

|         |     | 1.3.1 6116 RAM                        |      | 15         |

|         |     | 1.3.2 EPROM                           |      | 21         |

|         |     | 1.4 SYSTEM CLOCK                      |      | 22         |

|         |     | 1.4.1 8284 Clock Generator and Driver |      | 22         |

| 2       |     | ADC INTERFACE                         |      | 24         |

|         |     | 2.1 SIGNAL RECEPTION AND ANALYSIS     |      | 24         |

|         |     | 2.2 DATA CONVERTERS                   |      | 25         |

|         |     | 2.3 MICROPROCESSOR INTERFACE          |      | 30         |

|         |     | 2.4 WHY THE MICROPROCESSOR? - 8088    |      | 32         |

|         | •   | 2.5 ADC INTERFACE                     |      | 33         |

| 3       |     | INTERRUPTS IN 8088                    |      | 37         |

|         |     | 3.1 INTERRUPTS IN 8088                |      | 37         |

|         |     | 3.1.1 Type - 1 Interrupt              |      | <b>4</b> i |

|         |     | 3 1 2 Type - 2 Interrupt              |      | 14         |

| Chapter | No. |        |            |                                                     | Page | No             |

|---------|-----|--------|------------|-----------------------------------------------------|------|----------------|

| 4       |     | SOFTWA | ARE LISTIN | GS                                                  |      | 45             |

|         |     | 4.1    |            | PROGRAM AND THE USE<br>088 BOARD DEVELOPED          |      | 45             |

|         |     |        | 4.1.1      | Sample Program to illustrate the 8088 instructions. |      | 45             |

|         |     |        | a)         | Program to find the average of number of bytes.     |      | 46             |

|         |     |        | b)         | Binary multiplication                               |      | 47             |

|         |     |        | c)         | division                                            |      | 48             |

|         |     |        | d)         | String transfer instructions                        |      | 48             |

|         |     | 4.2.   | ADC PROG   | RAM                                                 |      | 51             |

|         |     | 4.3    | 8088 MONI  | TOR PROGRAM LISTING                                 |      | 56             |

| 5       |     | APPLI  | CATIONS    |                                                     |      | 53             |

|         |     | 5.1    | APPLICAT   | IONS                                                |      | <del>6</del> 3 |

|         |     | 5.2    | SCOPE FO   | R IMPROVEMENT                                       |      | 64             |

|         |     | 5.3    | ADVANTAG   | ES                                                  |      | ó4             |

| 6       |     | FABRI  | CATION     |                                                     |      | 35             |

| 7       |     | CONCL  | USION      |                                                     |      | 66             |

|         |     | BIBLI  | OGRAPHY    |                                                     |      |                |

APPENDIX

#### INTRODUCTION

In the last decade, microprocessors have had a major impact in the area of industrial process control. The introduction of fast 16-bit microprocessors like the 8086/8088 have added a new dimension towards control capabilities.

The microprocessor is a general purpose programmable logic device. The microprocessor requires both concepts and skills both hardware and software. The hardware is the physical structure of the microprocessor while the software concerned makes it come alive.

This project is centred around the 8088, which can be used for analysis of signals received that can be used for control applications.

The 8088 which was introduced after the 8086 retained all the powers of 8086, including the 16 bit manipulations of Arithmetic and logic, but the external data bus was made to have just 8 bits for convenience. Hence, the 8088 became more popular for it simplified the hardware and retained the 16-bit power. The 8088 board designed and fabricated here is compatible with the hexadecimal keyboard and input/output board. It can be inserted in the same edge connector sockets of the 8085/Z-80 board. A signal receiver card with ADC 0804 is developed.

#### CHAPTER - 1

#### DISCRIPTION OF THE CIRCUIT

#### 1.1 SYSTEM BOARD

The 8088 has built-in logic to handle bus access priorities in multi-chip systems. In such systems each processor will have its own memory and each processor can also share a common memory. The 8088 has a 16 bit data path internally. In this both bytes operation and word operations are possible. Thus one could write a program to add bytes or words.

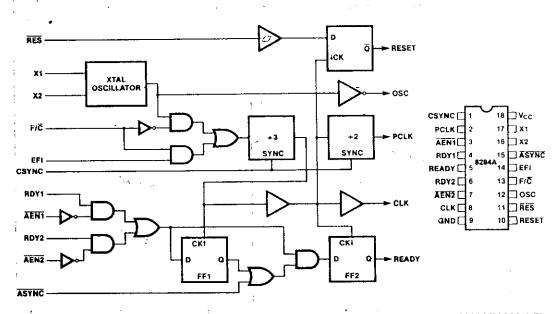

The clock signal for the basic 8088 chip is a 5 MHz derived via a divide by-three circuit used in the 8284 clock chip, from a standard 15MHz crystal connected to it. The simplest instruction of the 8088 takes about three clock cycles and mainly it depends on the type of operation performed.

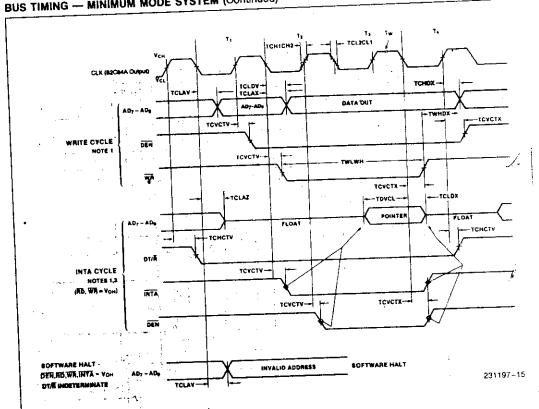

The circuit diagramof the system board is shown in 1182.1 The 8284 clock generator uses a 15 MHz crystal, divides it by three and generates the clock for the 8088. It also generates the RESET and READY signals, synchronised with the clock. A RESET switch is therefore connected to the 8284. The HOLD, TEST, NMI pins are tied through resistors to ground, since there is no need to use them now. Since we are used signal reception channel the INTR and INTA pins are brought to the edge connector, otherwise these two pins can tied through resistors to ground.

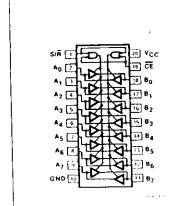

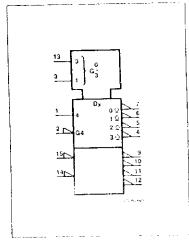

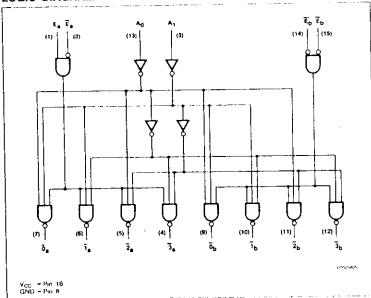

The ADO-AD7 multiplexed address-data lines are fed to the 74LS 374 whose output provides the  $A_0$ - $A_7$  low-order address lines. after demultiplexing them with the address-latch enable (ALE) pulse going to pin 11. The  $AD_0$ - $AD_7$  lines also go to the 74LS 245 buffer. The DEN and DT/R pin 26 and 27 respectively are connected to the enable and direction control pins of this bidirectional bus-buffer chip. This chip features a chip enable (CE) input for easy cascading and a send/Receive (S/R) input for direction control. Hence, the pins 11 to 18 of this chip provide the buffered data bus for use by the systems.

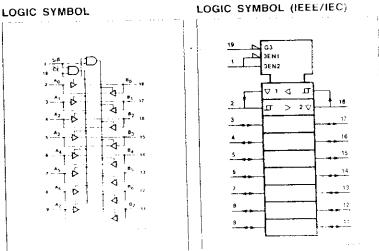

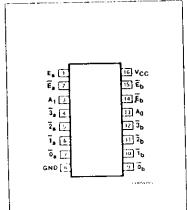

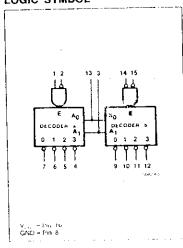

The address decoder 74 LS 155 chip is given the high order address lines A13, A14 and A15 as well as the memory enable signa. This chip is a dual 1-of-4 decoder with common address inputs and separate gated enable inputs. These 8 combinations are available from the output pins of the 74LS 155 decoder. The corresponding hexadecimal ranges are shown in fig1.1. Among the available ranges, the 8K block from E000 to FFFF is used for the selection of EPROM and the 8K block lying in the lowest memory range (0000 to 1FFF) is used for the selection of RAM. The remaining 8K memory blocks are used for addressing other peripheral chips which may be used. The unique feature of the system board is that these lines are brought out of the via the edge connector pins of the 8085 board so that these boards are interchangeable.

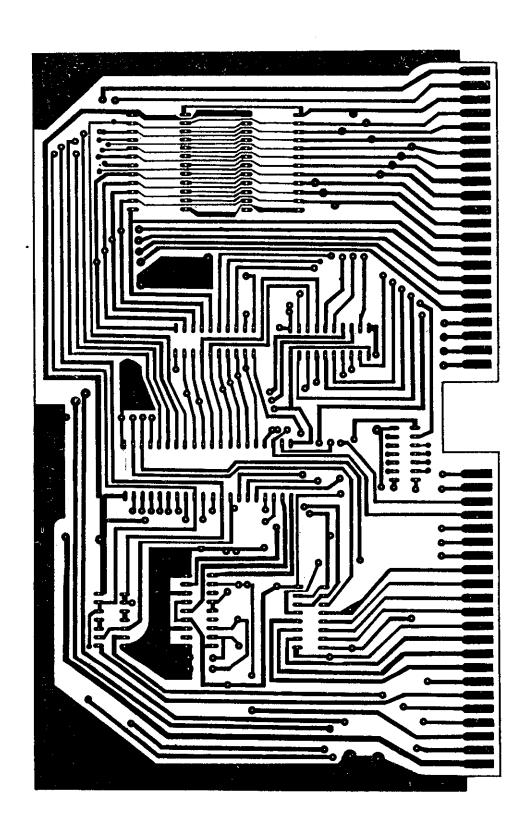

Fig: 1.1 CIRCUIT DIAGRAM

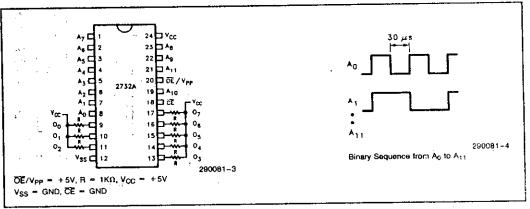

The address lines  $A_0$ - $A_7$  and  $A_8$ ,  $A_9$ ,  $A_{10}$ ,  $A_{11}$  go to the address pins of the 2732 EPROM. It is seen that the RD Signal goes to the output enable pin of the EPROM.

Address lines  $A_0$ - $A_7$ ,  $A_8$ ,  $A_9$ ,  $A_{10}$  go to the address-input pins of the RAM. As in the EPROM, the 8088 RD and WR signals go to its output enable and write enable pins.

The EPROM address is in high end of the memory since the 8088, upon RESET, causes the program to begin, fetching instructions from the address FFFO. Hence this address must be in the non-volatile memory or PROM. so that program execution of the monitor takes place as soon as power is applied and RS (reset) switch is pressed.

The RAM is kept in the lowest part of memory since the interrupt vectors are designed by the 8088 to access this space.

#### 1.2 System Processor:

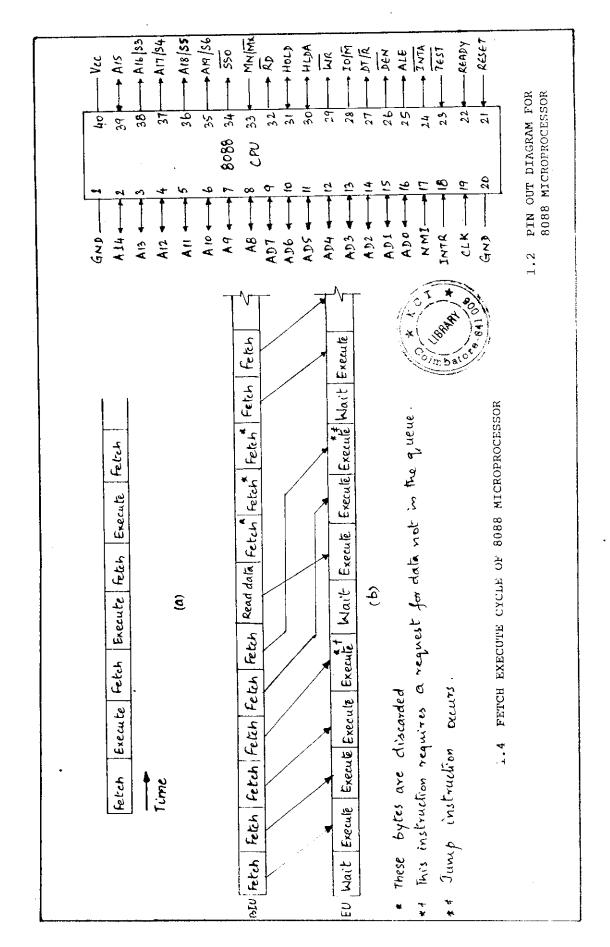

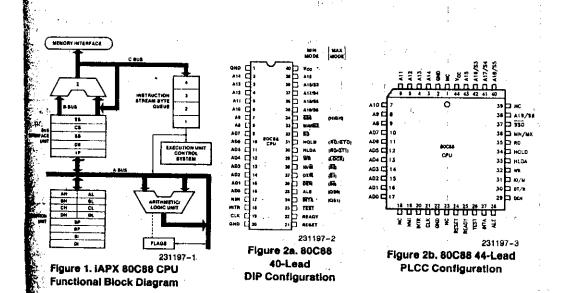

The heart of the system board is the INTEL 8088 microprocessor. This processor is eight bit extended version of INTEL 16-bit 8086 processor and is software compatible with 8086. The pin diagram of the 8088 is shown in fig. 1.2 Since the processor can access upto one megabyte of memory it needs four more address lines than the 8085. This processor contains the 8-bit data bus is named  $AD_0$  to  $AD_7$  and also these lines contain the address lines of low order i.e.  $A_0$  to  $A_7$  in a multiplexed manner.

The 8088 processor needs a clock generator chip separately. It needs just a single 5V power supply. For accessing input output ports and memory, the IO/M signal indicates that it the pin goes high an input-output operations occur and if it is low a memory read write operation takes place. The signal DT/R becomes necessary when bidirectional buffer is required, since data can either go in or out of the 8088 processor.

There are two possible interrupts, one the non-maskable interrupt NMI (pin 17) and the other the usual INTR Pin 18. The INTR Pin when takes high, interrupts the processor and an interrupt-acknowledge signal comes via pin 24 (INTA). The RESET and READY input signals are derived from the 8284 clock-chip because these inputs should he synchronised with the clock signal. There is another pin called the MN/MX, control pin. When this is tied to 5V, the processor works in its 'minimum system' hardware configurations. In the system

board we have caused only minimum mode. In the maximum mode, some of the pins perform a dual function with the help system controller chip 8288.

#### 1.2.1. THE 8088 MPU

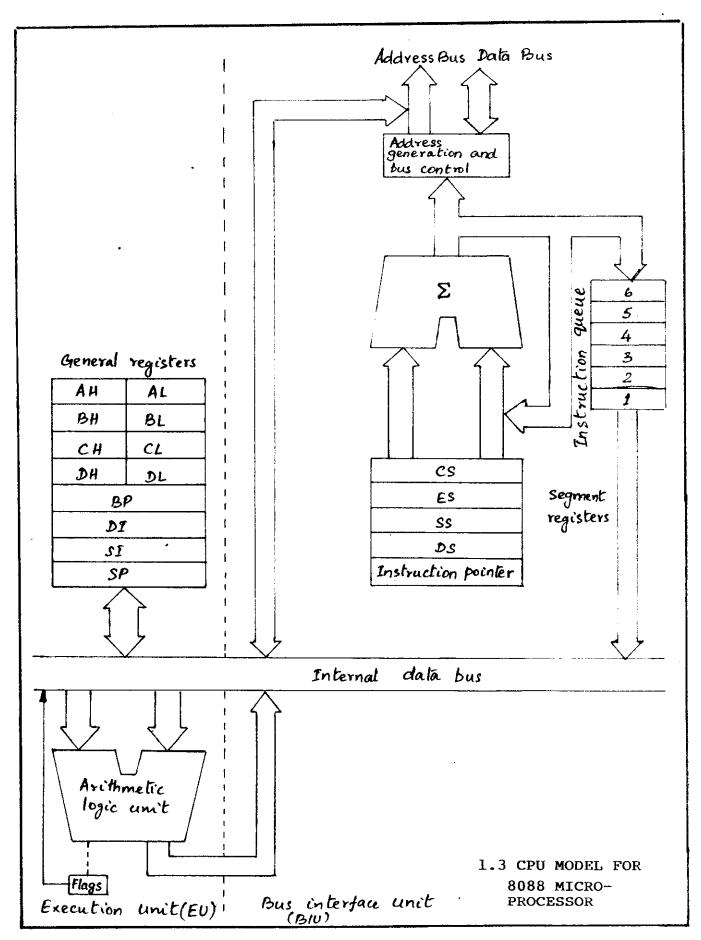

The 8088 microprocessor is actually just one IC chip in a family of 16-bit processors. The 8088 can read memory only 8 bits at a time. CPU Model for 8088 is shown fig.1:3.

#### The 8088 CPU Architecture

The study of microprocessors is broadly divided under:

- 1) The CPU Architecture, including the internal registers and flags and the instruction set i.e., the dictionary of program instructions. The Ap will recognize and execute.

- The electrical interface, including the data, address and control buses and the clock generation circuitry.

The Ap generates the timing signals and synchronizes the transfer of data between memory, I/O and itself. It accomplishes this task via the 3-bus system architecture.

The µp also has a software fn., It must recognize, decode and execute program instructions fatched from the memory unit. This requires an ALU within the CPU to perform arithmetic and logical functions.

It is organized as two separate processors, called the bus interface unit (BIU) and the execution unit (EU). The BIU provides hardware fns, including generation of the memory and I/O addresses for the transfer of bata between the outside world outside the CPU, that is and the EU.

The EU receives program instruction codes from the BIU, executes these instructions and stores the results in general registers By passing the data back to the BIU, data can also be stored ina memory location or written to an O/P device. The EU has no connections to the system buses, it receives and O/Ps all its data through the BIU. In the 8088, the BIU bus path is 8 bits wide. The 8088 instruction queue is four bytes long.

#### Fetch and Execute

- The BIU o/ps the contents of the instruction pointer register (IP) onto the address bus, causing the selected byte or word to be read into the BIU.

- 2) Register IP is incremented by 1 to prepare for the next instruction fetch.

- Once inside the BIU, the instruction is passed to the "queue".

This is a first-in, first-out storage register.

- 4) Assuming that the queue is initially empty, the EU immediately draws this instruction from the queue and begins execution.

5) While the EU is executing this instruction, the BIU proceeds to fetch a new instruction. Depending on the execution time of the first instruction, the BIU may fill the queue with several new instructions before the EU is ready to draw its next instruction.

The BIU is programmed to fetch a new instruction whenever the queue has room for one (with the 8088) additional byte. The advantage of this pipelined architecture is that the EU can execute instructions almost continually instead of having to wait for the BIU to fetch a new instruction. This is shown schematically in the 1191.4

There are 3 conditions that will cause the EU to enter a "wait mode". The first occurs when an instruction requires access to a memory location not in the queue. The BIU must suspend fetching instructions and output the address of this memory location. Afting waiting for the memory access, the EU can resume executing instruction codes from the queue.

The second condition occurs when the instruction to be executed is a "jump" instruction. In this cases control is to be transferred to a new address. The queue, however, assumes that instructions will always be executed in sequence and thus will be holding the "wrong" instruction codes. The EU must wait while the instruction at the jump address is fetched. Note that any bytes presently in the queue must be discarded.

One other condition can cause the BIU to suspend fetching instructions that are slow to execute. At four clock cycles per instruction fetch, the queue will be completely filled during the execution of this single instruction.

A subtle advantage to the pipelined architecture is that the BIU can access memory at a somewhat "leisurely" pace because the next serveral instructions usually in the queue.

#### 1.2.2 Segmented Memory

8088, being a 16-bit processor, reads memory at a rate of 8 instructions at a time. There are two main reasons for it to use an 8 bit memory. First it allows the processor to work on bytes as well as words. This is especially important with I/O devices such as printers, terminals which are designed to transfer 8 bit data generally. Second, many of the 8088 codes are single bytes. Other instructions may require anywhere from 2 to 7 bytes. By being able to access individual bytes, these edd lengthened instructions can be handled.

The memory of 8088 is segmented into small spaces each space possessing a byte in turn. If the memory consists of  $z^{10}$  bytes of different addresses then there has to be that much of segments. Moreover, 8088 with its 8-bit data bus interfaces to the 1 MB of memory as a single bank unlike the 8086 which goes on with 2 separate memory banks.

Memory map is an important aspect with 8088. It is nothing

but a guide like system, showing how the system memory is allocated. The blocks of memory are alloted is a proper way to ROM, RAM etc and the programme is intimated about that.

Within the 1 MB of mem. space, 8088 defines 4 major blocks called the code segment, stack segment, data segment, extra segment. Code segment holds the program instruction codes. Data segment stores data for the program. Stack separate stores interrupt and subroutine return addresses. Extra segment is an extra data segment and is often meant for shared data. The very concept of segmented memory is to provide more space for the user for processers.

An address within a segment is called an 'offset or logical address'. But logical address say 5H in a code segment (say BOOH) actually corresponds to the real address which is BOOH + 5H = BOO5H which is called as physical address. Physical address is 20 bits long and corresponds to the actual binary code O/P by the BH on the address bus lines whereas logical address is an offset from location 0 of a given segment.

The main aspect to be noticed with segmented memory is that the program opcodes will be fetched from the code segment, while program data variables will be stored in the data and extra segment. The advantage of having separate data and code segment is that one program can work on different sets of data. Perhaps the greatest advantage of segmented memory is that program that reference logical addresses only can be loaded and run anywhere in the memory.

#### 1.3 Memory devices:

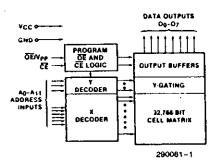

The system board designed uses on board permanent and volatice memory devices (2732 - Erasable programmable ROM and 6116 - RAM) respectively) and can hold system program upto 32 kilo bytes. A previously stored BIOS in the EPROM controls the system operations temporary operations performed in the system use the RAM locations and hence the time of accessing problems get minimised. The mapping of the chips are done considering them as extensions of the main memory inside the 8088 itself. The program sequence used for data reception from the ADC is stored in the EPROM and the received data stored in pre defined memory locations. The various stages of transfer taking place through registers in the 8088 and the RAM.

#### 1.3.1. 6116 RAM

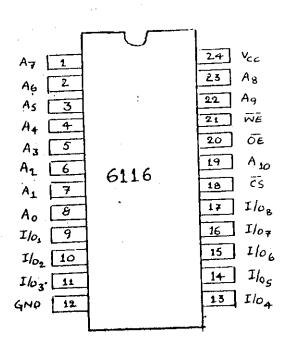

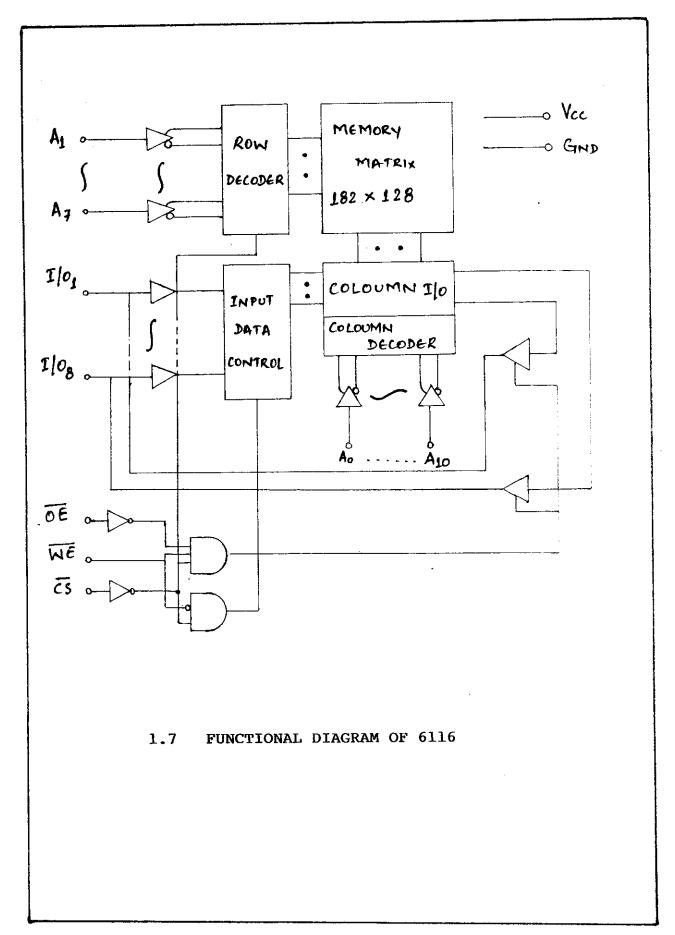

In this project we are using the 6116  $2K \times 8$  light speed CMOS RAM. The 6116 uses 16 K D Flip-Flops for its storage calls. These are organized in 2K groups of 8. The product of the number of unique locations and the number of memory cells at each location gives the total number storage devices in the memory IC.

Refer to fig1.5 By observing the number Of address inputs we can calculate the total number of unique storage locations. The pin out in fig1.6 indicates that the 6116 has address pins.  $2^{\rm m}$  =  $2^{\rm K}$  unique memory locations. Because the 6116 has eight 1/0 pims, there must be eight storage cells at each unique location. This agrees with the  $2^{\rm K}$  x 8 description Of the 6116.

### 1.6 PIN DIAGRAM OF 6116

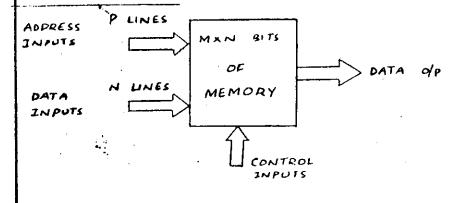

## 1.5 BLOCK DIAGRAM OF ANY MEMORY DEVICE

Refer to the functional block diagram 1.7 Notice the addinverter - like devices that the 11 address lines are driving. The inverter like drivers imply that both the true and inverted values of the address lines are applied to the row and column decode circuitry.

three-state drivers on the output. The only power requirements of the 6116 is +5V and ground. The last part of the functional diagram consists consists of the control bus inputs. Those are output enable (OE), write enable (WE) and chip select (CS). If the o/P of the top AND gate goes active high, the three state data outputs buffers are enabled. This AND gate control the memory read operation. Where as the active high output of the bottom AND gate controls the memory write operations. The read operation will occur when both the chip select and output enable inputs are active low. The write operation will occur when both the chip select and write enable inputs are active low.

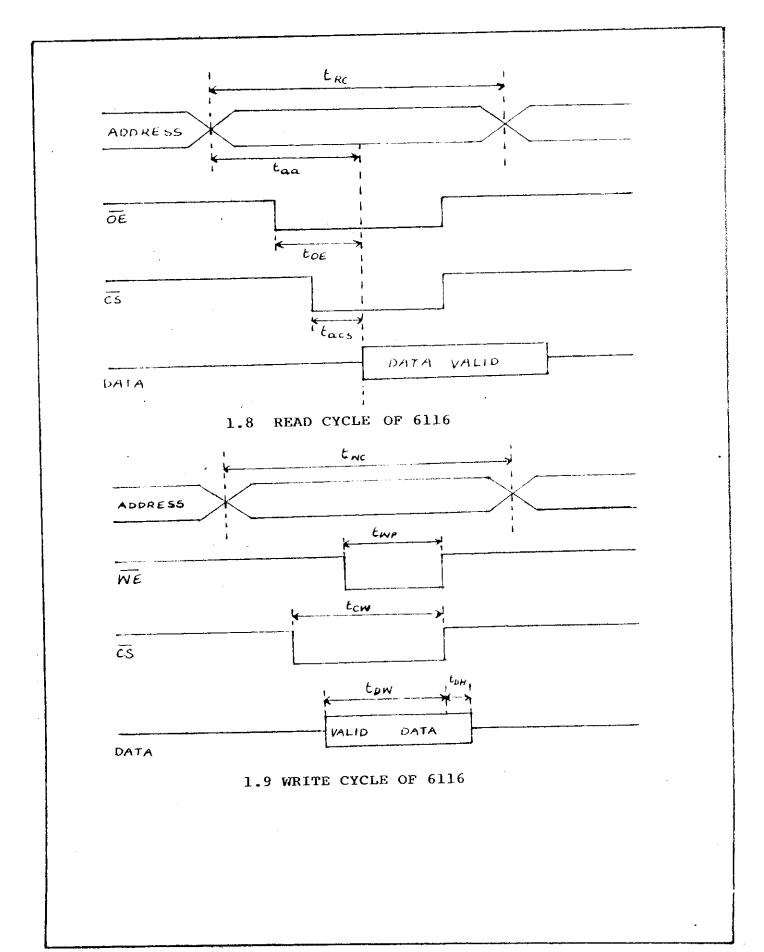

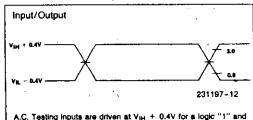

The microprocessor performing the read and write operation will have an 8 bit bidrectional data bus, 16 bit address bus, and a control bus with the active low signals memory request, write and read. The 6116 has different read access times (120, 150 and 200ns), so it in necessary to mention this specification with chip. The write cycle time is the write equivalent of the read cycle time. The WE signal is held at the inactive high level through out the read cycle. The processor will provide a 16 bit address denoting the memory loca-

tion to be read. Address bits  $A_0$  through  $A_{10}$  are directly connected to the 6116. Where as address bits  $A_0$  through  $A_{15}$  and MEMRQ will be used to create the chip select pulse. The output enable of the 6116 is driven by the RD of utput of the microprocessor. The typical read cycle shown in fig. 1.8 There are two possible ways to perform a 6116 write. The signal OE is held at an inactive logic 1 level. This will assure that the three state output buffers in the 6116 are never enabled when the microprocessor is outputting data or to the data bus. When the chip select goes active, the three state buffers will momentarily be enable until the write enable goes active. A typical (6116 memory write cycle is shown in fig.1.9

#### 1.3.2. EPROM

The EPROM is a type of ROM that can be erased and reprogrammed many times. The EPROM 2732 is used here in the system board. The 2732 has 4K bytes of programming sites on the metal oxide FETS. It is a 5V operating type.

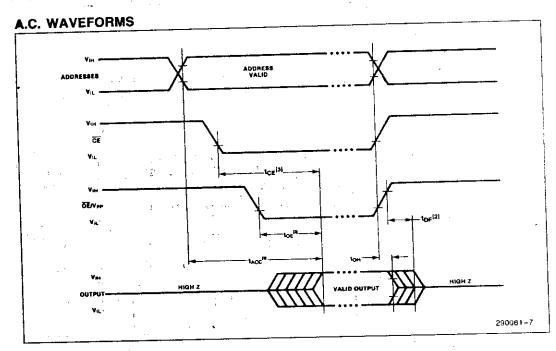

which takes the next address input A11, so that it has a 4K access. In this chip the pin 20 needs 25V for programming and a low signal (ground) for reading. One of the important features of this chip is that the otput enable (OE) is separate from the chip enable (CE) control. The OE control eliminates bus contention in microprocessor systems. The CE is used by the 2732 to place it in a stand by mode (CE= $V_4$ ) which reduces power consumption without increasing access time. The programming pulse applied to pin 18 is a negative going pulse of 50 ms. The pin out diagram is shown in appendix.

#### Erasure Characteristics

If a mistake occurs in the data programmed the whole EPROM should be erased and reprogrammed. The erasure characteristics are such that erasure begins to occur upon exposure to light with wavelength shorter than approximately 4000 A°. The recommended and standard erasure procedure is exposure to short wave ultraviolet light which has a wavelength of 2537 A°. In the center of an EPROM is a clear and round window. If this is exposed to UV (Ultraviolet) light.

the previously programmed information will be erased. The integrated dose for erasure should be a minimum of 15W sec/m². The erasure time with this dosage is 15 to 20 minutes using an UV lamp with a 1200 \(\mu\mathbf{w}\mu\scrime^2\) power rating. After each erasure, all bits of the EPROM are in the '1' state. Data is introduced by selectively programming '0' s into the bit locations. The only way to change a '0' to a '1' in cerdip EPROMS is by UV light erasure.

#### 1.4 System Clock

The circuit uses a clock frequency of 5 MHz, since the 8088 is a chip operating at 5 MHz. Each instruction utilizes at least three clock cycles and the maximum depends on the type of operation performed. We use a 15 MHz crystal in the clock generation circuitry. This used along with the 8284 oscillator circuitry provides a precise 5 MHz signal output with the chip having a divide by three facility.

#### 1.4.1. 8284 Clock Generator and Driver

The 8284 is a single chip clock generator which generates the system clock for the IAPX 88 microprocessor. The chip contains a crystal synchronization and reset logic. Refer to appendix for pin configuration. The oscillator circuit of the 8284 is designed with an external series resonant, fundamental mode, crystal from which the basic operating frequency is derived.

The crystal frequency should be selected at three times the required CPU clock,  $\mathbf{X}_1$  and  $\mathbf{X}_2$  are the two crystal input crystal connections. The clock generator consists of a synchronous divide by three counter with a special clear if input that inhibits the counting. The clock output is a 33% duty cycle mosclock driver designed to drive the IAPX 88 processor directly. The reset signal is synchronized to the falling edge of clk. The clock cycle period for this chip is about 125 ns.

## CHAPTER - 2

#### ADC INTERFACE

## 2.1. Signal reception and Analysis

Any Analysis operation on random signals can be done only by storing the received signal and observation. With the advent of digital systems a microprocessor based reception and analysis has become very common. This essentially consists in converting the signal in to digital equivalent and input to the microprocessor for processing.

The system can be expanded by using a multichannel input by a multiplexer cum sample and hold set up. The microprocessor giving the command for a particular channel to be selected and issuing command to the ADC module to convert the input signal into a digital code. The output inturn is read by the processor. The above steps are performed repeatedly.

The data is read in discrete intervals known as sampling. The sampling frequency is related to the signal frequency and should be atleast twice the maximum frequency of signal.

#### 2.2 Data Converters

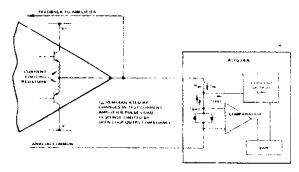

The analog signals from transducers are required to be digitised before entering into the processor. This necessitates the use of a converter. A typical Analog to digital converter converts an analog voltage to a digital output that best represents the input. The commonly employed technique for conversion is that the input signal is directly compared with a known reference signal.

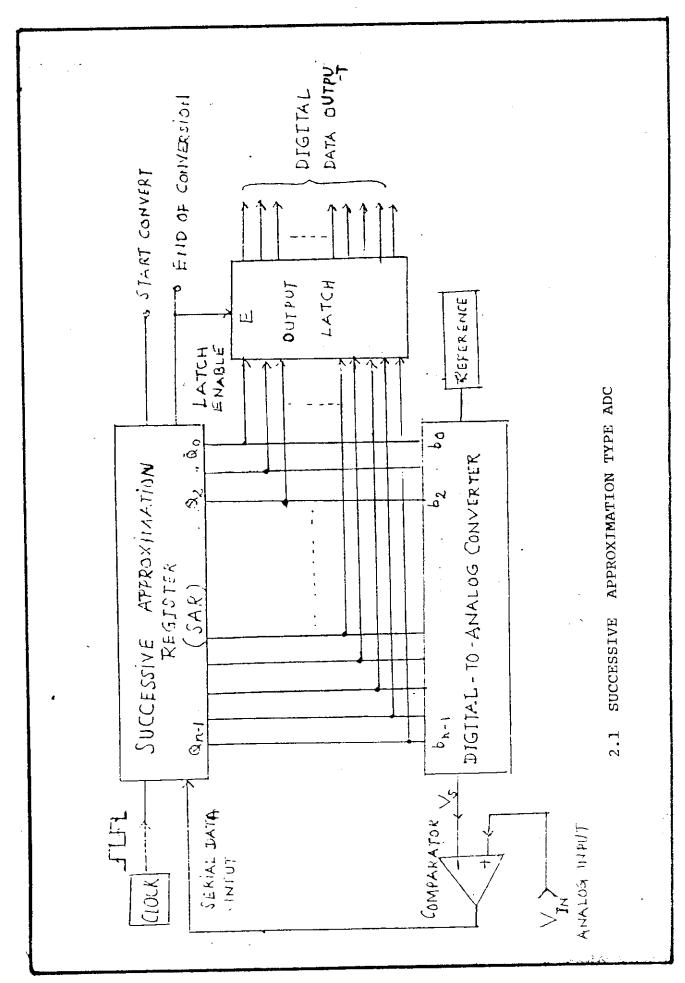

A successive approximation type of ADC is better equipped for processor interfaces than any other type of ADC's. A successive approximation A/D converter as in fig1.1 Consists of a D/A converter with a precision voltage reference comparator, successive approximation register, clock and output latch.

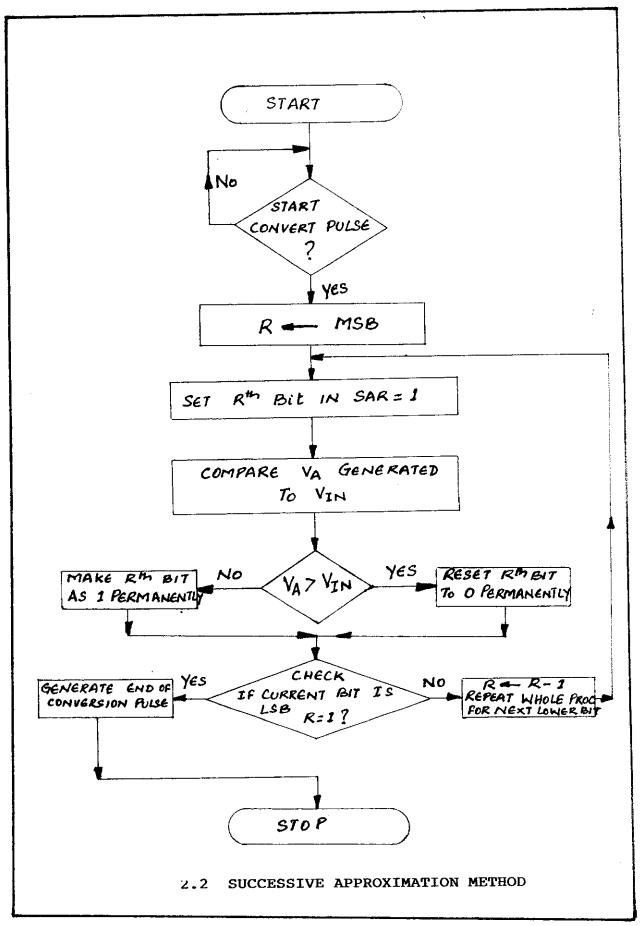

The conversion takes place by successive comparison and approximation of binary output between the input signal and the reference signal. The input signal should in no case exceed the refence. The number of steps of comparison and approximation in this type of ADC is equal to the number of bits in the digital output. The flow chart of conversion is shown in fig2.2 The advantage of SA ADC is its high speed and excellent resolution. The main factors involved are conversion speed, accuracy and cost. The SA ADC features high speed and the accuracy slightly decreases as the resolution increases.

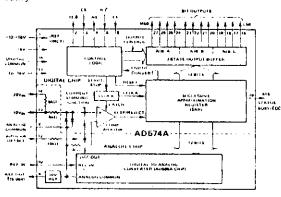

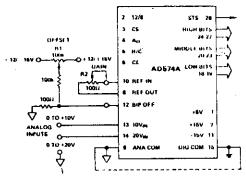

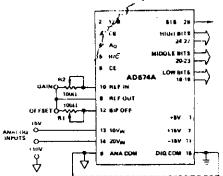

The AD574 is such a flexible and retiable converter having a very fast conversion rate, even faster than the process or itself that it can be used for receiving multichannel reception and continuously probing all the channels. The conversion is at such fast rate that the waveform——received from each channel will not be distorted for a typical 16 channel multiplexing i.e. the time between the 1st sample of 1st channel signal and its second sample i.e. after the 1st samples of all other 15 channels are taken is still well within sampling theorem requirements that the received data will be of such clarity as to enable brief——analysis of them.

#### AD 574 : CBIP ChS:

#### Interface Timing Adjustments:

The Chip has the following control signals whose signal requirements are to be precisely met for correct conversion.

- (i) the  $\overline{\text{CS}}$  signal which selects the card for conversion. This can be achieved by activating this by the address out of the 8088 (decoded)

- (ii) The CE signal enables the chip and it should be enabled before the  $\overline{\text{CS}}$  is done. This includes one less propagation delay and is a faster input.

- (iii) A R/ $\overline{C}$  signal which decides whether conversion process or data reading is going on. The signals RD and WR from the 8088 can be used to decide the process.

- (iv) A 12/8 pin which decides weather a 12 bit conversion, an 8 bit conversion or 12 bit conversion with 8 bit output is going on.

- (v) The pin  $A_0$  along with R/C determines 2 byte reading of 12 bit conversion. By connecting this to A0 of  $\mu$ P this can be achieved by reading from successive addresses.

- $$\left(\mathrm{vi}\right)$$  A STS signal which gives the E OC signal out and hence can be used to interrupt the processor.

All these signals need precise timing adjustments for perfect functioning and hence needs proper delays to be introduced and proper signals to be chosen for each and every pin. The operation of the ADC along with its turning diagrams are given in the appendix.

Such an interface along with a DAC and multichannel facility will serve as an excellent communication interface.

The circuit developed with all such facilities and proper printed circuit board layout was developed with theoretical analysis of the chip.

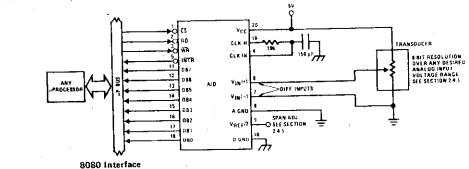

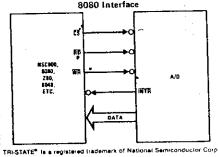

## 2.3 Microprocessor interface:

easily. The points to be considered in interfacing being a) the resolution (no.of bits) of the ADC is equal to the resolution of the processor data bus. b) the speed of operation and timings of the ADC coincide with the processor timings and speed. The operation can be a)synchronous: the processor executing the instruction for a time equal to the conversion time of the ADC b)Asynchronous: processor checking the part for End of conversion or c) in interrupt mode: The processor will then read the data from the ADC.

The throughput rate of an acquisition system is the number of samples/sec/channel, the system can handle. The above factor is important if one expands the system to a modified multichannel card with sample & hold circuitry.

The sequence of operation in a normal data receiving system are:

- a) Sending command to the part for start command operation, by selecting the chip and switching the input signal ON.

- b) The ADC goes into a conversion cycle. The address may be updated during conversion.

- c) After conversion the data can be read through the data lines.

- d) The above sequence is repeatedly executed for continuous data reception.

### 2.4 Why the microprocessor? - 8088

The Intel 8088 has the same Arithmetic Logic unit, the same registers and the same instruction set as 8086. The 8088 also has a 20 bit address bus, so that address as any one of the 1 Mb in memory. The 8088 has an 8 bit data bus so it can read or write 8 or 16 bits at a time. To read a 16-bit word from two successive memory locations, The 8088 will always have to do two read operations. The 8088 is more popular due to its simplified hardware while retaining the same power. The 8088 coupled with a numerical co-processor is capable of executing powerful floating point operations, many times faster than 8088 and is extremely useful in data processing. So, an ideal converter for an extremely fast processor is the AD574 which has a conversion time of 25 \mus. This is a 12 bit A/D converter which has a built in zener reference. This chip is capable of accepting bipolar voltage ranges. The advantage of this chip is that the 12 bits of output data can be as one 12-bit A/D converter which has a built in zener reference. This chip is capable of accepting bipolar voltage ranges. The advantage of this chip is that the 12 bits of output data can be read as one 12-bit word or as two 8-bit bytes (one with 8 data bits, the other with 4 data bits and 4 trailing zeros. This chip operates on the successive approximation principle.

The design of an interface, a typical data acquisition load using AD 574 is an asset in itself in any high frequency signal reception, like, for e.g. extraterrestrial signal by use of antenna elements.

#### 2.5 ADC Interface

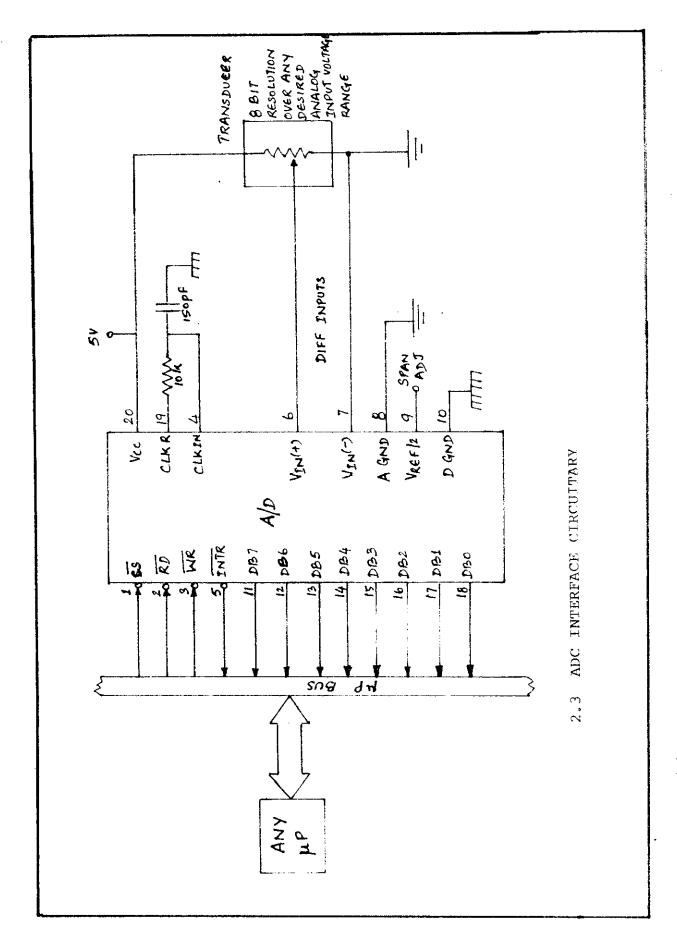

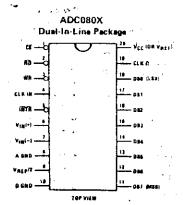

The converter used is a CMOS 8 bit successive approximation type. The operational characteristics and interface design of the 0804 chip with the microprocessor is discussed here. The chip uses a differential potentiometric ladder. The inbuilt output latches drive the data bus of the processor. These A/D s appear like memory locations or I/o ports to the processor and no interfacing logic is needed. A new differential voltage allows increasing the common mode rejection and offsetting the analog zero input. In addition the voltage reference input can be adjusted to allow encoding any smaller analog voltage span to the full 8 bits resolution.

The chip exhibits an on chip clock generator. This has an easy interfacing facility with all microprocessors or it operates stand alone. The interfacing schematic is shown in appendix The design part of the interface is just an enhanced form of the block shown with various signal and voltage level adjustment.

The various step taken to the above effect include:

1) The conversion of Analog signal to digital is initiated by a CSsignal output to the card and writing to the port the channel to be selected if multiplexing is done. Once the conversion cycle is started the processor will go into its usual routine. Address of the channel can be any one of the address for which 1YO gets activated.

- 2) The device will be interupted by the ADC after conversion so the end of conversion is given to the INTR of system board

- 3) The data will be read after interrupt so the IORD is connected to the o/p latch enable (RO) of the 0804.

- 4) The 2 inputs vin (-) and vin (+) are combined through a resistive devider to provide a constant range of input in both +ve and -ve direction. A multiplexer may be used at the vin (+) if many data channels need to be interfaced, but for simplicity the option is left open.

- 5) The clock inside the chip itself is used as clock in the design.

- 6) The reference voltage is maintained precisely at 2.5v by a Zener voltage adjust. The Zener adjust does the Vcc to V ref conversion 4 maintains the Vref.

- 7) The data outputs are connected directly to the system data bus and output the data when the RD pin of the system goes low or when the processor is ready to receive the data.

The whole circuitry employing the above features is shown in fig2.3 The circuit board for the same was designed in smart  $\epsilon$  tested. The software for data reception is listed in the software section.

The data receiving operation is explained in brief as below:

- 1) The processor initiates a conversion cycle.

- 2) The device interrupts the processor after the conversion terminates.

- 3) The processor reads the data from the  $\mbox{O/P}$  latches of the 'ADC.

- 4) The processor starts the next conversion cycle and the above sequence is repeated until sufficient signal samples are taken.

The data stored is analysed using software instructions and feedback actions taken.

### CHAPTER - 3

### INTERRUPTS IN 8088

The 8088 has seven different interrupt types:

3.1

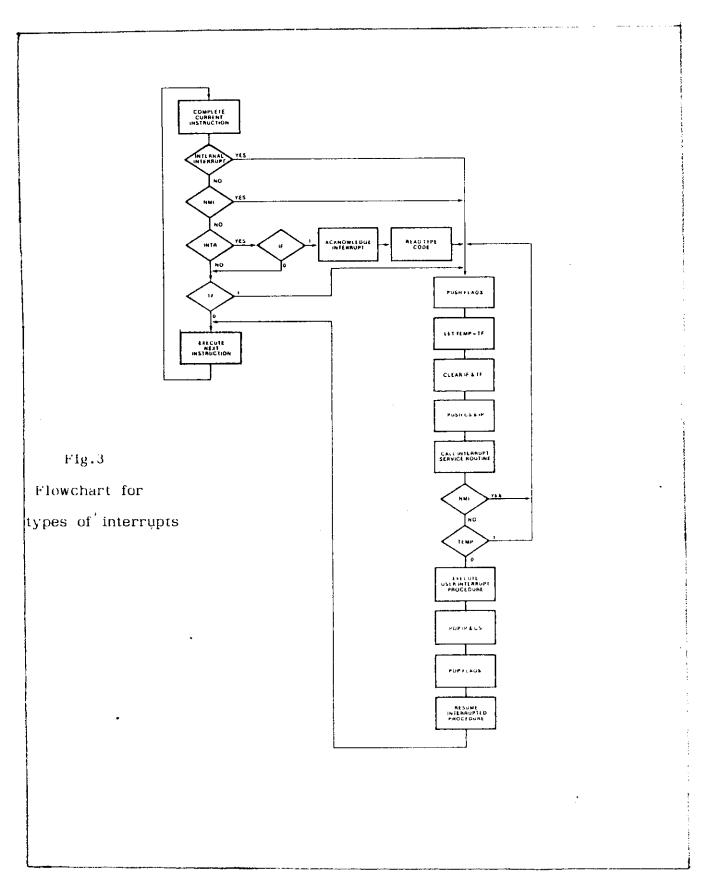

NMI, INTR, INTR, INTR, INTO, Divide-by-0, Single-step, INTR, INTO, and the special single-byte INT3 breakpoint instruction are software interrupts placed as desired within a program. The divide-by-0 and single step interrupts are initiated by the CPU: the former if the quotient produced by a divide instruction exceeds the capacity of the destination register and the latter at the completion f each instruction if TF is set. The flow chart of the 8088's response to each of these types of interrupts in fig3. In all cases the current instruction is allowed to finish before the interrupt is processed. Interrupt interrupts (except single-step) have precedence or priority over simultaneous (with the same instruction) external interrupt requests. For example, if an interrupt request occurs on INTR, but the current instruction causes a divide-by-zero interrupt, the later will be serviced first. Similarly if simultaneous interrupts occur on INTR and NMI, NMI will be serviced first.

When the interrupt is serviced, the flags, CS and IP registers are pushed on the stack, saving the CPU's "place" in the memory. This means that six bytes will be pushed onto the stack. The TF status is saved so that the interrupted instruction will still be single-stepped (if TF is set). However, before executing the ISR, TF and IF are cleared, disabling INTR and the single-step mechanism within

this routine. If desired, these flags can be set, enabling these interrupts. That is, the interrupts can be allowed to interrupt themselves.

If an internal interrupt is being serviced and an NMI (on INTR if IF is set) occurs, the ISR for the internal interrupt will be suspended and the external interrupt honored, even though it is of low priority. The priority structure applies to only simultaneous interrupt requests.

NMI is a non maskable interrupt which means that it cannot be blocked. INTR, on the other hand, is maskable via the IF flag. Only when this flag is set will interrupts on this live be accepted. Although internal interrupts have priority over external interrupts, the NMI I request will be honoured as the internal interrupt's ISR begins. This is not true for the INTR input however. This is because IF is cleared automatically when the internal interrupt is serviced.

As the NMI interrupt is non maskable, the NMI interrupt is reserved for catastrophic events such as memory error or an impending power failure.

The INT instruction causes the program to jump indirectly to the memory pointed by a vector in 00 to 03 pages. The INT instruction pushes on the stack the PC, CS and flags. An IRET instruction in the interrupt service routine will restore these, after returning from such an interrupt.

The pages 00 to 03, totally 1024 bytes, can contain 256 vector addresses (4 bytes/vector; bytes for jump addresss; 2 bytes for code segment). Thus 256 software interrupts are permissible.

However, some of the interrupt vectors are reserved for certain functions. For example, the first vector which is at  $00\ 00$  has:

| 00 00 | Low address and | of interrupt service routine for |

|-------|-----------------|----------------------------------|

| 00 01 | High address    | overflow upon divisin (divide    |

| 00 02 | Low part        | by 0) of code segment in         |

| 00 03 | High part       | which you might have written     |

|       |                 | a routine to be executed when    |

|       |                 | DIV by 0 occurs.                 |

Thus, the first software interrupt is reserved for taking suitable action whenever a divide-by-zero occurs. Hence, it is called a type-0 interrupt. It automatically occurs upon divisionally by zero.

| 04 00 | MOV AX FF 10              | B8 FF 10 | Move AX with the value      |

|-------|---------------------------|----------|-----------------------------|

|       |                           |          | 10 FF (some number).        |

| 04 03 | MOV CL <sub>1</sub> 00    | B1 00    | Make the divisor purposely  |

|       |                           |          | a zero.                     |

| 04 05 | DIV CL                    | F6 F1    | Divide by CL (a zero)       |

| 04 07 | MOV LABEL <sub>1</sub> AX | A3 00 05 | Move quotient and remainder |

|       |                           |          | in 05 00 and 05 01.         |

04 0A HLT F4

Also load the interrupt service routine (ISR) to take necessary action upon a division by zero occurring.

| 00 | D0 00 | 00         |       | Start address of division.         |

|----|-------|------------|-------|------------------------------------|

| 00 | 01    | 06         |       | by-zero interrupt service routine. |

| 00 | 02    | 00         |       | Code segment value is 00 00        |

| 00 | 03    | 00         |       |                                    |

| 06 | 00    | MOV AL, EE | BO EE | Move a flag EE in AL               |

| 06 | 02    | OUT AL, 04 | E6 04 | Output the error flag on port-4    |

| 06 | 04    | IRET       | CF    | Program returns.                   |

Upon executing the division program at 04 00, the output in port-4 is EE, indicating that division by zero was attempted. No division is really performed.

# 3.1.1 Type-1 Interrupt (single step mode):

Type-1 software interrupt vector which is stored in 00-04 to 00-07 (program counter and code segment values as before) is to have an interrupt routine which enables debugging a program ins-

truction by instruction. This interrupt is maskable and will work only if the TF bit in the flag register is set. So, in order to do single stepping of instructions, one has to set the IF flag, write an interrupt service routine for debugging and load the addresses 00 04 to 00 07 with the address code segment values of this routine. For example,

| 04 00 | PUSH F     | 9C       | Push the flags on the stack                                                     |

|-------|------------|----------|---------------------------------------------------------------------------------|

| 04 01 | POP AX     | 58       | Move the flags into AH & AL                                                     |

| 04 02 | OR AH, 01  | 80 CC 01 | Set the 8th bit (0th bit in AH) to 1. This is for setting TF flag subsequently. |

| 04 05 | PUSH AX    | 50       | Push this altered flag value on stack.                                          |

| 04 06 | POP F      | 9D       | Get the TF-set flags on to the flag register.                                   |

| 04 07 | MOV AL, 02 | во 02    | Here after the program which is to be single-stepped follows: Let AL = 02       |

| 04 09 | P: INC AL  | FE CO    | Increment AL                                                                    |

| 04 0B | JMP P      | EB FC    | Jump to Loop.                                                                   |

After entering the above program, the interrupt vector as well as the service routine for single step are loaded (at  $06\ 00$ ).

| 00 04 00  |               |          |                              |

|-----------|---------------|----------|------------------------------|

| 00 05 00° |               |          |                              |

| 00 06 00  |               |          |                              |

| 00 07 00  |               |          |                              |

| 06 00     | OUT AL 04     | E6 04    | Output AL on port-4.         |

| 06 02     | POP 00 05     | 8F 06 00 | Pop the stack to get at      |

|           |               |          | the previous prog. ctr.      |

|           |               |          | value at some memory say     |

|           |               |          | 05 00.                       |

|           |               |          |                              |

| 06 06     | PUSH 00 05    | FF 36 00 | Push it back again in place. |

|           |               | 05       |                              |

|           |               |          | DIVOY AV                     |

| 06 0A     | PUSH AX       | 50       | PUSH AX                      |

| 06 OB     | PUSH BX       | 53       | Push BX                      |

| 00 52     |               |          |                              |

| 06 OC     | MOV BX, 00 05 | 8B 1E 00 | Move the contents of 05 00   |

|           |               | 05       | 05 00 (the previous prog.    |

|           |               |          | ctr.) into BX.               |

|           |               |          | So that the monitor software |

|           |               |          | display can show it.         |

|           |               |          | 1 0                          |

| 06 10     | CALL KBD      | 9A 80 F2 | Call monitor display prog.   |

|           | •             | 00 00    |                              |

|           |               | 43       |                              |

| 06 15 | POP BX | 58 | Restore register sel   |

|-------|--------|----|------------------------|

| 06 16 | POP AX | 58 |                        |

| 06 17 | IRET   | CF | Return from interrupt. |

The program is executed at 04 00 as usual. The program advances step by step after reaching 04 09 address and the key board can be pressed (any her key) to step it. In this program, it jumps between the addresses 04 09, 04 0B (because it has a loop there).

### 3.1.2. Type-2-interrupt

The type-2 is a non-maskable interrupt which is got by a low to high pulse on NMI pin. It vectors to the address 08 on page 0.

### CHAPTER - 4

### SOFTWARE LISTINGS

### 4.1 Monitor Program and the use of the 8088 board developed.

The monitor program which is listed is written and developed on similar lines of the 8085 monitor. Upon RESET, the 8088 sets its CS register to FFFF and hence the program memory should be at the highest end of the one megabyte memory. As seen, we have left the addresses  $A_{16} - A_{19}$  addresses, the first F in the CS register is a 'don't care' digit for us. Hence, the EPROM (2732) is selected at FF FFO and thus the first jump instruction is placed at the last (Fth) page of the EPROM at FO. This is an intersegment jump which jumps to F500, i.e. to the 5th page of the 2732. The CS register is simultaneously made 00 00. Thus, all further program has identical values for CS, DS, ES, SS all of which are 00 00. The values of the segment register, not necessarily have only the values 00 00. They can be chosen and redefined by the user himself. The user memory RAM occupies the first 2K space (0000-07FF).

# 4.1.1 Sample Programs to illustrate the 8088 instructions.

# a) Program to find the average of a number of bytes

| Address |                   | Code     | Comments                                              |

|---------|-------------------|----------|-------------------------------------------------------|

| 0400    | MOV S1, 0005      | BE 00 05 | SI points to 05 00 where the numbers are stored.      |

| 0403    | MOV Cx, 0B 00     | B9 0B 00 | Cx stored with the number; (OB) bytes to be averaged. |

| 0406    | PUSH CX           | 51       | Save CX register                                      |

| 0407    | TOP: ADD AL, (SI) | 02 04    | Add the first number with AL                          |

| 0409    | ADC AH, 00        | 80 D4 00 | And then ADD carry into AH                            |

| 040C    | INC SI            | 46       | Increment SI to get the next number.                  |

| 040D    | LOOP              | E2 F8    | Decrement CX and return to loop top if non-zero.      |

| 04 OF   | POP CX            | 59       | Restore original CX value.                            |

0410 DIVCL F6 F1 Divide AX by CL

0412 OUT AL, 04 E6 04 Output the averaged number of port 4.

The numbers to be averaged are stored in  $0500\ \mathrm{onwards}$ .

### Address

05 00 01 02 03 04 05 06 07 08 08 08 09 0A 0B

**Result:** The number 66 is the average.

### (a) BINARY MULTIPLICATION

| Address        | Mnemonics          | Code           | Comments                   |

|----------------|--------------------|----------------|----------------------------|

| 0400           | MOV AL, 08         | B0 08          | Multiplicand - 08 is inAl. |

| 0402           | MOV CL, 05         | B1 05          | Multiplier - 35 is in      |

|                |                    |                | CL.                        |

| 0404           | MUL CL             | F6 E1          | Multiply AL by CL contents |

| 0406           | MOV 05 00,         | AX A3 00 05    | Store result in 0500       |

| 0409           | нст                | F4             |                            |

| After executir | ng the program, 05 | 00 contains 28 | 3. 0501 contains 00.       |

### (:) DIVISION

Binary division (byte division)

| 0400 .        | MOV AX, FF 00 | B8 FF 00 | Dividend 00 FF is          |

|---------------|---------------|----------|----------------------------|

|               |               |          | in AX.                     |

| 0403          | MOV CL, 10    | B1 10    | Divisor in CL register     |

| 0405          | DIV CL        | F6 F1    | Now AX is divided          |

|               |               |          | by CL                      |

| 0407          | MOV 05 00, AX | A3 00 05 | Move AX into 0500,<br>0501 |

| 0 <b>4</b> 0A | HLT           | F4       | Halt                       |

The result will be FF/10, which gives a quotient of  $\mathrm{OF}$  and a remainder of OF. For division the quotient is in AL, remainder in AH.

### d) STRING TRANSFER INSTRUCTION

# 1) Transfer one page of FF bytes.

| 0400 | MOV SI, | 05 00 | BE 00 05 | SI register points to |

|------|---------|-------|----------|-----------------------|

|      |         |       |          | source area 05 00     |

| 0403 | MOV DI, | 06 00 | BF 00 06 | DI register points to |

|      |         |       |          | destination area.     |

| 0406  | MOV CX,      | 00 FF - B9 FF | 00 CS is | stored with the     |

|-------|--------------|---------------|----------|---------------------|

|       |              |               | number   | FF (a page)         |

| 0409  | CLD          | FC            | Clear    | direction for       |

|       |              |               | auto ii  | ncrement in string  |

|       |              |               | instruc  | tion which follows. |

| 040A  | Pt.P: MOVS B | A4            | Moves    | the contents        |

| •     |              |               | of the   | e SI pointer to     |

|       |              |               | DI.      |                     |

| 04013 | LOOP P       | EZ FI         | ) Develo | pment CX, return    |

|       |              |               | to top   | of loop if not      |

|       |              |               | zero.    |                     |

| •     |              |               |          |                     |

| 04 OD | HLT F4       | F4            | Halt     |                     |

The contents of 05 page in RAM would have got transferred into 06 page after this program is run.

# String transfer and test while transfering:

| 0400 | CLD          | FC       | Clear     | the   | direction |

|------|--------------|----------|-----------|-------|-----------|

| •    |              |          | flag.     |       |           |

| 0401 | MOV SI, 0006 | BE 00 06 | SI points | s to  | a source  |

|      |              |          | string at | 06 00 | )         |

| 0404    | MOV DI, 0005  | BF 00 05 | DI Pts to 05 00, the  |

|---------|---------------|----------|-----------------------|

|         |               |          | place where it is to  |

|         |               |          | be stored.            |

| 0407    | MOV CX, FF 00 | B9 FF 00 | CS is stored with the |

|         | •             |          | code FF.              |

| 040A P: | LODB          | AC       | The contents of SI    |

| •       |               |          | area got into AL.     |

| 040B    | STOB          | AA       | Then moved into DI    |

|         |               |          | area.                 |

| 040C    | TEST AL, FF   | A8 FF    | Test if Al = FF.      |

| 040E    | LOOP NE, P    | E2 FA    | Loop until AL finds   |

|         |               |          | the code FF.          |

| 0410    | НСТ           | F4       | Halt                  |

The program will duplicate the contents of 06 page into 05, until senses an FF in the former. In string transfer the destination index points to the extra segment memory. But, in the monitor program developed, all the segment registers are made 0000 and hence access within the same memory block.

### 4.2. ADC Program

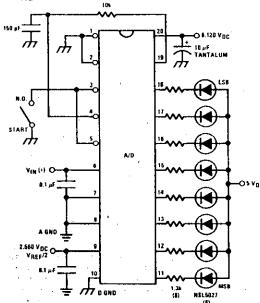

This program illustrates that it accepts the 8-bit output from an Analog to Digital converter and scales it to a value between OV & 5V. The output is displayed on two seven segment displays as a units digit and a tenths digit.

| = |      | DPORT | EQU | H | ; Data in port,   |

|---|------|-------|-----|---|-------------------|

| = |      | DSPY  | EQU | H | ; Display port    |

| = | 0005 | MPLR  | EQU | 5 | ; Full scaie = 5V |

One byte of uninitalised storage is reqd. TEMP is defined in a segment called DATA.

| 0000    | DATA | SEGMENT |   |   |      |       |

|---------|------|---------|---|---|------|-------|

| 0000 ?? | ТЕМР | DB      | ? | ; | Unde | fined |

| 0001    | DATA | ENDS    |   |   |      |       |

The program codes are stored in a segment called CODE.

The Assume statement tells the assembler to use CODE for CS and DATA for DS. The SS and ES segment registers are not defined.

0000 CODE SEGMENT

ASSUME CS: CODE, DS-DATA

The operating system loads CS at run time but not DS. The next two instructions load DS with the DATA segment base address.

0000 B8 ---- R START: MOV AX, DATA; Segment base

MOV DS, AX; to DS

0003 8E D8

Get data from ADC & Form value between OV & 5V

0005 E4 D6 AGAIN : IN AL, DPORT ; GET Data

0007 B3 05 MOV BL, MPLR; Multiply times

0009 F6 E3 MUL BL ; full scale

000B BA 0000 MOV DX, 0 ; Divide 32 bit

; Dividend in

: DX : AX

000E BB 0100 MOV BX, 256; by 256 for an

0011 F7 F3 DIV BX ; 8 bit ADC

Shift quotient four bits left so it will appear in the left most display.

0013 B1 04 MOV CL, 4 ; 4 shifts left

0015 D2 E0 SAL AL, CL ;

0017 A2 0000R MOV TEMP, AL; Save units digit

Fetch remainder and calculate tenths digit.

001A BA C2 MOV AL, OL ; Reminder to A1

001C B3 OA MOV BL, 10 ; Multiplier

001E F6 E3 MUL BL ;

0020 BA 0000 MOV DX, 0 ; Do division

0023 BB 0100 MGV BX, 256; for the

0026 F7 F3 DIV BX ; tenths digit

Check remainder, round tenths digit up & output result to the displays.

0028 80 FA 80 CMP DL, 128; Less than

002D FE CO INC AL ; No

002F 27 DAA ; Keep decimal

0030 02 06 0000R SKIP: ADD AL, TEMP; form result

0033 E6 D4 OUT DSPY, AL; and show it

0035 EB CE JMP AGAIN ; Repeat cycle

0037 CODE ENDS

END START

The flow chart for the ADC conversion is shown. The units digit is called X and the tenths digit is called Y. After inputting the digital word, the units digit is calculated using the formula as shown above.

We require a 16-bit divisor to divide the data by 256 and thus a 32-bit dividend in registers DX:AX.

The multiplication and division instructions can be performed on (a) 8-or (b) 16 bit register or memory source operates specific registers are dedicated to these functions as shown.

After the division X will be a number between 0 § 4. At this point Y represents the remainder of the division and could be any number between 0 § 255.

Because the units digit must appear in the left most display, it is shifted left four places (or multiplied by 16). The remainder is then multiplied by 10 and divided by 256 to calculate the tenths digit. If the remainder from this division is greater than 127, one is added to Y to round up one-tenth.

Finally, adding X and Y assembles the two-digit result and it can be output to the displays. The process is then repeated.

The assembly language listing for the program is also shown. The EQU statements are used to give names to constants & port addresses. After a value for X has been calculated, the result is temporarily stored until the tenths digit has been calculated. One byte in a (data) segment called DATA is used for this purpose. This segment is bracketed between the DATA SEGMENT and DATAENDS segment. All the segments must have an opening & closing statement like this or the assembler will issue an error message.

ASSUME CS: CODE, DS: DATA Statement tells the assembler what to assume for the segment registers as it assembles the following instructions. This statment does not load the registers. The assume is required so that the assembler will know if it needs to generate far or near calls and jumps. It is also required to determine if a segment override is required.

The operating system will pick a value for CS based on available memory. The remaining segment registers must be loaded by the user.

The MOV AX, DATA instruction will cause the assembler to reserve two bytes of the MOV op-code for the segment address. Normally, this move instruction would load the contents of memory location DATA to AX. In this case, however, because DATA identifies a segment statement, the segment address is used. This can be seen in the left most column: B8....R. The R means that this address is relative and cannot be determined at this time. When the program is linked and loaded, the actual segment address will be placed in these two bytes.

When the program is run, the data segment address will be loaded into AX and the next instruction will transfer this value to DS. The remainder of the program follows the flow chart.

| Address |               | Hex. | Code       | <b>:</b> |    |    |         | Mnemonics               |

|---------|---------------|------|------------|----------|----|----|---------|-------------------------|

| ні      | LOW           |      |            |          |    |    |         |                         |

| FF      | F0            | EA   | 99         | F5       | 00 | 00 |         | JMP, BRANCH,<br>SEGMENT |

| F5      | 00            | BC · | FF         | 07       |    |    |         | MOV SP, DATA 16         |

| F5      | 03            | ВВ   | 00         | 04       |    |    |         | MOV BX, 00 04           |

| F5      | 06            | 8A   | 2 <b>F</b> |          |    |    | Scan. 2 | MOV CH, (BX)            |

| F5      | 08            | 9A   | 80         | F2       | 00 | 00 | Scan. 1 | CALL KBD                |

| F5      | 0D            | 3C   | 40         |          |    |    |         | CMP AL, 40              |

| F5      | $0\mathbf{F}$ | 73   | 80         |          |    |    |         | JNB To Pt. D            |

| F5      | 11            | В1   | 04         |          |    |    |         | MOV CL, 04              |

| F5      | 13            | D2   | E5         |          |    |    |         | SAL CH, N               |

| F5      | 17            | EB   | EF         |          |    |    |         | JMP TO SCAN 1           |

| F5      | 19            | 3C   | <b>4</b> 2 |          |    |    | Pt. D   | CMP AL, 42              |

| F5      | 18            | 75   | 04         |          |    |    |         | JNZ To Pt. E            |

| F5      | 1D            | 8A   | DD         |          |    |    |         | MOV BL, CH              |

| F5      | IF            | EB   | E5         |          |    |    | -       | JMP To SCAN 2           |

| F5      | 21            | 3C   | 41         |          |    |    | Pt. E   | CMP AL, 41              |

| F5      | 23            | 75   | 04         |          |    |    |         | JNZ To Pt. F            |

| F5      | 25            | 8A   | FD         |          |    |    |         | MOV BH, CH              |

| F5      | 27            | EB   | DD         |          |    |    |         | JMP To Scan 2           |

| F5      | 29            | 3C   | 44         |          |    |    | Pt. F   | CMP AL, 44              |

| F5      | 2B            | 75   | 03         |          |    |    |         | JNZ Pt. P               |

| F5      | 2D            | 4B   |            |          |    |    |         | DEC BX                  |

| F5      | 2E            | EB   | D6         |          |    |    |         | JMP To Scan. 2          |

| F5  | 30 | 3C | 47         |    | Pt. | P | CMP AL,47       |

|-----|----|----|------------|----|-----|---|-----------------|

| F5  | 32 | 75 | 05         |    |     |   | JNZ Pt. G       |

| F5  | 34 | 88 | 2 <b>F</b> |    |     |   | MOV (BX), CH    |

| F5  | 36 | 43 |            |    |     |   | INC BX          |

| F-5 | 37 | EB | CC         |    |     |   | JMP To Scan. 2  |

| F5  | 39 | 3C | 43         |    | Pt. | G | CMP AL, 43      |

| F5  | 3B | 75 | C8         |    |     |   | JMP To Scan. 2  |

| F5  | 3D | A1 | 00         | F6 |     |   | MOV AX, 00 F6   |

| F5  | 40 | E7 | 01         |    |     |   | OUT AX, PORT-01 |

| F5  | 42 | FF | ЕЗ         |    |     |   | JMP BX          |

# SOFTWARE DISPLAY ROUTINE:

| F2  | 00 | 51 |    |    | PUSH CS           |

|-----|----|----|----|----|-------------------|

| F2  | 01 | 9C |    |    | PUSH F            |

| F2  | 02 | 8A | C7 |    | MOV AL, BE        |

| F2  | 04 | 24 | F0 |    | AND AL, FO        |

| F2  | 06 | В1 | 04 |    | MOV CL, 04        |

| F2  | 08 | D2 | C8 |    | ROR AL, N         |

| ·F2 | 0A | 8A | DO | •  | MOV DL, AL        |

| F2  | 0C | вΰ | 7F |    | MOV AL, 7F        |

| F2  | 0E | E6 | 01 |    | OUT AL, 01        |

| F2  | 10 | E8 | 4D | 00 | CALL seg. display |

|     |    |    |    |    | (F2 60)           |

| F2  | 13 | 8A | С7 |    | MOV AL, BH        |

| F2  | 15 | 24 | 0F |    | AND AL, OF        |

|                                        |                                              |                                                           | MOV DI Al                                                                               |

|----------------------------------------|----------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|

| F2                                     | 17                                           | 8A D0                                                     | MOV DL, AL                                                                              |

| F2                                     | 19                                           | BO BF                                                     | MOV AL, BF                                                                              |

| F2                                     | 1B                                           | E6 01                                                     | OUT AL, 01                                                                              |

| F2                                     | 1D                                           | E8 40 00                                                  | CALL seg. display                                                                       |

| F2                                     | 20                                           | 8A C3                                                     | MOV AL, BL                                                                              |

| F2                                     | 22                                           | 24 FO                                                     | AND AL, FO                                                                              |

| F2                                     | 24                                           | B1 O4                                                     | MOV CL,O4                                                                               |

| F2                                     | 26                                           | B2 C8                                                     | ROR AL,N                                                                                |

| F2                                     | 28                                           | 8A DO                                                     | MOV DL AL                                                                               |

| F2                                     | 2 <b>A</b>                                   | BO EF                                                     | MOV AL, EF                                                                              |

| F2                                     | 2C                                           | E6 O1                                                     | OUT A01                                                                                 |

| F2                                     | 2E                                           | E8 2F 00                                                  | CALL SEG. DISPLALY                                                                      |

|                                        |                                              |                                                           |                                                                                         |

| F2                                     | 31                                           | 8A C3                                                     | MOV AL,BL                                                                               |

| F2<br>F2                               | 31<br>33                                     | 8A C3<br>24 OF                                            | MOV AL,BL<br>AND AL,OF                                                                  |

|                                        |                                              |                                                           |                                                                                         |

| F2                                     | 33                                           | 24 OF                                                     | AND AL,OF                                                                               |

| F2<br>F2                               | 33<br>35                                     | 24 OF<br>8A DO                                            | AND AL,OF MOV DL,AL                                                                     |

| F2<br>F2<br>F2                         | 33<br>35<br>37                               | 24 OF<br>8A DO<br>BO F7                                   | AND AL,OF  MOV DL,AL  MOV AL,F7                                                         |

| F2<br>F2<br>F2                         | 33<br>35<br>37<br>39                         | 24 OF<br>8A DO<br>BO F7<br>E6 O1                          | AND AL,OF  MOV DL,AL  MOV AL,F7  OUT AL,O1                                              |

| F2<br>F2<br>F2<br>F2                   | 33<br>35<br>37<br>39<br>3B                   | 24 OF<br>8A DO<br>BO F7<br>E6 O1<br>E8 22 OO              | AND AL,OF  MOV DL,AL  MOV AL,F7  OUT AL,O1  CALL SEG. DISPLAY                           |

| F2<br>F2<br>F2<br>F2<br>F2             | 33<br>35<br>37<br>39<br>3B<br>3E             | 24 OF  8A DO  BO F7  E6 O1  E8 22 OO  8A C5               | AND AL,OF  MOV DL,AL  MOV AL,F7  OUT AL,O1  CALL SEG. DISPLAY  MOV AL,CH                |

| F2<br>F2<br>F2<br>F2<br>F2<br>F2       | 33<br>35<br>37<br>39<br>3B<br>3E<br>40       | 24 OF  8A DO  BO F7  E6 O1  E8 22 OO  8A C5  24 FO        | AND AL,OF MOV DL,AL MOV AL,F7 OUT AL,O1 CALL SEG. DISPLAY MOV AL,CH AND AL FO           |

| F2<br>F2<br>F2<br>F2<br>F2<br>F2<br>F2 | 33<br>35<br>37<br>39<br>3B<br>3E<br>40<br>42 | 24 OF  8A DO  BO F7  E6 O1  E8 22 OO  8A C5  24 FO  B1 O4 | AND AL,OF MOV DL,AL MOV AL,F7 OUT AL,O1 CALL SEG. DISPLAY MOV AL,CH AND AL FO MOV EL,O4 |

| F2         | 4.\ | E6 01    | OUT AL, 01          |

|------------|-----|----------|---------------------|

| F2         | 4C  | E8 11 00 | CALL seg. display   |

| F2         | 4F  | 8A C5    | MOV AL, CH          |

| F2         | 51  | 24 OF    | AND AL, CF          |

| F2         | 53  | 8A D0    | MOV DL, AL          |

| F2         | 55  | BO FE    | MOVAL, FE           |

| F2         | 57  | E6 01    | OUT AL, 01          |

| F2         | 59  | E8 04 00 | CALL seg. display   |

| F2         | 5C  | 9D       | POPF                |

| F2         | 5D  | 59       | POPCX               |

| <b>F</b> 2 | 5E  | СВ       | RET (inter-segment) |

## SEGMENT DISPLAY ROUTINE:

| F2         | 60 | B6 | F2            |        | MOV DH, F2          |

|------------|----|----|---------------|--------|---------------------|

| F2         | 62 | В0 | F0            |        | MOVAL, FO           |

| F2         | 64 | 0A | D0            |        | OR DL, AL           |

| F2         | 66 | 8B | F2 MOV S1. DX |        | MOV S1, DX          |

| F2         | 68 | 8A | 04            | •      | MOVAL, (S1)         |

| F2         | 6A | E6 | 02            |        | OUT AL, 02          |

| F2         | 6A | E6 | 02            |        | OUT AL, 02          |

| F2         | 6C | ВА | 3F 00         |        | MOV DX, 3F 00       |

| F2         | 6F | 4A |               | Pt. P; | DEC DX              |

| <b>F</b> 2 | 70 | 75 | FD            |        | JNZ disp 8 to. pt P |

| F2 | 72 | В0         | 00 | MOV | AL, 00        |        |

|----|----|------------|----|-----|---------------|--------|

| F2 | 74 | E6         | 02 | OUT | AL,02         |        |

| F2 | 76 | <b>C</b> 3 |    | RET | (displacement | based) |

# KEYBOARD SUBROUTINE;

| F2 | 80 | E4 | 02    |    |    | KBD:IN AL,O2             |

|----|----|----|-------|----|----|--------------------------|

| F2 | 82 | 0A | CO    |    |    | ORAL,AL                  |

| F2 | 84 | 78 | FA    |    |    | JS disp 8 to KBD         |

| F2 | 86 | E8 | 36 00 |    |    | CALL lime display (F2BF) |

| F2 | 89 | E4 | 02    |    |    | LOOP1:IN AL,02           |

| F2 | 88 | 0A | CO    |    |    | OR AL, AL                |

| F2 | 8D | 9A | 00 F2 | 00 | 00 | CALL software display    |

| F2 | 92 | 79 | F1    |    |    | JNS TO LOOP 1            |

| F2 | 94 | E8 | 28 00 |    |    | CALL TIME DELAY          |

| F2 | 97 | E4 | 02    |    |    | IN AL 02                 |

| F2 | 99 | OA | C0    |    |    | OR AL,AL                 |

| F2 | 9B | 79 | EC    |    |    | JNS,TO LOOP 1            |

| F2 | 9D | 34 | CO    |    | ·  | XOR AL,CO                |

| F2 | 9F | 24 | 4F    |    |    | AND AL,4F                |

| F2 | A1 | СВ |       |    |    | RET(inter-segment)       |

### TIME DELAY ROUTINE;

| F2 | BF | 50 |    |    | PUSHAX                   |

|----|----|----|----|----|--------------------------|

| F2 | CO | 9C |    |    | PUSHF                    |

| F2 | C1 | В8 | FF | 09 | MOV AX,FF 09             |

| F2 | C4 | 48 |    |    | PtA:DEC AX               |

| F2 | C5 | 75 | FD |    | JNZ TO PT.A (disp 8)     |

| F2 | C7 | 9D |    |    | POPF                     |

| F2 | С8 | 58 |    |    | POP AX                   |

| F2 | С9 | C3 |    |    | RET (displacement based) |

# LOOK UP TABLE FOR SEGMENTS;

| F2 | F0 | 7E   | 0 |

|----|----|------|---|

| F2 | F1 | OC . | 1 |

| F2 | F2 | В6   | 2 |

| F2 | F3 | 9E   | 3 |

| F2 | F4 | CC   | 4 |

| F2 | F5 | DA . | 5 |

| F2 | F6 | FA   | 6 |

| F2 | F7 | 0E   | 7 |

| F2 | F8 | FE   | 8 |

| F2 | F9 | CE   | 9 |

| F2 | FA | EE   | A |

| F2 | FB | F8 | В |

|----|----|----|---|

| F2 | FC | 72 | С |

| F2 | FD | BC | D |

| F2 | FE | F6 | Ε |

| F2 | FF | E2 | F |

### CHAPTER - 5

#### **APPLICATIONS**

### 5.1 APPLICATIONS

The discussions made earlier was on the implementation of the system logic and control software for signal reception. The signal itself is from some sensors and transducers which will constantly monitor the process variables of a physical system.

The above type of card can be used in a number of applications like measurement of physical variables for eg, temperature of ovens can be measured using a temperature sensor.

Pressure of small capacity boilers by use of a pressure sensor.

Motor speed, rotor position, displacement etc., can also be measured.

The system board itself can be used as a mini-processor system with proper keyboard and display connections. The PCB layout for the system board itself is done in such a way that it can go directly into a 8085 system ie. the 8085 main board can be replaced by this. The 8088 processor kit as such can be used to analyse a lot of software details including analog signal analysis, as in this case.

### 5.2. Scope for improvement:

The developed system can be improved to a microprocessor based data acquisition system which controls the physical variables of mechanical systems.

Such a facility can be extended by

- 1) including a keyboard and display interface for the main board.

- 2) A two way data card having a) A DAC b) A multiplexer for multichannel system c) A sample hold circuitry for updating of channels during conversion.

If all the above facilities are incorporated the system can be made to operate as a real time high precision control system.

### 5.3 Advantages

The development of a digital processor oriented data analyser provides a convenient, flexible and cost effective control of production in a factory. This lessons errors and decreases the time factor in the problems of machinery. This board with added facilities will be more helpful as an analyser of data since it uses a highly flexible microprocessor with auxilliary memory facility. The ADC add on card developed provides an added dimension in that if provides facility for real time monitoring and analysis of performance of physical systems.

### CHAPTER - 6

### **FABRICATION**

The circuits were designed as per procedure elaborated in the previous sections were tested individually and later fabricated.

The printed circuit board was made professionally in a copper clad hylam circuit board.

The necessary components for the boards were purchased. The components were soldered properly on the board. The monitor program in software sec. for the same is recorded in the EPROM with a Z-80 EPROM recorder.

## CHAPTER - 7

#### CONCLUSION

The system board developed is designed so that it can directly replace the 8085 system boards. With the simple board and using the same I/O board cum hex keyboard, the powerful microprocessor instruction set can be practised for various application. The sample programs illustrated in the previous sections can be demonstrated by replacing the 8085 board with the 8088 system board developed.

The system board along with the signal receiver card can be used for control applications for monitoring parameters in industrial applications, where speed and accuracy are the key specifications.

### **BIBLIOGRAPHY**