# Digital Phase Meter

# **Project Work**

SUBMITTED BY P-12-84

#### Binov Vithayathil

- T. Rajeev Kumar Ramdas

- A. Ravichandra Reddy

Under the Guidance of

Mr. K. Ramprakash, M.E.

In partial fulfilment of the requirements for the award of the degree of

BACHELOR OF ENGINEERING

in Electronics and Communication Engineering

Bepartment of Electronics and Communication Engineering Kumaraguru College of Technology

> Loimbatore - 641 006 1991 - '92

# Department of Electronics and Communication Engineering Kumaraguru College of Technology

Loimbatore - 641 006

# **CERTIFICATE**

This is to Certify that the project entitled

Digital Phase Meter

has been Submitted by

Mr. Binoy Vithayathil, T. Rajcev Kumar Ramdus, A. Ravichandra Roddy.

In partial fulfilment of the requirements for the award of the degree of

## BACHELOR OF ENGINEERING

in Electronics and Communication Engineering

Branch of the Bharathiar University, Coimbatore-641 006

During the academic year 1991 - '92

| Wohn Drolland.                                          | War Zorner                         |

|---------------------------------------------------------|------------------------------------|

| Guide                                                   | Head of the Dept.                  |

| Certified that the Candidate was  Viva-Voce Examination | examined by us in the Project—work |

| and the University Register                             |                                    |

| Internal Examiner                                       | External Examiner                  |

#### CONTENTS

| Chapter No. |                                  | Page No. |

|-------------|----------------------------------|----------|

| 1.          | OVERVIEW                         | 1        |

| 2.          | PHASE DETECTION TECHNIQUES       | 4        |

| 3.          | HARDWARE DESCRIPTION             | 18       |

| 4.          | DIGITAL MEASURING SECTION        | 38       |

| 5.          | DESCRIPTION OF THE CIRCUIT       | 53       |

| 6.          | CIRCUIT CONSTRUCTION             | 61       |

| 7.          | CALIBRATION AND USE              | 63       |

| 8.          | POWER SUPPLY OF THE SYSTEM       | 65       |

| 9.          | PRINTED CIRCUIT BOARD DESIGN     | 68       |

| 10.         | CONCLUSION                       | 72       |

| 11.         | BIBLIOGRAPHY                     | 73       |

|             | APPENDICES                       | 74       |

|             | APPENDIX - A : CMOS FEATURES     | • .      |

|             | APPENDIX - B : PCB LAYOUT        |          |

|             | APPENDIX - C . IC SPECIFICATIONS |          |

#### **OVERVIEW**

the rare instruments. Even in meters are Phase audio and Hi-fi Engineers and enthusiasts laboratory of these instruments are difficult to be found. Perhaps that is because until the advent of reliable digital techniques fairly difficult to design an accurate direct reading phasemeter. In the 1970's the phasemeters had an accuracy of 3 degrees from 10 Hz to 30 KHz. Clearly for modern audio equipment, that is no longer acceptable. Another reason may be that a phasemeter is a fairly specialized instrument. Many engineers and technicians measure phase shift with the aid of Lissaqious figures which does not give very accurate results either.

The phase meter presented in this project is accurate to within 0.5 degrees over frequency range 10 Hz to 20 KHz.

#### 1.1. What is Phase?

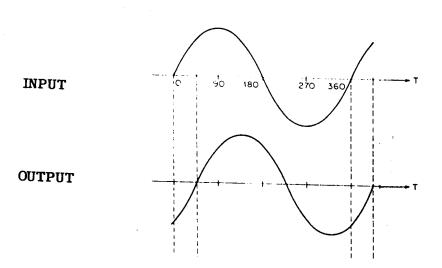

When a sinusoidal signal is input to a device, It arrives at the output of the device only after a certain time period. This delay is defined as the phase difference between two signals. This delay between input and output may be expressed as a proportion of the sine wave cycle, usually in degrees, one cycle is 360°, one half cycle is 180° etc.

So the phase difference between two signals will vary from  $0-360^{\circ}$ .

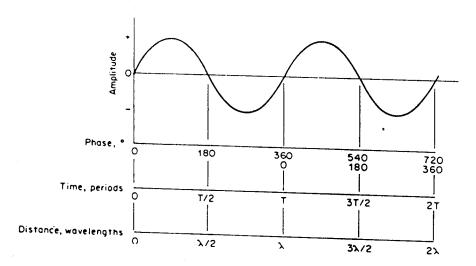

Phase is a notation in which the time of one period of a sine wave is divided into  $360^{\circ}$ . It is a relative quantity, and although it can be defined with respect to any reference point in a cycle, it is convenient to start  $(0^{\circ})$  with the upward, or positive going, zero crossing and to end  $(360^{\circ})$  at precisely the same point at the beginning of the next cycle. (Fig. 1.1). Phase shift expresses in degrees the fraction of a period or wavelength by which a single frequency component is shifted in the time doman. For example a phase shift of  $90^{\circ}$  corresponds to a shift of 1.4th period. For different frequencies this translates into different time shifts.

In the fig (1.2) shown the output signal lags in phase with respect to the input signal and the input signal leads in phase with respect to the output signal.

FIG. 1.1

RELATIONSHIP BETWEEN THE PERIOD (T) AND WAVELENGTH OF A SINUSOIDAL WAVEFORM AND PHASE EXPRESSED IN DEGREES.

FIG. 1.2

PHASE SHIFT BETWEEN INPUT AND OUTPUT SIGNAL

2.1 MEASUREMENT OF PHASE (Lissagious Patterns)

2.2 METHODS OF PHASE MEASUREMENT

#### PHASE DETECTION TECHNIQUES

#### 2.1. MEASUREMENT OF PHASE (LISSAGIOUS PATTERNS)

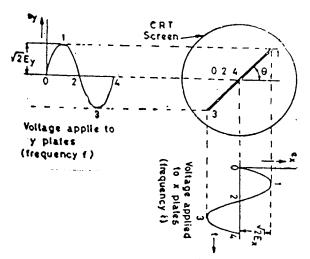

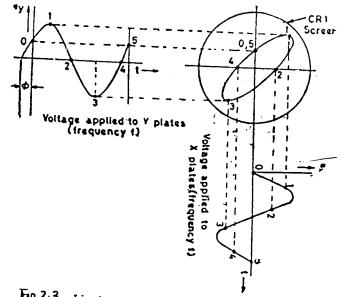

It is interesting to consider the characteristics of patterns that appear on the screen of the CRT when sinusoidal voltages are simultaneously applied to horizontal and vertical plates. These patterns are called Lissagious patterns.

When two sinusoidal voltages of equal frequency which are in phase with each other are applied to the horizontal and vertical deflection plates, the pattern appearing on screen is a straight line as clear from Fig.2.1. When two equal voltages of equal frequency but with 90° phase displacement are applied to a CRO, the trace on the screen is a circle. This is shown in Fig.2.2.

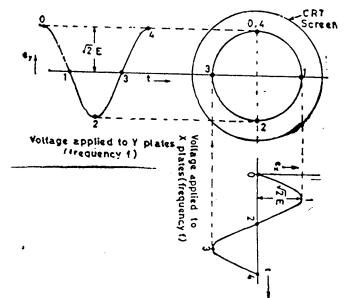

When two equal voltages of equal frequency but with a phase shift ( $0^{\circ}$  or  $90^{\circ}$ ) are applied to a CRO we obtain an ellipse (Fig.2.3). An ellipse is also obtained when unequal voltages of same frequency are applied to the CRO.

A number of conclusion can be drawn from the above discussions. When two sinusoidal voltages of the same

Fig 2.1 Lissajous pattern with equal frequency voltages and zero phase shift.

Fig 2.2 Lissajous pattern with equal voltages of equal frequency and a phase shift of 90°.

frequency are applied.

- (i). A straight line results when the two voltages are equal and are in phase with each other or  $180^{\circ}$  out of phase with each other. The angle formed with the horizontal is  $45^{\circ}$ , when the magnitudes of the voltages are equal. An increase in the vertical deflection voltage causes the line to have an angle greater than  $45^{\circ}$  with the horizontal. On the other hand a greater horizontal deflection voltage makes the angle less than  $45^{\circ}$  with the horizontal.

- (ii). Two sinusoidal waveforms of the same frequency produce a lissagious pattern which may be a straight line, a circle or an ellipse depending upon the phase and magnitude of the voltages. A circle can be formed only when the magnitude of the two signals are equal and the phase difference between them is either 90° or 270°. However if the two voltages are not equal and are out of phase an ellipse is formed. If the Y voltage is larger, an ellipse with vertical major axis is formed while if the X plate voltage has a greater magnitude, the major axis of the ellipse lies along horizontal axis.

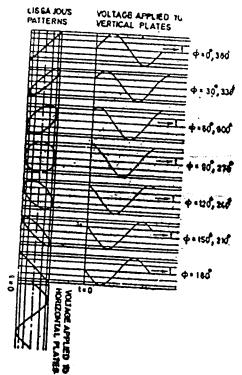

- (iii). It is clear from Fig.2.4 that for equal voltages of same frequency, progressive variation of phase voltage causes the pattern to vary from a straight diagnoal line to ellipse of different eccentricities and then to a

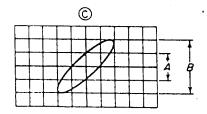

Fig 2.3 Lissajous pattern with two equal voltages of same frequency and phase shift of  $\phi$ .

Fig 2.4 Lissajous patterns with different phase shifts.

circle, after that through another series of ellipses and finally a diagonal straight line again.

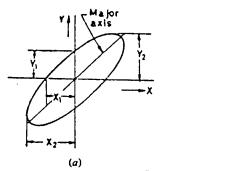

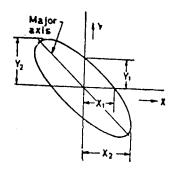

Regardless of the two amplitudes of the applied voltages the ellipse provides a simple means of finding phase difference between two voltages. Referring to Fig.2.5, the sine of the phase angle between the voltages is given by

Sin

$$\beta = \frac{Y_1}{Y_2} = \frac{X_1}{X_2}$$

For convenience the gain of the vertical and horizontal amplifiers are adjusted so that the ellipse fits exactly to a square marked by the lines on the graticule.

If the major axis of the ellipse lies on the first and third guadrants (ie. slope is positive) as in Fig.2.5. (a). the phase angle is either between  $0^{\circ}$  and  $90^{\circ}$  or between  $270^{\circ}$  to  $360^{\circ}$ . When the major axis of ellipse lies in the second and fourth guadrants, ie., when its slope is negative as in Fig.2.5. (b), the phase angle is between  $90^{\circ}$  and  $180^{\circ}$  or between  $180^{\circ}$  and  $270^{\circ}$ .

## 2.2. METHODS OF PHASE MEASUREMENTS

There are two methods that are widely used for measuring the phase difference between two given signals. They are,

- i. Dual Trace Method

- ii. X Y Method

Determination of angle of phase shift.

FIG. 2.5

#### 2.2.1. Dual Trace Method

The dual trace method of phase measurement provides a high degree of accuracy at all frequencies, but it is especially useful at frequencies above 100 KHz, where phase measurement may provide inaccurate readings owing to inherant internal phase shift.

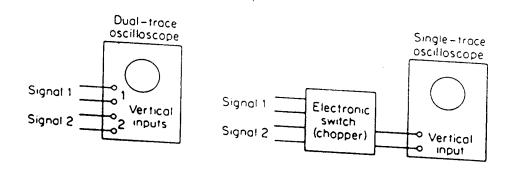

The dual trace method also has the advantage of measuring phase difference of signals with different amplitudes, frequency and waveshape. The method can be applied directly to those oscilloscopes having a built in dual trace feature, or to a conventional single trace oscilloscope using an electronic switch or "chopper". Either way the procedure consists essentially of displaying both traces on the oscilloscope screen simultaneously, measuring the distance (in scale divisions) between related points on the two traces, and then converting the distance into phase.

- 1. Connect the equipment as shown in Fig. 2.6.

- 2. Place the oscilloscope in operation.

- 3. Set the step attenuators to deflection factor that will allow the expected signal to be displayed without overdriving the amplifiers.

- 4. Switch on the oscilloscope internal recurrent sweep.

Fig. 2.6 Measuring phase difference with dual traces.

- 5. Set the position controls (horizontal and vertical) to spread the patterns over as much of the screen as desired.

- 6. Switch on the dual trace function of the oscilloscope or switch on the electronic chopper.

- 7. Adjust the sweep controls until one cycle of the reference signal occupies exactly 9 divisions of the screen.

- 8. Determine the phase factor of the reference signal.

- 9 . Measure the horizontal difference between corresponding points on the waveform. Multiply the measured distance (in centimeters) by  $40^{\circ}$  (phase factor) to obtain the exact amount of phase difference:

- 10. If the oscilloscope is provided with a sweep magnification control where the sweep rate is increased by a fixed amount and only a portion of one cycle can be displayed, more accurate phase measurements can be made. In this case, the phase factor is determined as in Step-9. Then the approximate phase difference is determined as described in step -10. Without changing any other controls, the sweep rate is increased (by the sweep magnification control or the sweep rate control) and a new horizontal distance measurement is made, as shown in Fig. 2.6. (b).

Note: Either of the two signals can be used as the reference signal, unless otherwise specified by the requirements of the particular test. It is usually simpler if the signal of the lowest frequency is used as the reference signal.

#### Disadvantage

For more accurate results, the cables connecting the two signals to the oscilloscope input should be of the same length and characteristics. At higher frequencies a difference in cable length or characteristics could introduce a phase shift.

#### 2.2.2. X - Y Method

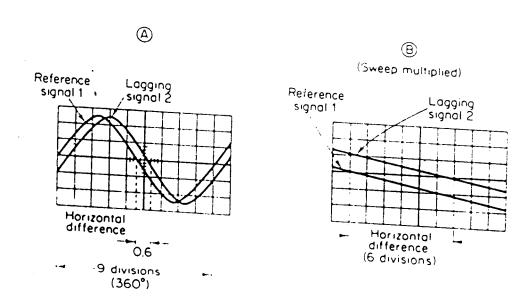

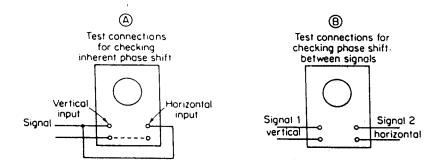

The X - Y phase measurement method can be used to measure the phase difference between two sine wave signals of the same frequency. This method provides a method of measurement for signal frequencies upto about 100 KHz, more precise than the dual trace method. Above this frequency however the inherant phase difference between the horizontal and vertical systems make accurate phase measurement difficult. Therefore, the X-Y method should be limited to phase measurement of lower frequency signals and to signals of the same frequency.

In the X - Y method, one of the sine wave signals provide horizontal deflection (X), and the other provides the vertical deflection (Y). The phase angle between the two signals can be determined from the resulting lissagious pattern.

- 1. Connect the equipment as shown in Fig. 2.7.(a).

- 2. Place the oscilloscope in operation.

- 3. Set the step attenuators to deflection factors that will allow the expected signal to be displayed without overdriving the amplifiers.

- 4. Switch off the oscilloscope internal recurrent sweep.

- 5. Set the gain controls (horizontal and vertical) to spread the patterns over as much of the screen as desired.

- of. Set the position control (horizontal and vertical) until the pattern is centered on the screen. Center the display in relation to the vertical graticule line.

Measure distance A and B as shown in Fig.2.7.(c). A is the vertical measurement between the two points where the trace crosses the vertical centerline. Distance B is the maximum vertical height of the display.

- 7. Divide A by B to obtain the phase angle between the two signals. The angle can then be obtained by taking the inverse sine of this value.

- 8. Once the inherant phase shift has been determined, connect the equipment as shown in Fig.2.7.(b). Repeat steps 3 through 7 to find the phase angle between the two signals.

- 9. Substract the inherent phase difference from the phase angle to determine the true phase difference.

#### Note:

Figure 2.7.(a) shows the test condition necessary determine the inherent phase shift (if any) between the horizontal and vertical deflection systems of the oscilloscopes. Even the most expensive laboratory identical vertical oscilloscopes with and horizontal amplifiers will have some inherant phase shift, particularly at the high frequencies. Therefore all frequencies should be checked and the inherent phase shift recorded before any phase measurements are made. If there is excessive phase shift (in relation to anticipated phase shift) the oscilloscope should not be used. A possible exception exists when the signals to be measured are of sufficient amplitude to be applied directly to the oscilloscopic deflection plates, and thus bypass the horizontal vertical amplifiers.

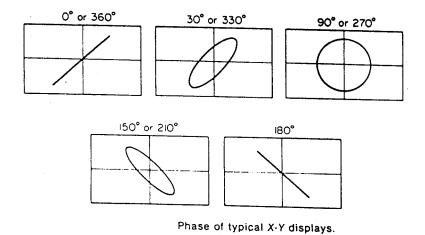

If the display appears as a diagonal straight line, the two amplifiers are either in phase (tilted upper right to lower left) or  $180^{\circ}$  out of phase (tilted upper left to lower

Measuring phase difference with X-Y method.

FIG. 2.7

FIG. 2.8

right). If the display is a circle, the signals are 90° out of phase. Fig.2.8 shows Lissagious displays produced between 0° and 360°. Notice that above 180° phase shift, the resultant diaplay, will be the same as at some lower frequency. Therefore it may be difficult to tell whether the signal is leading or lagging. One way to determine correct phase (leading or logging) is to introduce a small, known phase shift to one of the inputs. The proper angle may then be determined by noting the direction in which the pattern changes.

- 3.1 BLOCK DIAGRAM OF THE SYSTEM

- 3.2 BUFFER SECTION

- 3.3 ZERO CROSSING DETECTOR

- 3.4 BISTABLE MULTIVIBRATOR

- 3.5 MONOSTABLE MULTIVIBRATOR

#### HARDWARE DESCRIPTION

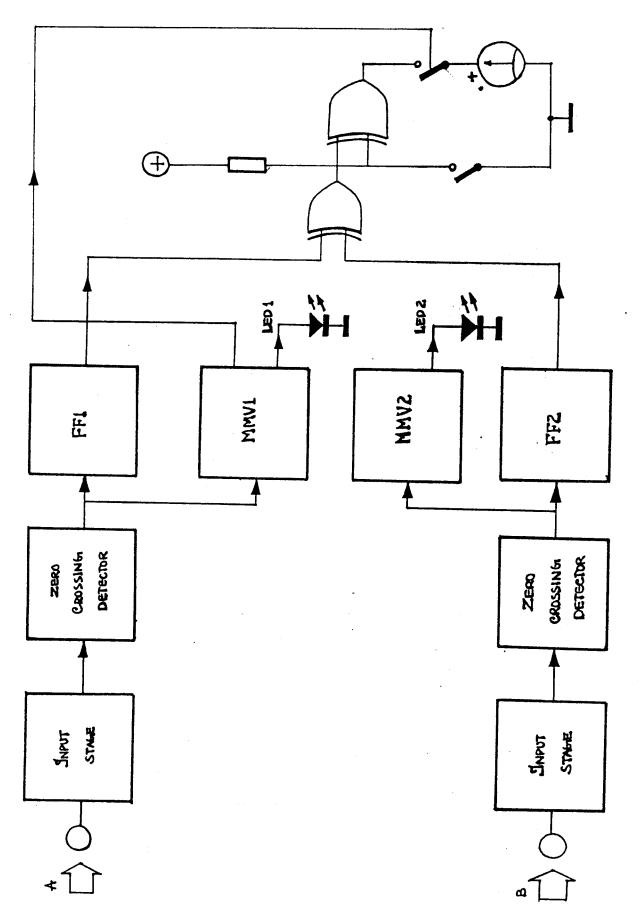

#### 3.1. BLOCK DIAGRAM OF THE SYSTEM

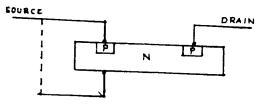

The basic design of the phase meter is presented in the block diagram shown in Fig.3.1. For the sake of simplicity the LED digital display has been replaced by an analogue meter.

The two analogue signals whose phase difference is to be measured are fed into two input stages respectively. These input stages are just buffers which are used for avoiding the loading on the signals. It matches the impedances of the comparator with the signal source.

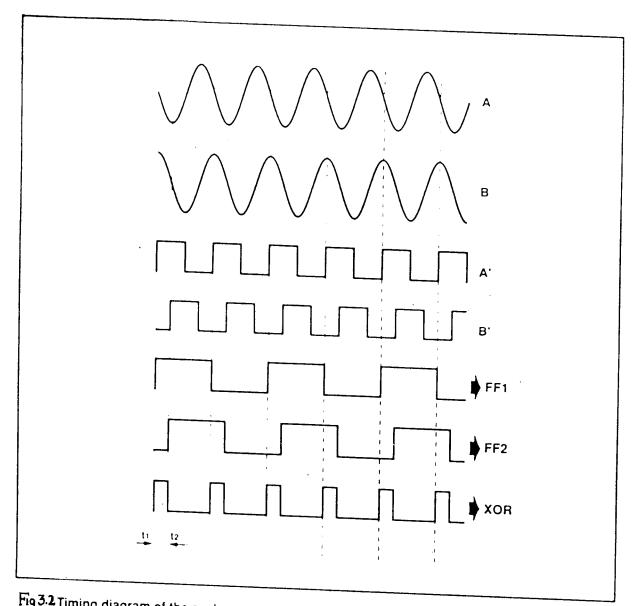

These signals from the buffer are given to two zero crossing detectors which are basically A to D converters. The analogue signals are digitised before they are processed. Since alternating signals are involved this is a simple process; the positive part of the signals are converted to a logic low (o), And the negative part to a logic high (1). The timing diagram for a typical signal is shown in Fig.3.2. It shows the analogue signals A and B (which are the inputs) together with their digitised varients A' and B'.

FIG. 3.1 BLOCK DIAGRAM OF THE DIGITAL PHASE METER

$\label{eq:fig3.2} \ensuremath{\text{Fig}} \ensuremath{\textbf{3.2}} \ensuremath{\text{Timing}} \ensuremath{\text{diagram of the analogue-to-digital conversion section.}}$

The output of the zero crossing detector are fed to two flip-flops  $FF_1$  and  $FF_2$ . The use of digitised signals as the clock for bistable flip flop ensures a perfectly symmetrical (ie. duty cycle is 50 per cent) digital output signal at a frequency equal to half that of the input signal. This guaranties that differing lengths of positive and negative half periods, noise, have no effect on the accuracy of the measurements.

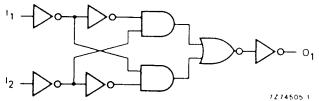

The time difference between the leading edges of signals eminating from the bistables is a measure of the phase shift between the two input signals. These outputs of the bistables are fed to the two inputs of an EXOR gate. The output of the EXOR gate is high during the time difference only. The ratio of the width of the logic high signal at the output of the EXOR gate to that of the output signal bistable FFl gives the phase shift, which only has to be converted to degrees. The width of the output pulse of EXOR gate indicates at all times by how much signal B Therefore the pulse represents Α. the difference of 0° to 360°. Since it may also be of interest to measure the lag of signal A with respect to signal B, there is a second EXOR gate whose output may be inverted.

Monostables MMVI and MMV2 indicate by LED's that usable signals, ie signals whose phase difference is to be

measured, exist at the associated inputs. Furthermore the output of MMVI is used to actuate the meter. If only signal A is present, the meters must remain stably in center position. If it does not, the input signal is unstable and therefore not suitable for measurements.

Since the width of the pulse at the output of the EXOR gate is a measure of the phase shift, it would seem that a simple analogue interface in the form of an integrator would be sufficient for driving a moving meter. That would, however, present certain difficulties, such as a strong dependance on temperature and the fact that to obtain a stable meter deflection a high integration constant would have to be used. That would make the measurement very slow and the instrument inconvenient to use.

A digital meter was therefore chosen, which can accurately indicate any phase difference between  $0^{\circ}$  and  $360^{\circ}$  with a resolution of  $1^{\circ}$ .

### 3.2. BUFFER SECTION

The input signals (A and B) are supplied separately to two buffer circuits. An operatitonal amplifier is made use for this purpose. A CMOS IC 3140 is selected for this purpose.

#### 3.2.1. Description

This IC has two inputs: the inverting input and the non-inverting input. These inputs go to a pair of P-channel FET's which act as a differential amplifier.

Any small voltage difference on the (+) and (-) inputs is sensed, strongly amplified by the three internal gain stages and the output is received at pin-6. A rising signal at the non-inverting (or +) input drives the output positive, while a rising signal on the inverting (or -) input drives the output negative. Since the two input signals are applied to two gates of the CMOS transistors, the input impedence is virtually infinite.

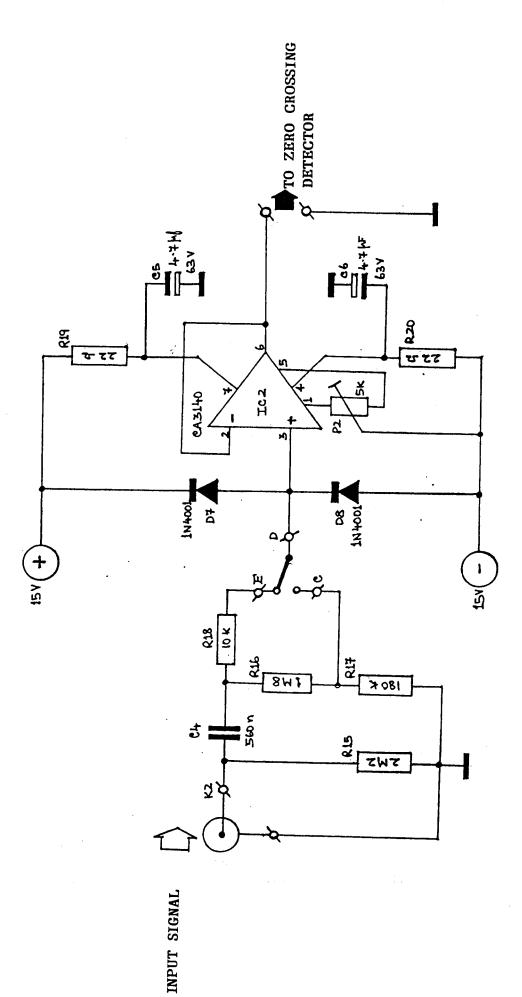

All operational amplifiers have an inherent offset voltage at their inputs that cannot be distinguished from an input signal. The buffer IC 3140 shown in Fig.3.3. has an offset voltage of about 8 mv and hence we use the offset potentiometer  $P_1$ , which is a potentiometer variable till 5K. This potentiometer unbalances the current mirror just enough to compensate for input offset. For adjusting the preset, we short the two inputs under in circuit conditions and then adjust the potentiometer until we get an open circuit, midrange output voltage. The two diodes  $D_5$  and  $D_6$  provide protection against over voltage. Frequency compensation is

24

FIG. 3.3 BUFFER CIRCUIT

#### HARDWARE DESCRIPTION

internally provided. The output stage is capable of driving capacitive loads.

When the inverting input terminal is shorted to the output pin (ie.pins 2 and 6). The op-amp acts as a unity gain amplifier which is a voltage follower. It gives a very high input impedace because the inverting input terminal does not act as a virtual ground. It can be compared to a super emitter follower with zero offset. The output is a low impedance, same size, same frequency, same polarity replica of an input signal which we cannot afford to load heavily.

Since all the voltage is fed back to the (-) input, the (-ve) input voltage will equal the output voltage. The high gain of the Op-Amp will force the (-) input to follow the (+) input.

#### 3.3. ZERO CROSSING DETECTOR

The zero crossing detector, is the circuit used to convert the buffered input signal into its digitised varient. We are making use of an operational amplifier IC for this purpose.

One of the most important applications of the operational amplifier is the zero crossing detector (A to D converter).

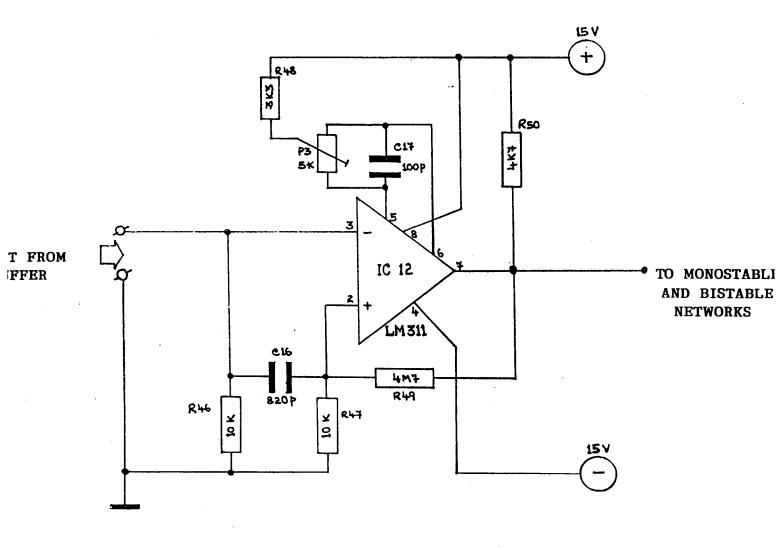

The buffered input signals are applied to the circuit shown in figure.3.4. there it is an open circuit operation of the Op-amp. The inverting terminal of the operational

FIG.3.4 ZERO CROSSING DETECTOR

#### HARDWARE DESCRIPTION

amplifier is connected directly to the input signal. The offset voltage compensation is provided by connecting a Rheostat in between pins five and six.

The principle of positive feedback is used here. The output voltage is fed back to the non-inverting terminal of the operational amplifier. The feed back resistor  $R_{49}$  is made a very high value compared to the series resistance  $R_{47}$  to provide significant hysterisis for the circuit, which ensures rapid output voltage transitions.

In open loop operation of the operational amplifier when it is used as a comparator the output voltage is positive when the amplitude of the voltage applied to the non-inverting terminal is greater than the amplitude of the voltage applied at the inverting terminal. The output voltage is negative when the voltage applied to the inverting terminal is greater than that applied to the inverting terminal is greater than that applied to the non inverting terminal when a constant voltage is applied to the non inverting terminal of the Op-amp and a varying amplitude signal to the inverting terminal. The output changes states (0 and 1), when the input voltage crosses the threshold voltage in both directions.

So the output of this zero crossing detector is a digitized signal which has a high state during the -ve 1/2 cycle of the signal and a logical low state during the +ve

1/2 cycle of the analogue input signal as shown in figure 3.2.

The resistance  $R_{50}$  which is connected in between the tue supply and the output pin acts as a voltage pull up resistor which increases the amplitude of the output voltage.

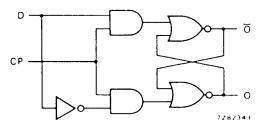

#### 3.4. BISTABLE MULTIVIBRATOR

#### 3.4.1. Description

Any device or circuit that has two stable states is said to be bistable. It's output is either in logical high stage or logical low state depending on the states of the input signals. Flip flop is a bistable electronic circuit that has two stable states (1 or 0). Any change in the logical status of the input signals are transmitted immediately to the outputs. It is also called a latch.

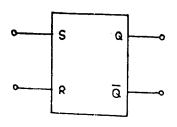

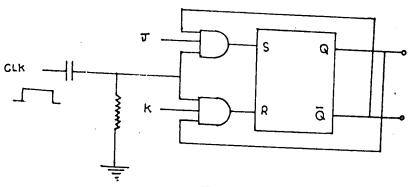

If we consider a R-S flip flop (set Reset flip flop), the status of the outputs are as shown in table 3.1. Fig.3.5. represents an R - S flip flop.

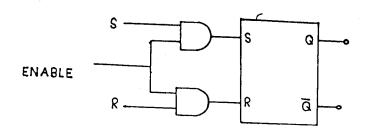

When we provide two AND gates as the input stage for an R-S flip flop as shown in Fig.3.6, we get a clocked R-S flip flop whose output changes depend on the clock signal. When enable input is low, the AND gate outputs are both low and hence there is no change in the output states of the flip

flop. The latch is said to be disabled. When the enable signal is high the R and S inputs are passed through and hence the output Q of the flip flop changes. This flip flop is called a clocked R-S flip flop.

#### J - K FLIP FLOP

JK flip flops are ideal circuit elements that can be used for the purpose of counting. Fig. 3.7. shows how to build J - K flip flops.

The variables J and K are called control inputs because they determine what the flip flop does when a positive clock edge arrives. As before the Rc circuit has a short time constant, thus converting the rectangular clock pulse into narrow spikes. Because of the AND gates the circuit is positive edge triggered.

Table 3.2. shows the truth table for J-K flip flops. When J and K are both low, both AND gates are disabled. Therefore clock pulses have no effect. This first possibility is the initial entry in the truth table. As shown when J and K are both O's, Q retains its last value.

When J is low and K is high, the upper gate is disabled, so there is no way to set the flip flop. The only possibility is reset. When Q is high the lower gate passes a reset trigger as soon as the next positive clock edge

Table 3.1

FIG. 3.5

| _R | S | la            |

|----|---|---------------|

| 0  | 0 | Last State    |

| 0  | 1 | 1             |

| 1  | 0 | 0             |

| 1  | 1 | ? (forbidden) |

TRUTH TABLE

# LOGIC SYMBOL FOR AN RS FLIP FLOP

FIG. 3.6 LOGIC DIAGRAM FOR A CLOCKED RS FLIP FLOP

FIG. 3.7 J-K FLIP FLOP

|          | Tal  | b]le | 3.2 |

|----------|------|------|-----|

| CLK      | J    | ĸ    | Qnu |

| ×        | 0    | 0    | Qn  |

| <b>†</b> | 0    | 1    | 0   |

| 1        | 1    | 0    | 1   |

| <b>↑</b> | 1    | 1    | Qn  |

| TI       | RUTE | I TA | BLE |

arrives. This forces Q to go low. Therefore J=0 and K=1, means that the next positive clock edge resets the flip flop (unless  $\overline{Q}$  is already reset). When J is high and K is low, the lower gate is disabled, so it is impossible to reset the flip flop.

But you can reset the flip flop as follows. When Q is low, Q is high; therefore the upper gate passes a SET trigger on the next positive clock edge. This drives Q into the high state. As you can see J = 1 and K = 0 means the flip flop will be SET for the next clock edge (Unless Q is already high).

When J and K are both high (notice that this is the forbidden state with an RS flip flop), it's possible to set or reset the flip flop. If Q is high, the lower gate passes a RESET trigger on the next positive clock edge. On the other hand, when Q is low, the upper gate passes a SET trigger on the next positive clock edge. Either way, Q changes to the complement of the last state. Therefore J = 1 and K = 1 means the flip flop will toggle on th next positive clock edge. Toggle means to switch to the opposite state. J - K master slave flip flops are used to prevent "racing".

The last entry in the truth table is effectively used to build a frequency divider.

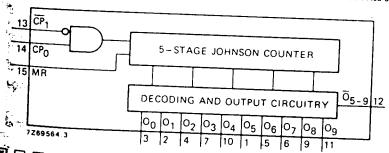

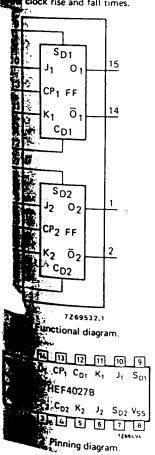

The output of the zero crossing detector is a digitized varient of the input analogue signal. This signal has the same frequency as the input signal. This output from the zero crossing detector is used as the clocking signal for a J-K flip flop. In the circuit we are using a CMOS IC 4027 which is a dual J-K flip flop. We are using this as a frequency divider. We use the condition where, when J=1 and K=1 at the clock edge, the output of the flip-flop toggles ie., changes to the opposite state.

The IC 4027 is used to half the frequency of the signal that is the digitized version of the input sinusoidal signal. This IC has two negative edge triggered J-K flip flops.

#### 3.4.2. Operation

The two inputs J and K are tied together and are connected to the positive DC voltage of 15 volts. So now the two inputs J and K are at a logical high state.

The outputs of the zero crossing detectors are applied to the clock input of each of the two flip flops. At every negative clock edge of the clock input, the output of the J-K flip flops change to their opposite state (ie toggles).

#### HARDWARE DESCRIPTION

This occurs because both J and K inputs are at a logical high state. So at the Q outputs of the two flip flops we get two pulse trains as shown in the timing diagram shown in Fig. 3.2.

From the figure we can easly see that the time period of each pulse has been doubled. So in effect the frequency of the output of the flip flop is half that of the input pulse train.

$$F_{out} = F_{in}/2$$

This halving of the frequency ensures a perfectly symmetrical signal (1/2 the frequency of the input signal) (duty factor is 50 per cent). This guarantees that differing lengths of positive and negative 1/2 periods, noise and other spacious signals have no effect on the accuracy of measurement.

Now at the output of the two J-K flip flops IC 13a and IC 13 b we have two digital signals which are the digitized varients of the two input signals whose phase difference is to be measured, with half their frequency.

#### 3.5. MONOSTABLE MULTIVIBRATOR

## 3.5.1. Description

Monostables have one stable state and one unstable state. They remain in their stable state until they are

triggered. Triggering places them temporarly in the other state. After a certain time delay, the monostable snaps back into its original condition.

Monostables are generally used for medium accuracy pulse genrators and time delay generators. They are also used to detect leading and trailing edges of waveforms.

Here we are using the monostable to indicate the presence of two input signals whose phase difference has to be measured.

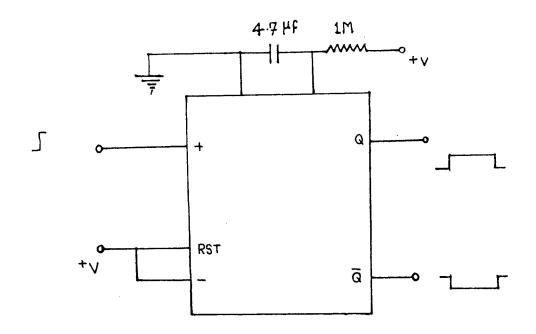

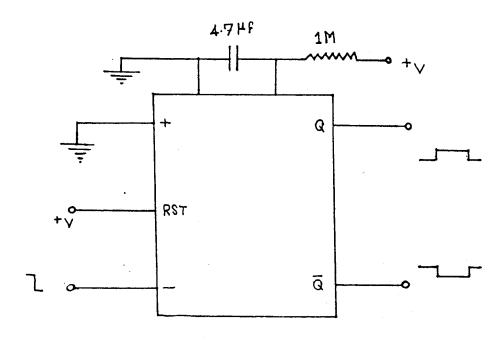

In the circuit we are using a dual retriggerable monostable IC (4528). Here both retriggerable monostables are used separately.

In normal operation the clear inputs (3 and 13) are held high. Pins 1 and 15 are grounded. If we are using the monostable to detect the leading edge of a waveform then we use the +ve inputs (4 and 12) to give the pulse and the -ve inputs (5 and 11) are given the supply voltage  $V_{\rm cc}$ . If we are using the monostable to detect the trailing edge of the signal then we give the input pulses to pins (5 and 11) and the positive inputs (4 and 12) are connected to the ground. Figure to detect leading edges is shows in Fig.3.8. (a), and that which illustrates detection of trailing edges is shown in Fig.3.8. (b).

FIG. 3.8 (a)

POSITIVE EDGE TRIGGERED USING 4528

FIG. 3.8 (b)

NEGATIVE EDGE TRIGGERED USING 4528

When we supply the pulse, triggering will drive the Q output high and  $\overline{Q}$  output low for a length of time set by the resistor and capacitor. The one time can be shortened by bringing the clear input low. A low clear input also prevents output pulses during power up times.

The timing resistor can range from 10 K to 10M ohms while the timing capacitor can range from 20 Pf upwards. The circuit is retriggerable; If more than one triggering pulse arrives during the ON time, the RC product determines the delay after the last triggering edge arrives.

T = RC

The timing capacitor is discharged after every triggering. This causes a capacitor dependent delay between the time you trigger and the time you actually get any output. This delay is almost a microsecond with a 1000 pf timing capacitor and a 5 volts supply. Several milliseconds can elapse before you get an output after triggering with microfarad sized timing capacitors.

Always we should use a large timing resistor for a given ON time to minimise start up delay.

The minimum input pulse width is 70 nanoseconds at 5 volts, and 30 nanoseconds at 10 volts. Minimum output pulse width is 550 ns at 5 volts and 350 ns at 10 volts.

## 3.5.2. Operation

The digitized output of the zero crossing detector to the manostable multivibrator IC applied Fig. 3.8.(a). The input is given to the positive pin. So this multivibrator detects the leading edge of the input signal. As soon as the positive edge occurs the monostable goes into quasistable high state. The duration of the quasistable state is determined by the timing capacitors ( $C_{20}$  and  $C_{21}$ ). When the monostable is set by the positive edge of the input pulse, the capacitor starts charging and the period of the quasistable state depends on the product of the timing capacitor and resistance. So the LED's  $(D_q$  and  $D_{10})$ showing the presence of two signals at the input whose phase difference is to be measured. The output of the monostable drives the bases of the two transistors to whose collectors are connected the corresponding LED's.

The  $\overline{\mathbb{Q}}$  output of monostable multivibrator 1 also drives the reference counter.

#### DIGITAL MEASURING SECTION

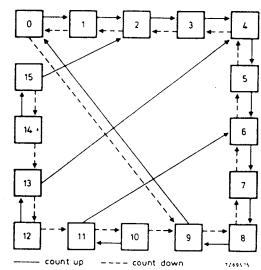

#### 4.1. COUNTER SECTION

A counter is probably one of the most useful and versatile subsystem in a digital system. A counter driven by a clock can be used to count the number of clock cycles. Since the clock pulses occur at known intervals, the counter can be used as an instrument to measure times and therefore period or frequency. There are basically two different types of counters synchronous and asynchronous.

The ripple counter is simple and straight forward in construction and usually requires the minimum of hardware. It does, however, have a speed limitation. Each flip flop is triggered by the previous flip flop and thus the counter has a cumulative settling time. Counters such as these are called serial or asynchronus.

An increase in the speed of operation can be achieved by the use of parallel or synchronous counters. Here every flip flop is triggered by a clock (in synchronism), and thus settling time is simply equal to the delay time of a single flip flop. The increase in speed is usually obtained at the price of increased hardware.

Serial and parallel counters are used in combination to compramise between speed of operation and hardware size, serial, parallel or combination counters can be designed such that each clock pulse advances the contents of the counter by one. It is then operating in a count up mode. The opposite is also possible, the counter then operates in a count down mode.

Futher more the counters can be either "cleared' so that every flip flop containes a zero, or preset such that the contents of the flip flop represents any desired binary number.

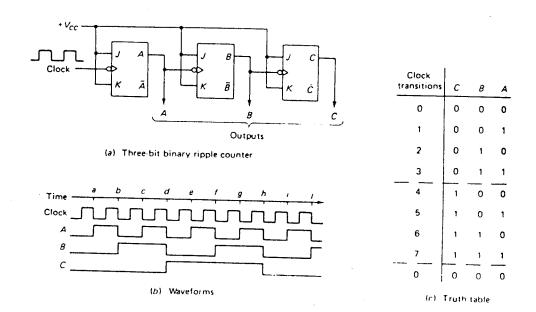

### 4.1.1. Asynchronous Counters

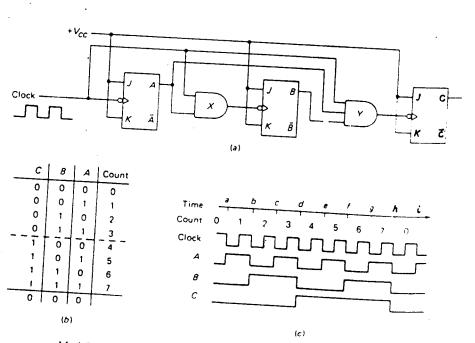

A binary ripple counter can be constructed by use of clocked J-K flip flops. Fig.4.1. shows three masterslave, J-K flip flops connected in cascade. The system clock, a square wave drives flip flop. The output of A drives B, and the output of B drives flip flop C. All the J and K inputs are tied to  $+V_{\rm CC}$ . This means that each flip flop will change state (toggle) with a negative transition at its clock input.

When the output of a flip flop is used as the clock input for the next flip flop, we call the counter a ripple counter or asynchronous counter. The A flip flop must change

states before it can trigger the B flip flop, and the B flip flop has to change states before it can trigger the C flip flop. The triggers move through the flip flops like ripples on water. Because of this the overall propagation delay time is the sum of the individual delays. For instance, if each flip flops in the counter has a propagation delay of 10 ns, overall propagation delay time for the counter is 30 ns.

The waveforms given in Fig 4.1(b) shows the action of the counter as the clock runs. Let's assume that the flip flops are all initially reset to produce 0 outputs. If we consider A to be the least significant bit (LSB) and C the most significant bit, we can say the contents of the counter is 000.

Every time there is a -ve clock transition flip flop A changes states. Thus at the first -ve clock transition A goes high, at the second -ve edge it goes back low. At point C it again goes back high. Notable is the feature that the output of the flip flop A is 1/2 that of the input frequency.

Since A acts as the clock for B, each time the waveform at A goes low, flip flop B will toggle. Thus at point B on the time line B goes high. It then goes low at point b and toggles back high at point f. The waveform at the output of

flip flop B is one half the frequency of A and one fourth that of the clock frequency.

Since B acts as the clock for C, each time the waveform at B goes low, flip flop C will toggle thus C goes high at point d on the time line and goes back low again at point ah. The frequency of the waveform at C is one half that at B, but it is only one eighth of the clock frequency.

The output condition of the flip flops is a binary number equivalent to the number of negative clock transitions that have occurred. Prior to the point 'a' on the time line the output condition is CBA = 000. At point 'a' on the time line the output becomes 001. At point 'b' it changes of 010 and so on. In fact a careful examination of the waveforms will reveal the counter count advances one count for each clock transition until the count reaches lll. At this point the counter resets back to 000 and begins the count cycles all over again we can say that this ripple counter is acting in count up mode.

n flip flops in cascade have  $2^n$  output conditions and represents a maximum binary equivalent of the decimal  $2^n - 1$ .

The modules of a counter is the total number of states through which the counter can progress. A counter with n flip

flops is called a modulus 2<sup>n</sup> counter.

When the  $\overline{A}$  output is used as the clock for flip flop  $\overline{B}$  and  $\overline{B}$  as the clock for flip flop C the counter acts as a down counter and counts from 7 downwards till zero.

## 4.1.2. Synchronous Counters

A ripple counter is the simplest to build, but there is a limit to its highest operating frequency. As previously discussed, each flip flop has a delay time. In a ripple counter these delay times are additive and the total "settling" time for the counter is approximately the delay times the total number of flip flops. Furthermore there is the possibility of glitches occurring at the outputs of decoding gates used with a ripple counter. Both of these problems can be overcome by the use of a parallel counter. The only difference is that every flip flop is triggered in synchronism with the clock.

The construction of one type of parall binary counter is shown in Fig.4.2. (a), along with the truth table and the waveforms of a natural count sequence in Fig.4.2. (b). Since each state corresponds to an equivalent binary number (or count), we refer to each state as a count from now on. The basic idea here is to keep the J and K inputs of each flip flop high, such that the flip flop will toggle with any negative clock transition at its clock input. We then use

FIG. 4.1

Mod-8 parallel binary counter

FIG. 4.2

and gates to gate every second clock to flip flop B, every fourth clock to flip flop C and so on. This logic configuration is often referred to as steering logic since the clock pulses are gated or steered to each individual flip flop.

The clock is applied directly to flip flop A. Since the J - K flip flop is used to respond to a negative clock transition. Its o/p toggles for each -ve transition of the clock.

Since, AND gate Y is enabled and will transmit the clock to flip flop C only when both A and B are high flip flop C changes state with every fourth negative clock transition. This is a mod-8, parallel or synchronous binary counter operating in the count up mode.

#### Advantages

- Whenever a flip flop changes state, It toggles at exactly the same time as all the other flip flops; in other words all the flip flops change state in synchronism.

- 2. As a result of synchronous change of state. It is not possible to produce a glitch at the output of the decoding gate. So the decoding gates need not be strobed.

Till now we have explained the construction of synchronous and Asynchronus counters to count the multiples of two ie., till 2, 4, 8, 16, 32 etc. It is often desirable to construct counter having moduli other than 2, 4, 8. For example, a counter having modulus 3 or 5. A smaller modulus counter can always be constructed from a counter of high modulus by skipping states.

The correct number of flip flops is determined by choosing the lowest natural count that is greater than the desired modified count.

#### Operation

- 1. Prior to point a on time line A = 0 B = 0 a -ve clock

transition at a will cause.

- a. A to toggle to 1, since its J and K inputs are high b. B to reset to 0

- 2. Prior to point b on the time line A = 1 and B = 0. A negative clock transition at b will cause.

- a. A to toggle to a 0, since its J and K inputs are high

- b. B to toggle to 1, since its J and K inputs are high

- 3. Prior to point c on the time line, A = 0 and B = 1. A negative clock transition at C causes.

- a. A to reset to zero

- b. B to reset to zero since its J input is low and its

K input is high.

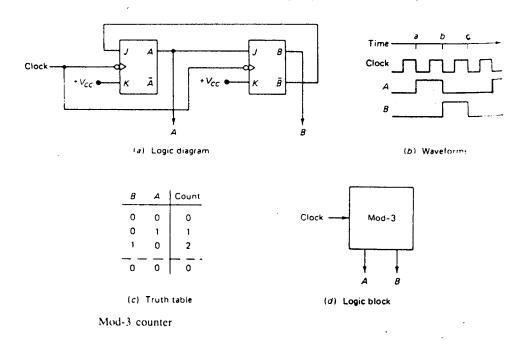

This can be considered as a devide by 3 block, since the output waveform at B (or at A) has a period equal to three times that of the clock in another words, this counter divides the clock frequency by 3. A MOD-3 synchronous counter and its timing diagram is shown in Fig.4.3. (a) and Fig.4.3. (b) respectively.

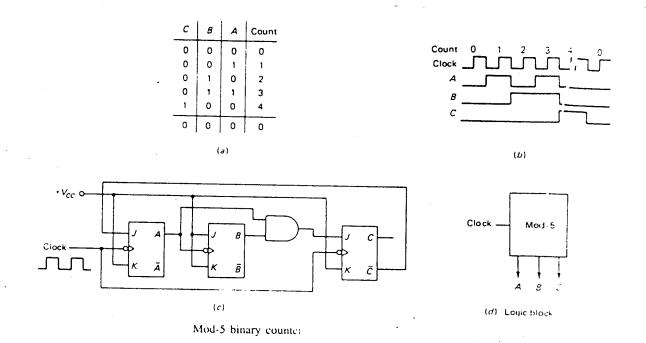

#### 4.1.4. Mod-5 Counter

The 3 flip flop counter shown in Fig.4.4. (a) has a 4.1.(a) natural count of 8. But in the circuit shown in fig. 4.1(a), the circuit is connected such that it advances one count at a time, beginning with 000 and ending at 100. Therefore this is a mod-5 counter.

The waveforms shown in Fig. 4.4. (b) show that flip flop A changes states each time the clock goes negative except during the transition from count 4 to count 0. Thus flip flop A should be triggered by the clock and must have an inhibit during count 4 - ie some signal must be provided during the count from 4 to count 0.  $\overline{C}$  is high during all the counts except count 4.

If  $\overline{C}$  is connected to the J input of flip flop A, we have the desired inhibit signal. This is true since the J and K to inputs the flip flop A are both true for

FIG. 4.3

FIG. 4.4

all counts except count 4. Thus the flip flop triggers each time the clock goes negative. However, during count 4, the J side is low and next time the clock goes negative the flip flop will be prevented from being set.

The desired waveforms in fig 4.4 (b) shows that flip flop B must change state each time A goes negative. Thus the clock input of flip flop B will be driven by A as shown in Fig.4.4. (a).

input is held low and K input is high, every clock pulse will reset it. Now if the J input is high only during count 3, C will be high during count 4 and low during all other counts. The necessary levels for the J input can be obtained by AND ing flip flops A and B. Since, A and B are both high only during count 3 the J input to flip flop C is high only during count 3. Thus when the clock goes negative during the transition from count 3 to count 4, flip flop C will be set. At all other times, the J input to flip flop C is low and is held at a reset state. The complete mod-5 counter is shown in Fig.4.4. (a).

The 3 flip flop counter does not count 5, 6 and 7 during its normal operating sequence, but there is a very real possibility that these three counters may initially set in any one of these three (illegal) states when power is

initially switched on. None of these three states cause the counter to malfunction, and it will automatically work itself out of any illegal state after only one clock transition.

Mod-5 counter can be used in cascade to construct higher modulus counters. For example modulus 10 or Decade Counter.

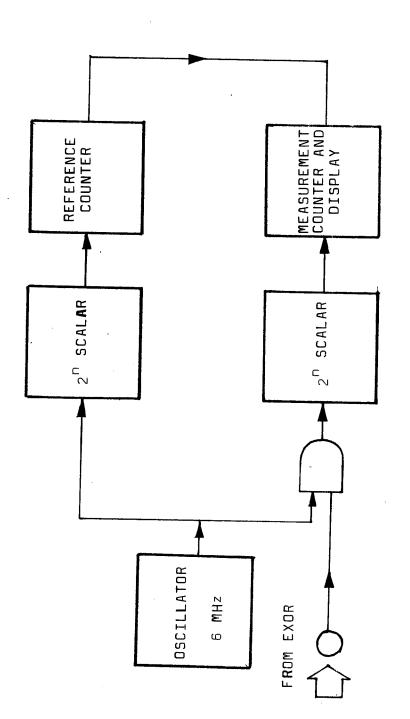

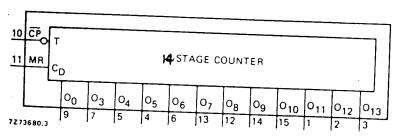

# 4.2. DESCRIPTION

The block diagram of the measuring section in shown in Fig.4.6. A crystal oscillator in used to generate a central clock frequency of 6 MHz. This central clock frequency of 6 MHz is applied continuously to one branch of the circuit, and to other branch only when the output of the XOR gate of the phase comparator is high. In both the branches of the circuit, the clock pulses are divided by 2<sup>n</sup> before they are applied to the respective stage. The factor n can be set manually by using a rotary switch. It in important to observe that since the division takes place after the AND gate, this gate, has no effect on the accuracy of the instrument.

The counting always starts at the beginning of a period. As soon as the content of the reference counter has reached a value of 3,600 one output of the counter goes high

BLOCK DIAGRAM OF THE DIGITAL MEASURING SECTION. Fig. 4.6.

to indicate that measurement in complete and that 3600/2n pulses were processed during it.

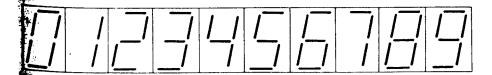

At the instant the reference counter has counted 3,600 pulses the display memory in prompted to take over the contents of the measurement counter. The display will then show the number of the counted pulses, that is, when the phase shift in  $0^{\circ}$ , no pulses were counted, if the phase shift is  $360^{\circ}$ , 3600 pulses were counted. The last digit of the number of pulses is omitted to make the display read the no.of degrees.

It sould be noted that the accuracy of the measurement depends on the ratio of the measuring time to the frequency of the reference signal. The measurand is therefore sampled at a frequency of 6 MHz. Even at the highest signal frequency of 20 KHz, the error introduced by this is negligible.

Further more the design of the instrument arranges that counting always starts at the beginning of a period. Therefore it is never known how much of the last period is measured and steps must be taken to ensure that last period has negligible influence on the measurement. This in done by taking many periods per measurement. For instance, a measurement over 10 periods has a possible error of 10 per cent whereas over 200 periods the error would be only 0.5 per cent. Because of that the instrument contarly a counter

# DIGITAL MEASURING SECTION

(in error indicating circuit) that moniters over how many signal periods a measurement was spread.

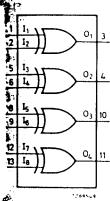

#### DESCRIPTION OF THE CIRCUIT

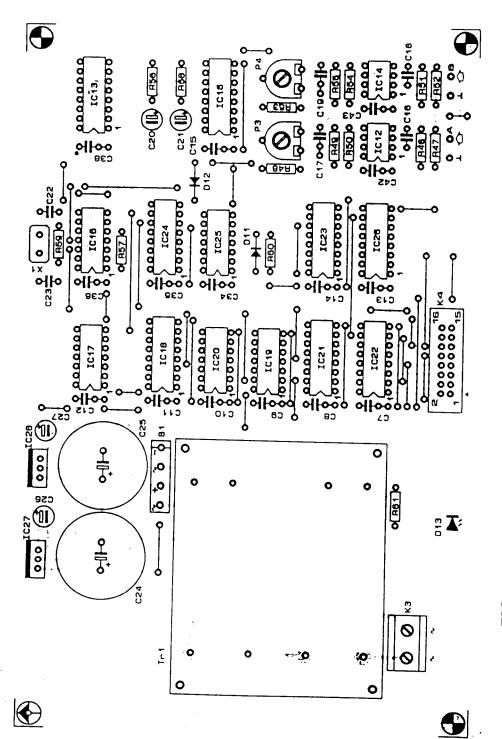

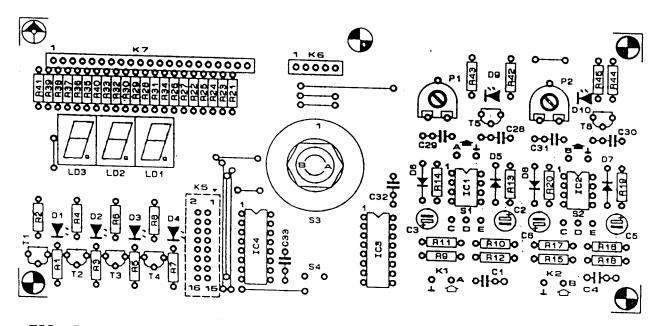

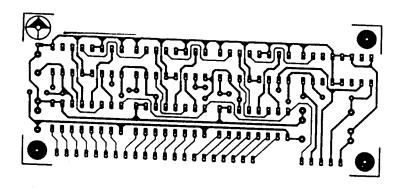

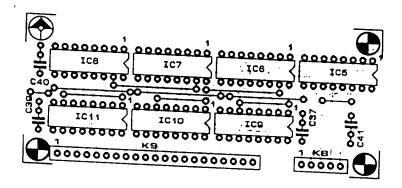

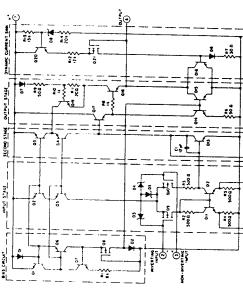

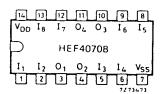

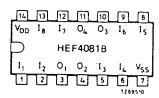

The instrument in constructed on three printed circuit boards, the associated circuits are shown in Fig.5.1, 5.2 and 5.3.

The fig (5.1) is the circuit diagram for the mother board the power supply in a straight forward, conventional type with a bridge rectifier and two integrated regulators.

The buffered and possibly attenuated (-20dB) signal is applied to terminals A and B. Input A in used as reference signal and for actuating the metering section.

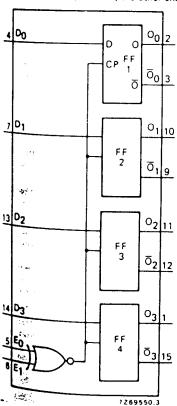

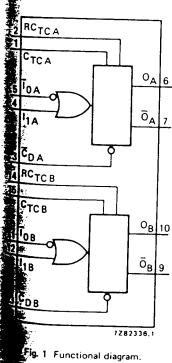

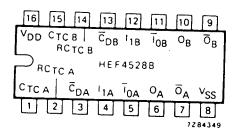

The incoming analogue signal is converted into a digital signal in IC 12 (channel A and IC 14 (Channel B). The offset of these Op-Amps is compensated by presets  $P_3$  and  $P_4$  respectively. Bistables IC 13a and IC 13b split, the digitized signal into symmetrical signal (duty factor - 50 per cent) that is suitable for measurements.

Monostables IC 15a and IC 15b actuate the LED's (D $_9$  and D $_{10}$ ) on the front panel to indicate that suitable signals are input.

The outputs of IC 13a and IC 13b are combined Via EXOR Gate IC 16a. Another XOR Gate IC 16b and switch S4 on the

front panel make it possible to invert the phase difference as discussed before.

Finally IC 17a which is an AND gate combines the output of the phase comparator with the clock frequency (6 MHz). When the output of XOR gate IC 16a is high, the clock is passed on and the measurement may be carried out.

The clock signal is generated by a crystal oscillator based on IC 16c. This clock signal is buffered by IC 16d before it is applied to the relevant stages.

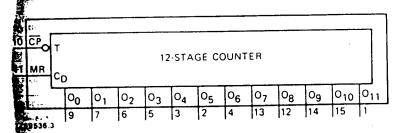

At the end of measurement a reset cycle in started by IC 24, which is a 12 stage binary counter. As soon as this IC has counted 3600 poines, IC 23b (J-K flip flop) is set via IC 25a (And gate) and OR gate  $D_{11}$  -  $D_{12}$  and in its turn resets decade scaler IC 26. This actuates the latch signal, where upon the counter state is transferred to the display drivers. Subsequently IC 22 receives a clock pulse and stores data concerning any measurement error, after which IC 21 is reset. All relevant measurement data are then stored and the remainder of the circuit in reset via bistable IC 23a. When the reset cycle in over, IC 23a is returned to the relevant output state via, AND gate IC 17b. At the same time, IC 24 is reset by the clock pulse that appears at the Q 9 O/P of

decade counter IC 26. This circuit in then ready for next measurement.

As mentioned before, the more periods are used, the more accurate the measurement. The counter in error detector IC 18 countes the number of periods between the onset of the measurement and the generated latch pulse. Four AND gates decode the result at 360, 180, 90 and 36 periods in one measurement. These counts correspond to errors of 0.5°, 1°, 2° and 5° respectively. Depending on the no.of counted periods, one or more LED's light; when they all light, the error is negligibly small.

Figure 5.2. shows the circuit of display the indicators the i/p stages and the stage for selecting the measurement duration. The indicator LED's are driven by transistors; the control lines are connected to relevant points on the mother board via K5.

The input impedance in about 1 M. ohms large input signals may be attenuated by 20dB ( $S_1$  and  $S_2$ ). All input signals are buffered by type CA3140 Op-Amps before they are applied to the comparator on the mother board. The inputs of these buffer are protected against over voltage by diodes. Presets  $P_1$  and  $P_2$  serve to minimize the offset at the output of the Op-amps.

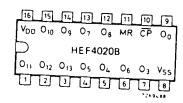

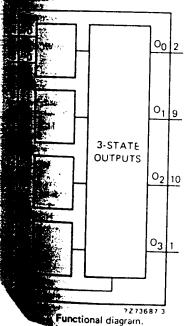

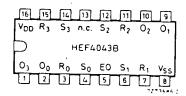

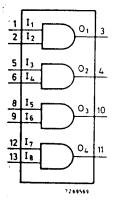

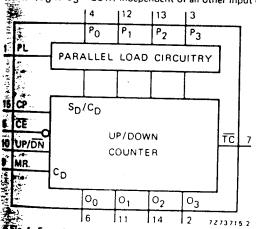

Circuits IC 3 and IC 4 (4020) are programmable 2<sup>11</sup> dividers IC 3 counts the clock pulses passed by AND gate IC 17a, that is, the pulses that indicate how long the output of XOR gate IC 16b has been high. The no.of these pulses depends entirely on the phase shift between the two input signals. IC4 is the reference counter that receives clock pulses continually.

The scaling factor in set with  $S_3$ ; it enables the user to select a measurement time that is most suitable for the frequency of the input signal. The error indicators on the display show whether the correct time has been selected.

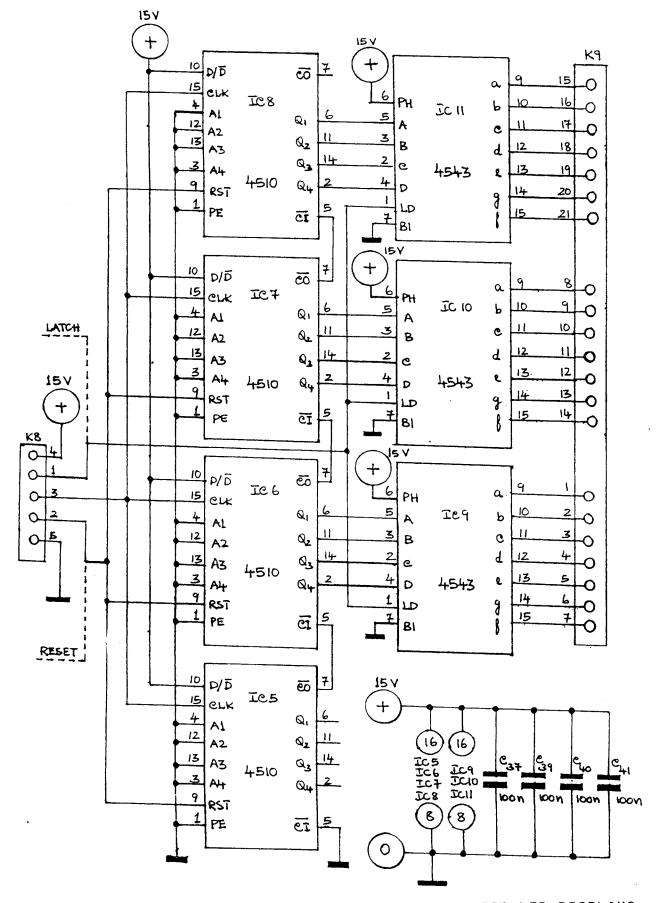

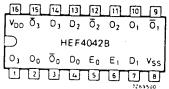

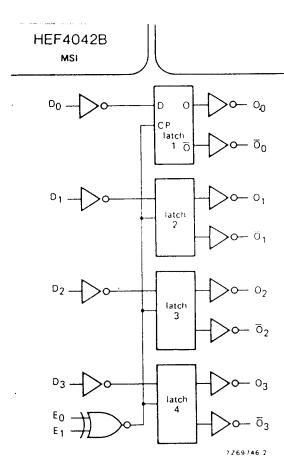

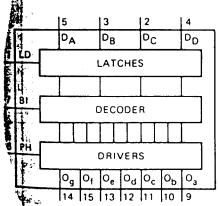

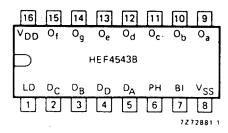

Fig.5.3. shown the circuit contained on the third PCB; the seven IC'S form the display counter and interface for the LED displays.

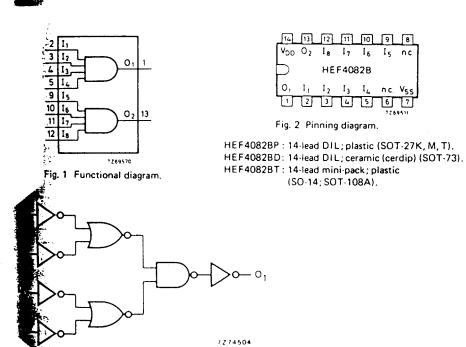

The clock pulses to be counted are applied to cascaded counters IC 5 - IC 8 (4510) via pin 3 of K8.

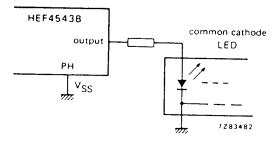

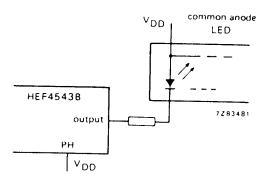

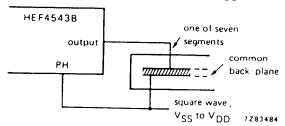

As soon as the latch signal in active, the counter state in stored in display drivers IC 9 - IC 11 (4543). The displays, connected with this part of the circuit via  $K_9$ , light to show the correct value measured.

At the reset command at pin2 of  $K_8$  the counters are returned to zero and a new measurement cycle can be started. The previous measurement value in retained on the displays

# DESCRIPTION OF THE CIRCUIT

because the display drivers are not reset. The next measurement is thus carried out while the displays show previous result.

Fig.5.3. DIAGRAM OF THE LOGIC CIRCUITS FOR LED DISPLAYS.

# CIRCUIT CONSTRUCTION

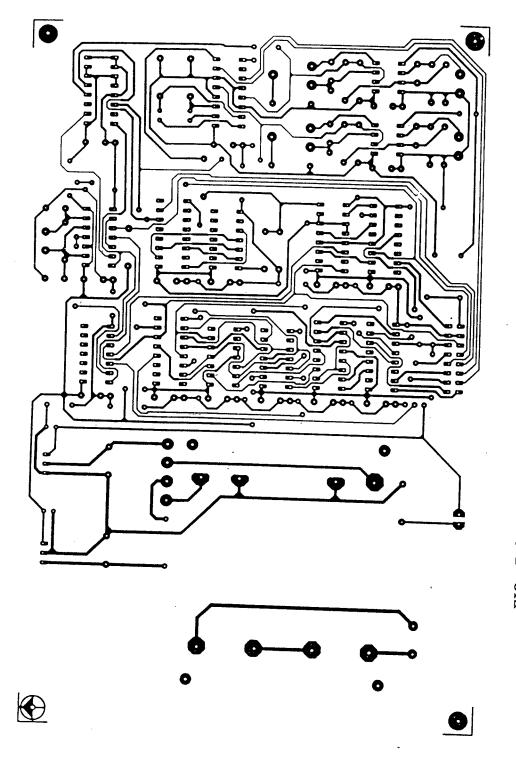

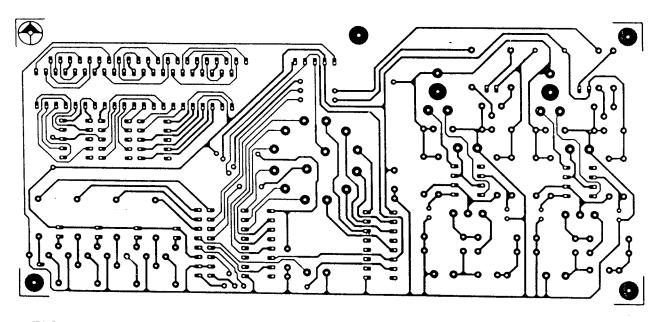

The 3 PCBs are shown in the figures B-1 to B-6 in the Appendix - B. Their population is straight forward, but it is best to begin with boards 2 and 3.

Connectors  $K_8$  and  $K_9$  on the board 3 may be replaced by right angle print headers. As a bonus, such headers would ensure a firm mechanical link between boards 2 and 3. In any case, the boards are provided with poles to enable corner braces to be used for strong mechanical linking.

The LED displays should be mounted on the board 2 about 1 cm (3/8 inch) above the board with the aid of wive wrap IC scokets.

Now connect the switches  $\mathbf{S}_1$ ,  $\mathbf{S}_2$  and  $\mathbf{S}_4$ , to the board with short lengths of wire and fit  $\mathbf{S}_3$  directly to the board.

Cut the terminal wires of  $D_1$  to  $D_4$  and  $D_9$  and  $D_{10}$  to about 2 cm (13/16 inches); this will ensure that they will be located exactly behind the windows in the front panel.

Fit soldering pins at A and B and adjacent earth points at the track side of board 2. The power on indicator,  $D_{13}$ ,

is best fitted to the front panel with the aid of an LED clip or super glue.

Fit board 2 on suitable spacers directly behind the front panel. Just prior to tightening the screws, connect the input sockets to the board via short wires. Next, screw the three toggle switches to the front panel.

Finally mount board 3 at right angles to the track side of board 2.

Mount the board on the bottom plate of the enclosure, after which all necessary electrical connections to the other boards, the power on LED, and ON-OFF switch to mains entry plug can be made.

Finally, interlink points A and B, and associated earthing points, on the mother board and board 2 by single screened audio cable.

# CALIBRATION AND USE

Having constructed the circuit of the digital phase meter, it in now required to calibrate it.

Calibration of the phase meter is confined to adjusting the four presets.

Short circuit inputs A and B and adjust  $P_1$  and  $P_2$  for zero output of IC 1 and IC 2.

Now remove the short circuit from the inputs and apply a sinusoidal audio frequency at a level of about 10 mV to the inputs. Adjust  $P_3$  until comparator IC 12 toggles exactly at the zero crossing point, check this on an oscilloscope. Finally adjust  $P_4$  until the display shows a phase difference of  $0^{\circ}$ .

Start measuring the phase shift by applying the two signals to the inputs and turning  $S_3$  (gate time) fully clock wise. Then turn the switch anti clock wise step by step (when the accuracy increases). When the indicator, marking a measuring error of  $0.5^{\circ}$  lights, the optimum position for this measurement has been reached. Since the measurement period increases all the time, it may take a few seconds at

low frequencies before the indicator lights. That is, however, the price to be paid for accuracy at low signal frequencies.

# POWER SUPPLY OF THE SYSTEM

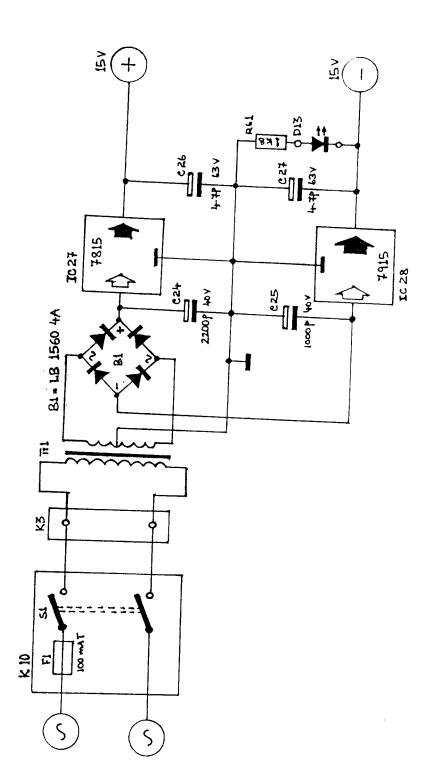

This project utilizes CMOS IC's. The minimum voltage required for these chips is  $\pm$  15V dc supply. The operational amplifiers used also need  $\pm$  15 dc supply. The block schematic shown in the Fig.8.1, describes the method to obtains a dc supply of  $\pm$  15 V and  $\pm$  15 V from an Ac voltage of 230 V and 50 Hz.

This schematic contains a step down centre tapped transformer  $T_{rl}$ , a bridge rectifier Bl and regulators. The i/p dc supply is fed to the primary of transformer  $T_{rl}$ . The switch  $K_{10}$  is a mains entry plug. It has got a provision for the fuse. This switch  $K_{10}$  acts as the main switch. The secondary winding of the transformer  $T_{rl}$  is a centre tapped one and the output obtained in 18V, 2A. This voltage is now fed into a bridge rectifier (Bl) LB 15604A for obtaining the dc voltage of  $\pm$  15 V. The secondary voltage from the transformer is full wave rectified by the diodes. The dc voltage obtained will generally be in the form of dc pulsatory wave. This is due to the ripple ie., the ac component present in the dc output received from the bridge rectifier circuit. In order to successfully eliminate this ripple a capacitor network in used. This network contains

Fig.8.1 POWER SUPPLY OF THE SYSTEM.

capacitors  $C_{24}$  and  $C_{25}$  in parallel. The filtered output is fed to the regulator IC's 7815 and 7915 for obtaining a stabilised dc voltage of + 15V and -15 V respectively. Still if there is any ripple present in the dc component of regulator outputs, the capacitor  $C_{26}$  and  $C_{27}$  eliminate them. The output in obtained across this capacitor and this will be a pure dc supply.

The 78XX series of regulators which come in a T0220 package generally can supply 500 ma. Therefore the maximum power dissapated in them is probably going to be 500 ma times the voltage difference between the input and output terminals. This might mean that the regulator has to dissapate 5W of heat, therefore an adequate heat sink is provided to it.

In the above metnioned circuit, the fitting of the main input socket, the fuse holder and the mains transformer is fairly straight forward.

# PRINTED CIRCUIT BOARD DESIGN

Printed circuit boards are generally used for laying out complex digital circuits.

The common problems which we meet with if not properly designed are listed as follows:

- Reflections (causing signal delays and also double pulsing i.e., conversion of one pulse into two or more pulses).

- 2. Cross talk (interference between neighbouring signal lines).

- Ground and supply line noise.

- 4. Electromagnetic interference from pulse type EM fields (under high noise conditions).

#### REFLECTIONS

In families of fast  $t_r$  (rise time) of IC's the conductors must be looked as a piece of transmission lines rather than short circuits. The transmission lines are normally mismatched on both sides so that multiple reflections take place based on the particular value of wave impedance of the conductor.

While designing the main points to be looked is that it must be having a proper value of wave impedance a value which has least reflections.

This wave impedance is chosen by selecting the width of the signal lines lower values of wave impedance such as needed in ECL IC's require broader signal conductors. Relatively larger value of wave impedance as needed by TTL, CMOS etc., require small width signal conductors. As in a digital circuit we are having a low operating frequency, double pulsing can't be tolerated. The double pulsing is the result of reflections.

For TTL logic, a wave impedance of 100 to 150 is desirable. The signal lines hence is 0.5 mm wide. The standard width of PCB dielectric is 1.6 mm. The signal lines can be even 1 mm wide only if then ground lines are farther away.

Current drawn or sunk back into the IC will be very large 20 mA and -55 mA for 50 line PCB for the rising and trailing edges respectively. These currents spikes have to be supplied by the Vcc line, (rising edge) or fed to the ground lines (trailing edge). Hence, in TTL PCB's wave impedance of 50 or less must be avoided. Very high impedance such as 720 ohms also cause problems making voltage as

well as double pulsing very high. Hence, in TTL IC's loose wiring (high impedance) must be avoided and signal connections must run always near the ground line.

For CMOS circuits, broad PCB conductors for signal lines is avoided. The wave impedance must be high and the signal line width is 0.5 mm. If the wave impedance is 150 to 300 ohms, the transitions will be considerably faster. The above value can be obtained if signal line width is low, the ground lines are not too broad and kept too near the signal lines. In the wiring between PCB's one should definitely avoid using 50 ohm cables and also the wave impedance must be high.

#### CROSS TALK

The considerations that cross talk can be kept low are uncritical, if ground line or a ground plate is nearby. A ground line that runs between two signal lines eliminates almost all cross talk and should be used whenever the situation becomes too critical. A special problematic situation occurs, when signal lines run next to each other with a logical flow (signal flow) on opposite directions. Then it will be generally advisable to run a ground line between the two signal lines, specially for the more critical cases of TTL and ECL IC's.

#### GROUND AND SUPPLY LINE NOISE

This is perhaps the most serious problem with TTL - IC's and is present in reduced form with ECL - IC's and in very much reduced form, with CMOS IC's. This problem can definitely be solved with proper PCB layout and with a few, very simple measures.

The two principal measures are:

a. To have a low impedance Zw between proper supply line and ground line. This is obtained by providing a large copper surface for ground either full ground broad as it is possible in the case of multilayer boards or at least a ground mesh on finally leaving the copper in all unused ports of PCB such as corners etc., and connecting it to the ground.

Current spikes are drawn from the Vcc line and fed in to the ground line during the IC's transition. These currect spikes are partly needed to charge or discharge the transistor within the IC while they switch and this current is referred as internal current spike which is required to chage on discharge the transmission lines (i.e., conductors) connected to the IC's output. Internal and external spike are super imposed and must be carried by the same Vcc and ground lines. If many synchronous gates or flip flops are connected to the same point, the situation becomes even worse. Thus ground and supply line noise is reduced.

#### CHAPTER 11

#### BIBLIOGRAPHY

- 1. K.BLAIR BENSON "Audio Engineering Handbook" , McGraw Hill Ltd.

- JOHN.D.LENK "Handbook of Oscilloscopes, Theory and application", Prentice Hall, Inc.

- 3. ALBERT PAUL MALVINO and DONALD.P.LEACH "Digital Principles and Applications" McGraw Hill Book Company, Fourth Edition.

- 4. A.K.SAWHNEY "A course in Electrical and Electronic Measurements and Instrumentation", Dhanpat Rai and Sons.

- 5. Robert Boylestad and Louis Nashelsky "Electronic Devices and Circuit Theory" prentice Hall of India Private Ltd., Fourth Edition.

- 6. DON LANCASTER "CMOS Cookbook" , Howard W.Sams and Company, Second Edition.

- 7. "Digital IC Data Book" CMOS PHILLIPS PART 4, JULY 83.

- 8. ELEKTOR ELECTRONICS JOURNAL, JULY, 1991.

#### CMOS FEATURES

#### Complimentary metal oxide semiconductors (CMOS)

#### **Advantages**

- It is ultra low in cost.

- It is available in hundreds of devices from a dozen major manufacturers.

- 3. Works over a wide, non critical power supply range.

- 4. It uses zero power when inputs aren't changing and very little power when they are.

- 5. Inputs are essentially opencircuits, and its outputs swing the whole range between supply limits.

- 6. Output drive to other CMOS packages in unlimited.

- 7. It is very forgiving to system noise and does'nt generate much noise on its own.

- 8. It is easily converted to linear operation and offers dozens of options towards high performance, count timers, oscillators and pulse sources.

The above mentioned advantages are ample reasons for chosing CMOS IC's for this project.

#### The CMOS process

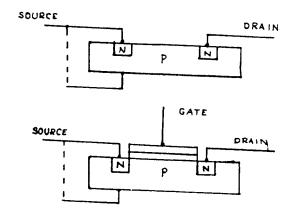

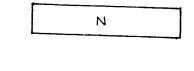

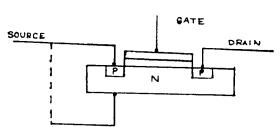

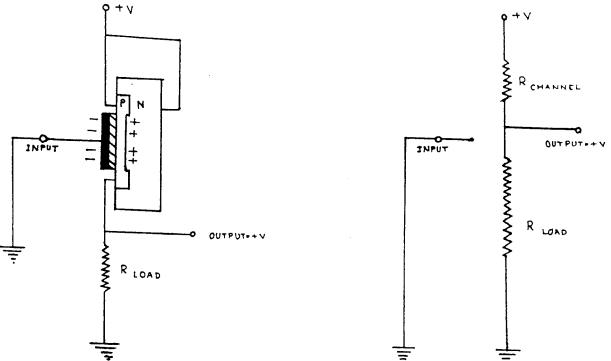

Fig (A-1) shows how we build a transistor called an n-channel enhancement mode Mos devise. We start with a bar of

START WITH A BLOCK OF P-TYPE SILICO (P MATERIAL HAS EXCESS HOLES)

DIFFUSE OR IMPLANT TWO N REGIONS, FORMING PN JUNCTIONS. (N REGIONS HAVE EXCESS ELECTRONS)

ADD OHMIC CONTACTS AND CALL THE THREE REGIONS SOURCE, DRAIN, AND SUBSTRATE. FOR SOME USES SOURCE AND SUBSTRATE MAY BE CONNECTED TOGETHER. (OHMIC CONTACTS ARE CONNECTIONS THAT DONT RECTIFY)

A VERY THIN LAYER OF SIO, OR ANOTHE INSULATOR IS BUILT UP BETWEEN SOURC AND DRAIN, A CONDUCTOR IS ADDED TO THE TOP OF THIS INSULATOR, FORMING A CAPACITOR.

FIG A-1. BUILDING AN n-channel MOS transistor.

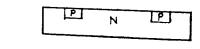

START WITH A BLOCK OF N-TYPE SILICON.

DIFFUSE OR IMPLANT TWO P REGIONS FORMING PN JUNCTIONS.

ADD OHMIC CONTACTS AND CALL THE THREE REGIONS SOURCE, DRAIN, AND SUBSTRATE.

A VERY THIN LAYER OF SIO OR ANOTHER INSULATOR IS BUILT UP BETWEEN SOURCE AND DRAIN. A CONDUCTOR IS ADDED TO THE TOP OF THIS INSULATOR, FORMING A CAPACITOR.

FIG A-2. BUILDING A P-CHANNEL MOS TRANSISTOR

p-type silicon. P-type silicon is ultrapure, single crystal silicon (derived from ordinary beach sand). With just enough of an impurity introduced that there all too few electrones to go around. The absence of an electron where an electron is expected to be is called a hole. We say that P-type silicon has an excess of holes. A hole has an equivalent positive charge that equals and offsets the negative charge of an electron.

Now we diffuse two junctions into our silicon block, or substrate. This builds up two n-type silicon regions. The n-type silicon regions have an excess of electrones in them. These two regions are introduced by diffusing or ion-implanting, additional impurities that are carefully selected to tip the balance towards an excess of electrones in these new regions.

P-N junction conducts current when P is more positive than N, blocks current when N is more positive.

Ohmic contacts are made with the three regions of the silicon bar. One of the n-regions is called the source and the other n-region the drain.

To control the current flow between out source/substrate terminal and our drain terminal, we build a

special capacitor between source and drain on the surface of the transistor.

We begin building our capacitor with a dielectric or insulating layer of silicon dioxide, glass, or some other insulator. This layer of dielectric is extremely thin. On top of this insulator we place a new conductor we call a gate. An ohmic contact is provided for the gate too, called the gate lead. The conductor can be a metal. Silicon gates are more sensitive and faster.

Biasing voltages or currents are applied to this basic transistor to actuate this device.

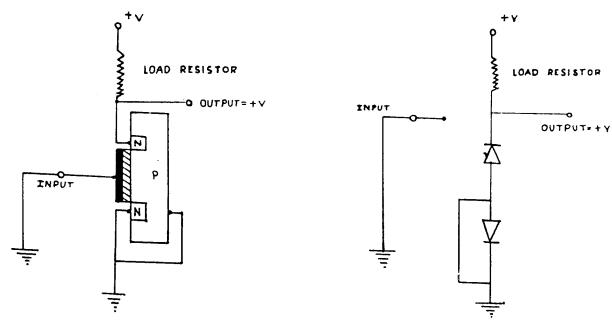

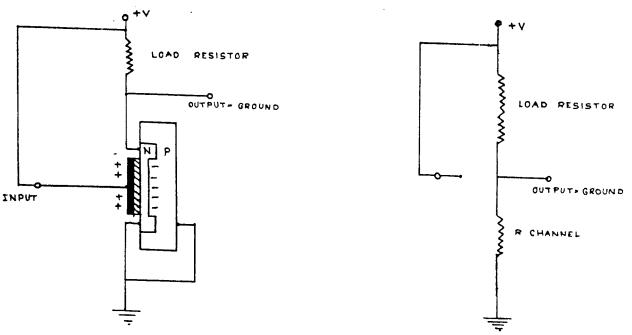

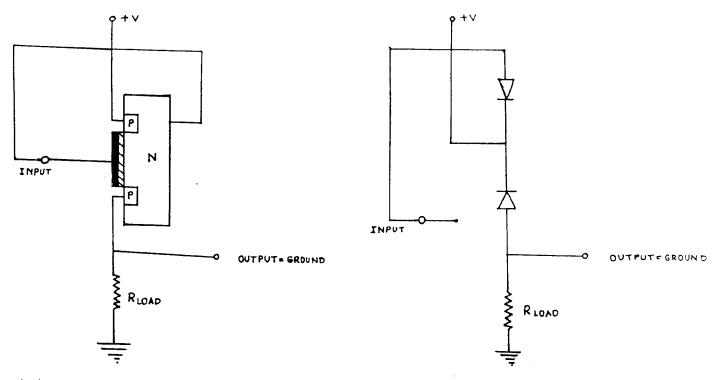

Fig A-3 shows how we bias our transistor. We usually are the gate as the input, drain as the output, substrate and source all connected to ground or some other voltage.

In Fig.A-3 (a) we have grounded our source and substrate and drain connected to a -ve voltate, +V, through a load resistor. Gate input is also grounded.

Due to the circuit connections the drain junction acts as a reverse bias (open circuit). The capacitor being grounded doesnot charge. So the output become +Vcc. So a grounded I/P gies a +ve O/P.

- (A) OFF. Grounded input prevents channel from forming. Output is high.

- (B) Equivalent OFF circuit.

(C) ON. + V gate input forms low resistance n-channel.

(D) Equivalent ON circuit.

Fig. A-3. BIASING AN N-CHANNEL MOS TRANSISTOR.

- (A) OFF.Input at + V Prevents channel from forming. Output is grounded.

- (B) Equivalent OFF circuit.

(C) ON. Grounded gate input forms low-resistance pchannel in response to charge on gate. (D) Equivalent ON circuit.

Fig. A-4. BIASING A P-CHANNEL MOS TRANSISTOR.

If gate is connected to the supply +v source as in fig 4.3. (c). The left side of the capacitor now has positive charges, or holes, placed on it. When the capacitor charges, it must end up with extra electrons on the right side.

The surface just under the dielectric was a p-type material meaning it was deficient of electrons. The building up of electrones neutralise the holes in the p-type material and hence the whole region becomes intrinsic. More electrones cause the substrate to turn to n type material at the surface.

Thus we have a n channel connecting the drain and source. So now a short circuit occurs between drain and source terminals to ground. So the output becomes zero. So we have turned the transistor on by applying a +ve gate voltage. The amount of voltage needed to turn the transistor on is called the threshold voltage. Since our transistor is normally off, and since we have to force it on by actively doing something to it, it is called an enhancement mode device.

#### Note:

- Input is always open circuit since gate lead goes only to a capacitor hence no I/P current needed.

- When the transistor turns on, it is simply a solid bar of material or a plain resister.

The construction, biasing and equivalent circuits of the P channel mosfet is shown in the figures above. The only difference between P-channel and n-channel mosfets are that they are exactly the opposite in operation.

Here a grounded gate produces a low voltage at the output (transistor on). A +ue voltage applied to the gate produces a high voltage at the output (transistor off). Here the substrate and drain are tied together and the source is grounded through the load resistor.

FIG. B-1 TRACK SIDE LAYOUT OF THE MOTHER BOARD

FIG. B-2 COMPONENT SIDE LAYOUT OF THE MOTHER BOARD

FIG. B-3 TRACK SIDE LAYOUT FOR THE DISPLAYS, INPUT STAGES AND SELECTOR SWITCHES.

FIG. B-4 COMPONENT SIDE LAYOUT FOR THE DISPLAYS, INPUT STAGES AND SELECTOR SWITCHES.

FIG. B-5 TRACK SIDE LAYOUT FOR THE LOGIC CIRCUITS FOR THE LED DISPLAYS

FIG. B-6 COMPONENT SIDE LAYOUT FOR THE LOGIC CIRCUITS FOR THE LED DISPLAYS

**CA 3140B**

Operational Amplifiers

BIMOS

With MOS/FET input, bipolar output

The CA3140B, CA3140A, and combine the advantages of high-voltage PMOS transistors Because of this unique sitors on a single monolithic CA 3140 are integrated-circuit operational amplifiers amplifiers that with high-voltage bipolar trancombination of technologies this device can now provide designers, for the first time, with the special performance eatures of the CA 3130 COS/ and the versatility of the 741 industry-standard operational amplifiers. operational series

gate-pro-The CA3140, CA3140A, and CA3140 BiMOS operational ected MOS/FET (PMOS) transistors in the input circuit to at supply voltages from 4 to operational amplifiers rent, and high-speed performance. The CA3140B operates provide very-high-input im very-low-input curfeature amplifiers pedance,

CA 3140 from 4 to 36 volts in unity-gain follower are also provided for use in 14 volts; the CA 3140A and are internally phase-compensated to achieve stable operhave access terminals for a roll-off is desired. Terminals applications requiring input offset-voltage nulling. The use operation, and, additionally, supplementary external caof PMOS field-effect transistors in the input stage results (either single or dual supply) pacitor if additional frequency hese ation

ALL MESSTANCE VALUES ARE IN OHIS 2 00 E to ground. The CA3140 series has the minal, an important attribute in common-mode input-voltage capability down to 0.5 volt below the negative-supply terfor single-supply applications. he output stage uses bipolar transistors and includes builtin protection against damage cuiting to either supply-rail or from load terminal short-cir-

RCA

# Maximum ratings, absolute-maximum values:

| CA 3140, CA 3140A                                          | CA 3140B |

|------------------------------------------------------------|----------|

| DC supply voltage                                          |          |

| (Between V <sup>+</sup> and V <sup>−</sup> terminals) 36 V | 4<br>2   |

**4 +8**

1 mA

630 mW

derate linearly 6.67 mW/°C

to (V--0.5 V) (\(\gamma\) +8\(\gamma\) Common-mode DC input voltage Differential-mode input voltage Input-terminal current Device dissipation:

without heatsink: up to 55°C

with heat sink: above 55°C

lemperature range: above 55°C up to  $55^{\circ}$ C

derate linearly 16.7 mW/°C

-55 to +125°C -65 to +150°C Indefinite

Operating (all types) storage (all types)

Output short-circuit duration\* Lead temperature

1/16 ± 1/32 inch (1.59 ± 0.79 mm) (during soldering): at distance

from case for 10 seconds max .:

Short circuit may be applied to ground or to either supply.

Application

| TYPICAL ELECTRICAL CHARACTERISTICS         | TRICAL CHAR    | ACTERISTICS               | ļ          |          |         |          |

|--------------------------------------------|----------------|---------------------------|------------|----------|---------|----------|

|                                            |                | TEST                      |            |          |         |          |

| CHARACI                                    | CHARACTERISTIC | V15 V                     | CA31408    | CA3140A  | CA3140  | STIMO    |

|                                            |                | VV                        | (1,S)      | (1,S.E)  | (T,S,E) |          |

|                                            |                | TA - 25°C                 |            |          |         |          |

|                                            |                | Typ. Value of Re-         |            |          |         |          |

| Local Office Walness                       | 1              | sistor Between            |            |          |         |          |

| Advistment Peristor                        | 300            | Term. 4 and 5 or          | <b>Ş</b>   | 92       | 4       | ç        |

|                                            |                | 4 and 1 to Adjust         |            |          |         |          |

| Input Resistance                           | ٩              |                           | 1.5        | 5.1      | 1.5     | ជា       |

| Input Capacitance                          | <del>ن</del>   |                           | •          | •        | •       | ۳.       |

| Output Resistance                          | O.H.           |                           | 8          | 8        | 9       | a        |

| Equivalent Wideband<br>Input Noise Voltage | ages en        | ВW = 140 кН2<br>RS = 1 MΩ | 84         | 84       | 2       | <b>ક</b> |

| Equivalent Input                           |                | + 1 kHz RS-               | Ç          | 0,       | ĝ.      | الغ      |

| Signal Store                               | E              | 1 • 10 kHz 100 fl         | 13         | 12       | 12      | 2        |

| Short-Circuit Current to                   | rent to        |                           |            |          |         |          |

| Opposite Supply Source 10M+                | Source 10M*    |                           | 9          | 0.       | 40      | Ę        |

|                                            | Sink iOM"      |                           | 18         | 18       | 18      | Ψ        |

| Gain-Bandwidth<br>Product,                 | F              | •                         | 4.5        | 4.5      | 4.5     | WHY      |

| Stew Rate,                                 | RS             |                           | 6          | 6        | 6       | V/µs     |

| Sink Current From Terminal 8               | m Terminal 8   |                           |            |          |         |          |

| To Terminal 4 to Swing Output Low          | Swing<br>0     |                           | 2,20       | 8        | 230     | 4        |

| Transient Response:                        | 3              | B. = 2 kΩ                 |            |          |         |          |

| #:F -: 10.                                 | -              | C. = 100 oF               | 800        | 8        | 3       | =        |

| Overshoot                                  |                | - 1 co b.                 | 10         | 10       | 10      | ×        |

| Settling Time                              | 1 mV           | R 2 kΩ                    | 4.5        | 4.5      | 4.5     | :        |

| , A.A.                                     | 10 mV          | Voltage Follower          | <b>*</b> : | <b>1</b> | *       | s.       |

same 8-lead terminal pin-out used for the '741' and other industry-standard operational

Sample and hold circuit.

TOT ME GLANTS

in either the standard 8-lead TO-5 style package (T suffix), or in the 8-lead dual-in-line formed-lead TO-5 style pack-CA 3140 is available in chip and CA 3140 are also available

age 'DIL-CAN' (S suffix). The

form (H suffix). The CA3140A

amplifiers. They are supplied

- pedance (ZIN) 1.5 TΩ MOS/FET input stage a. very high input im-

- (II) 10 pA typ. at ± 15 V Very low input current input-voltage range (VICR) age (VIO) - to 2 mV max. c. Low input-offset voltd. Wide common-mode can be swung 0.5 volt below negative supply

- plements input common- e. Output swing comvoltage rail

mode range

- Directly replaces industry bipolar diode protected type 741 in most appli-Rugged input stage

- Includes numerous induscategories such as general try operational amplifier purpose, FET input,

cations

volts single or dual supplies Operation from 4-to-44

operation at supply voltages

in an 8-lead dual-in-line plastic The CA3140B is intended for ranging from 4 to 44 volts, for

package (Mini-DIP-E suffix)

mium-grade specifications and lished for operations over the

applications requiring

with electrical limits estab-

The CA 3140A and CA 3140 are for operation at supply

range from -55°C to +125°C

- operation down to 4 volts TTL supply systems with Characterised from ± 15-Internally compensated volt operation and for

- High voltage-follower slew MHz unity gain at ± 15 V or 30 V; 3.7 MHz at 5 V Wide bandwidth - 4.5

operated safely over the temperature range from -55°C to +125°C.

All types can be

18 volts). voitages

up to 36 volts (±

Fast settling time — 1.4 μs typ. to 10 mV with a 10rate - 9 V/μs

Photocurrent instrumen-

seconds-minutes-hours)

Output swings to within / p-p signal

Peak detectors

Active filters Comparators

0.2 volt of negative sypply Strobable output stage

## Applications:

single-supply amplifiers Ground-referenced

supply voltage systems

Interface in 5 V TTL systems & other low-