# Wireless Surviellance of Energy

# **Project Report**

Submitted By

Sriram.K.M.

Shanthakumar.R.

Sudhakar.K.

Mohankumar.N.S.

Guided By

Prof . Muthuraman Ramasamy, M.E., MISTE., (Ph.D)

Head of the ECE Department

2002 - 2003

In partial fulfillment of the requirements for the award of the Degree of

BACHELOR OF ENGINEERING IN ELECTRONICS & COMMUNICATION ENGINEERING

Of the Bharathiar University, Coimbatore

Department of Electronics & Communication Engineering

Kumaraguru College of Technology

Coimbatore - 641 006.

# Kumaraguru College of Technology

Department of Electronics & Communication Engineering

Coimbatore – 641 006

# **CERTIFICATE**

| This is to certify that the contents of the project report entitled |                          |  |  |  |

|---------------------------------------------------------------------|--------------------------|--|--|--|

| 'WIRELESS SURVEILLANCE OF ENERGY'                                   |                          |  |  |  |

| has been submitted by Mr/Ms                                         |                          |  |  |  |

| In partial fulfillment of the requirem                              | ent for the award of the |  |  |  |

| Degree of BACHELOR OF I                                             | ENGINEERING              |  |  |  |

| IN ELECTRONICS & COMMUNICATION ENGINEERING                          |                          |  |  |  |

| Branch of the Bharathiar Unive                                      | ersity, Coimbatore.      |  |  |  |

| During the academic year                                            | 2002 – 2003              |  |  |  |

|                                                                     |                          |  |  |  |

| Internal Guide                                                      |                          |  |  |  |

| Internal Guide                                                      | Head of the Department   |  |  |  |

| Certified that the candidate with University R                      | egister Number           |  |  |  |

| was examined by us in Project Viva – Voce Ex                        | xamination held on       |  |  |  |

| hamproprise and                                                     | 35 18h                   |  |  |  |

External Examiner

Internal Examiner

# **ACKNOWLEDGEMENT**

We express our sincere thanks to our beloved Principal, Mr.K.Padmanaban B.Sc. (Engg), M.Tech., Ph.D., for all the facilities provided in carrying out this project work.

We express our gratitude and indebtedness to our respected guide Prof. Muthuraman Ramasamy M.E., FIE. FIETE., MIEEE (USA)., MISTE., MBMESI., C.Eng.(I)., Head of the department of Electronics and Communication engineering for his full fledged technical guidance, constant encouragement and suggestions in carrying out this project.

We also take this opportunity to thank our Assistant Professors Mr.K.Ramprakash M.E., and Mr.S.Govindaraju M.E., for sharing their in depth knowledge on the subject and providing us with tips as and when required.

We would also like to thank all the teaching and non-teaching staff for guiding us throughout, without which our project would not have been a great success.

## **SYNOPSIS**

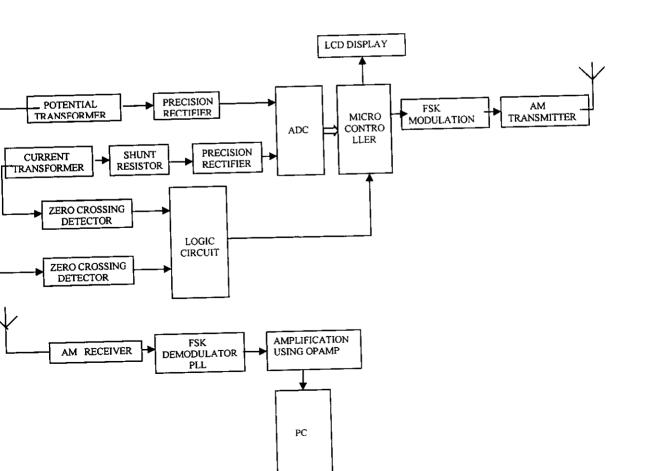

This project is microcontroller based Energy Monitor and transmission of energy through wireless to an EB substation This Project deals with the transmission of the various parameters automatically to the Computer based server through wireless media. The various parameters that would be transmitted are:

- Voltage Reading

- Current Reading

- Power Factor

- Power

- Energy Consumed

The mode of transmission used is wireless, but depending on the economy and various factors it could be done with the help of a telephone line or power line too. Our project uses 89C52 micro controller effectively for reading the above mentioned parameters by efficient programming. Since the core component is the micro controller it is cost effective as well as accurate, which is one of the main criteria for any measuring device. The parameters measured are displayed using LCD display through 8255 PPI. For the conversion of analog signal to digital signal ADC is used.

The measured parameter readings are transmitted using Frequency Shift Keying (FSK) Technique. This FSK technique uses two frequencies of lower range. So in order to transmit without attenuation this frequencies are modulated with high frequency carrier signal. By having server based control the main advantages like 24- Hour Surveillance, automatic fault detection, preventing illicit usage, reduced man power can be achieved.

On the receiver end the received signal is demodulated using a technique which then converted in to 0's and 1's in order to receive at the computer. We have used C as a front-end tool, which displays various parameters. With the help of a computer based server we can calculate the Bills for the used electricity, which could be received like the telephone bills of the present days.

# **CONTENTS**

| ACKNOWLEDGEMENT<br>SYNOPSIS                       | PAGE NO |

|---------------------------------------------------|---------|

| 1. INTRODUCTION                                   |         |

| 1.1 NEED FOR THIS PROJECT                         | 2       |

| 1.2 OVERVIEW                                      | 2       |

| 1.3 BLOCK DIAGRAM                                 | 4       |

| 2. POWER SUPPLY UNIT                              |         |

| 2.1 TRANSFORMER                                   | 6       |

| 2.2 RECTIFIER                                     | 6       |

| 2.3 FILTER                                        | 6       |

| 2.4 REGULATOR                                     | 7       |

| 2.5 CURRENT TRANSFORMER                           | 8       |

| 2.6 POTENTIAL TRANSFORMER                         | 9       |

| 2.7 DIFFERNCE BETWEEN C.T AND P.T                 | 9       |

| 3. PRECISION RECTIFIER AND ZERO CROSSING DETECTOR |         |

| 3.1 PRECISION RECTIFIER                           | 11      |

| 3.2 ZERO CROSSING DETECTOR (ZCD)                  | 13      |

| 3.3 ZCD FOR PHASE MEASUREMENT                     | 15      |

| 4. MICROCONTROLLER BOARD DETAILS                  |         |

| 4.11 MICROCONTROLLER 89C52                        | 18      |

| 4.12 PIN DIAGRAM                                  | 19      |

| 4.13 ARCHIECTURE                                  | 20      |

| 4.14 MEMORY ORGANISATION                          | 23      |

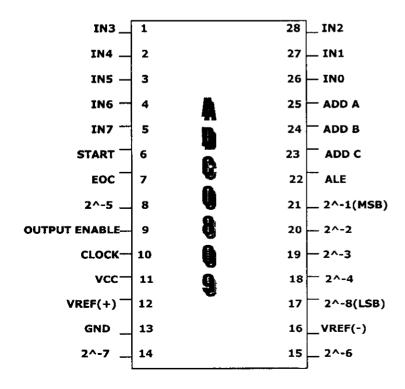

4.20 ANALOG TO DIGITAL CONVERTER (ADC0809)

25

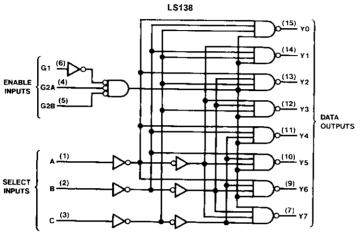

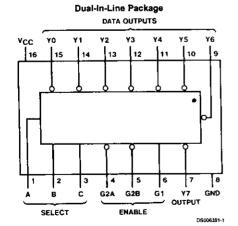

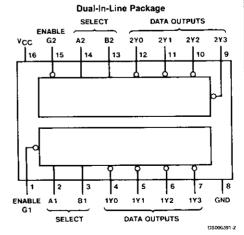

| 4.3      | DM74LS138 DECODER                      | 27         |

|----------|----------------------------------------|------------|

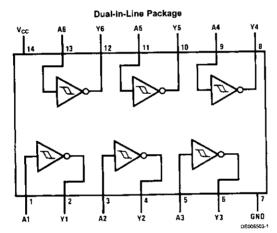

| 4.4      | DM7414 HEX INVERTER                    | 27         |

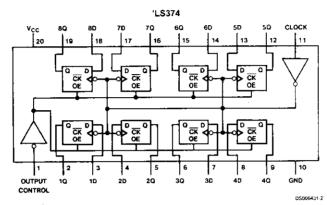

| 4.5      | DM74LS373 TRANSPARENT LATCH            | 28         |

| 4.6      | 74LS393 COUNTER                        | 29         |

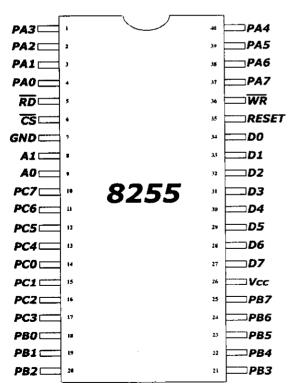

| 4.71     | 8255-PROGRAMMABLE PERIPHERAL INTERFACE | 30         |

| 4.72     | PIN DIAGRAM                            | 30         |

| 4.73     | BLOCK DIAGRAM                          | 31         |

| 5. AM T  | RANSMITTER                             |            |

| 5.1      | FSK GENERATOR (555 TIMER)              | 34         |

| 5.2      | AMPLITUDE MODULATION                   | <i>3</i> 6 |

| 5.3      | CD4011 NAND GATE                       | 37         |

| 6. AM R  | ECEIVER                                |            |

| 6.1      | ENVELOPE DETECTOR                      | 38         |

| 6.2      | PHASE LOCK LOOP (IC 565)               | 39         |

| 7. 89C5  | 2 MICROCONTROLLER PROGAMMING           | 42         |

| 8. 'C' C | DDING                                  | 75         |

| 9. CON   | CLUSION                                | 79         |

| 10. BIB  | LIOGRAPHY                              | 81         |

| 11. APF  | PENDIX                                 | 83         |

## 1. INTRODUCTION

# 1.1 NEED FOR THIS PROJECT

This project is microcontroller based Energy Monitor and transmission of energy through wireless to an EB substation. This project will be very much useful to EB distribution system. This project will not only useful to monitor and transfer energy, and also it can show the electricity theft.

If suppose we implement the project for a complete network in an area, that will be consuming very huge amount and it can calculate the energy transmission and energy consumption. By using the above two values we can calculate the transmission loses we are going to implement an energy meter with wireless transmission for single house.

## 1.2 OVERVIEW

In a house to calculate the energy we need the following parameters to be measured. They are voltage, current, power factor, power with power and time we can calculate the energy. By using potential transformer we can measure voltage, the potential transformer (P.T.) will give a step down AC output. That AC output will be converted into DC with the help of a rectifier. The rectifier is actually a precision rectifier. The precision rectifier will give you a pure DC output according to the input voltage. The precision rectifier is based on operational amplifiers. Then the converted Analog DC voltage will be given to an ADC.

The current transformer is used to measure the current with the help of the precision rectifier as described earlier. The only difference between voltage measurement and current measurement is we can directly measure the voltage from P.T., to measure the current. The C.T has to connect with a shunt resistor. Then the rectified current output will also be given to the ADC.

The ADC is an eight bit eight channel ADC (ADC0809). This will convert the analog voltage into digital data and those digital data will be fed into the microcontroller.

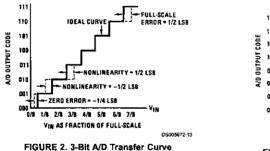

Then the microcontroller will display the voltage and current output in an LCD display. The accuracy for voltage will be 1V and the current will be 0.1 Amps. If you want to increase the accuracy just we have to increase the number of bits.

Then the power factor will be measured with the help of both C.T & P.T. The P.T & C.T output will be given to a zero crossing detector and the zero crossing detector output will be given to a logic circuit, that will detect the phase difference between voltage and current waveform. The voltage and current waveform output will be given to a timer program that will calculate the power factor.

After measuring the voltage, current, power factor we can easily calculate the power with the help of a multiplication program. Then by using power and timer we can calculate the energy.

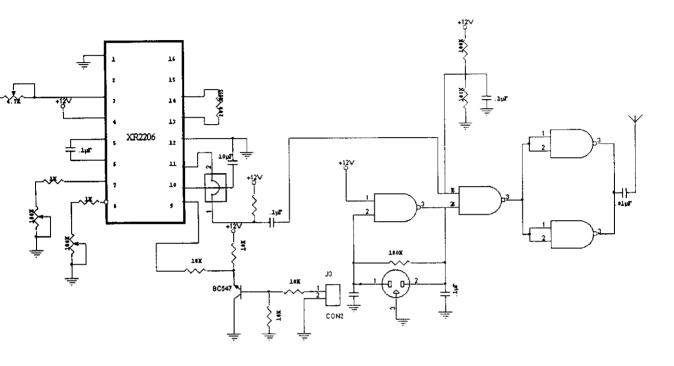

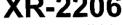

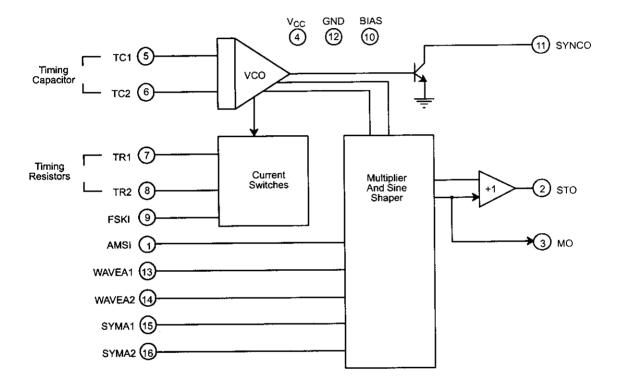

While transmitting it, we have to transmit all the above parameters, that is voltage, current, power, power factor and energy, the transmission will take place through FSK modulation. FSK modulation IC XR2206 will produce two different

frequencies for two logic levels and that will be given to an AM transmitter board. The AM output will be transmitted through air.

At the receiver end the AM demodulation take place with the help of diode demodulation technique. Then the AM demodulated output will be given to PLL, the PLL will give '1's and '0's for the frequencies. Then the TTL output will be converted into RS232 output and that will be given to a PC there we have to write a 'C++' program there we can monitor all the measured parameters.

# 1.3 BLOCK DIAGRAM

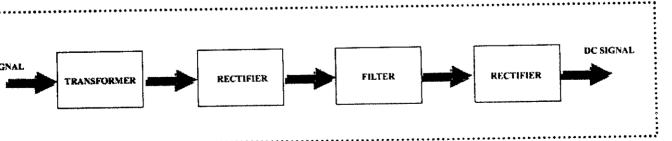

## 2. POWER SUPPLY UNIT

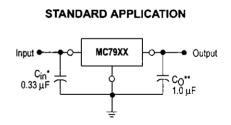

Since all electronic circuits work only with low D.C. voltage we need a power supply unit to provide the appropriate voltage supply. This unit consists of transformer, rectifier, filter and regulator. A.C. voltage typically 230V rms is connected to a transformer which steps that AC voltage down to the level to the desired AC voltage. A diode rectifier then provides a full-wave rectified voltage that is initially filtered by a simple capacitor filter to produce a DC voltage. This resulting DC voltage usually has some ripple or AC voltage variations. A regulator circuit can use this DC input to provide DC voltage that not only has much less ripple voltage but also remains the same DC value even the DC voltage varies some what, or the load connected to the output DC voltages changes.

#### LOCK DIAGRAM:

## 2.1 TRANSFORMER

A transformer is a static (or stationary) piece of which electric power in one circuit is transformed into electric power of the same frequency in another circuit. It can raise or lower the voltage in a circuit but with a corresponding decrease or increase in current. It works with the principle of mutual induction. In our project we are using step down transformer for providing a necessary supply for the electronic circuits. In our project we are using a 15-0-15 center tapped transformer.

#### 2.2 RECTIFIER

The DC level obtained from a sinusoidal input can be improved 100% using a process called full-wave rectification. It uses 4 diodes in a bridge configuration. From the basic bridge configuration we see that two diodes (say D2 & D3) are conducting while the other two diodes (D1 & D4) are in "off" state during the period t=0 to T/2. Accordingly for he negative of the input the conducting diodes are D1 & D4. Thus the polarity across the load is the same.

#### 2.3 FILTER

The filter circuit used here is the capacitor filter circuit where a capacitor is connected at the rectifier output, and a DC is obtained across it. The filtered waveform is essentially a DC voltage with negligible ripples, which is ultimately fed to the load.

## 2.4 REGULATOR

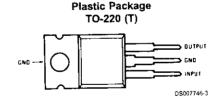

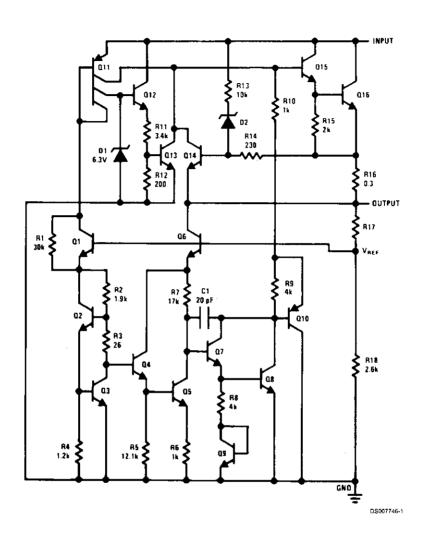

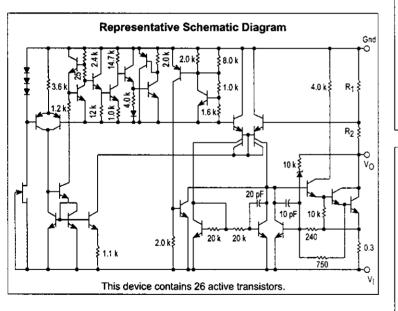

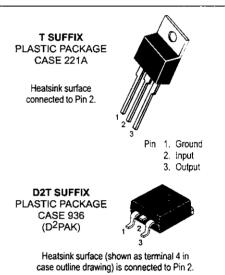

The output voltage from the capacitor is more filtered and finally regulated. The voltage regulator is a device, which maintains the output voltage constant irrespective of the change in supply variations, load variation and temperature changes. Here we use two fixed voltage regulators namely LM 7812, LM 7805 and LM7912. The IC 7812 is a +12V regulator IC 7912 is a -12V regulator and IC 7805 is a +5V regulator.

## **VOLTAGE & CURRENT TRANSFORMERS**

Transformers are used in a.c. systems for the measurement of current, voltage, power and energy. They are also used in connection with measurement of power factor, frequency and for indication of synchronism. The transformer used for measurement of current is called a "Current Transformer" or simply "C.T". Transformers used for voltage measurements are called "Voltage Transformers" or "Potential Transformers" or simply "P.T."

## 2.5 CURRENT TRANSFORMER

The current transformer is used with its primary winding connected in series with line carrying the current to be measured and, therefore, the primary current is dependant upon the load connected to the system and is not determined by the load (burden) connected on the secondary winding of the current transformer. The primary winding consists of very few turns and, therefore, there is no appreciable voltage drop across it. The secondary winding of the current transformer has larger number of turns, the exact number being determined by the turn's ratio. The ammeter, or wattmeter current coil, are connected directly across the secondary winding terminals. Thus a current transformer operates its secondary winding nearly under short circuit conditions. One of the terminals of the secondary winding is earthed so as to protect equipment and personnel in the vicinity In the event of an insulation breakdown in the current transformer.

## 2.6 POTENTIAL TRANSFORMER

Potential transformers are used to operate voltmeters, the potential coils of wattmeters and relays from high voltage lines. The primary winding of the transformer is connected across the line carrying the voltage to be measured and the voltage circuit is connected across the secondary winding.

The design of potential transformers is quite similar to that of a power transformer but the loading of a potential transformer is always small, sometimes only a few volt-amperes. The secondary winding is designed so that a voltage of 100 to 120 V is delivered to the instrument load. The normal secondary voltage rating is 110 V.

## 2.7 DIFFERENCE BETWEEN C.T. AND P.T.

There are a few differences in the operation of a current transformer and a potential transformer.

1. The potential transformer may be considered as' parallel' transformer with its secondary winding operating nearly under open circuit conditions whereas the current transformer may be thought as a 'series' transformer under virtual short circuit conditions. Thus the secondary winding of a P.T. can be open-circuited without any damage being caused either to the operator or to the transformer.

- 2. The primary winding current in a C.T. is independent of the secondary winding circuit conditions while the primary winding current in a P.T. certainly depends upon the secondary circuit burden.

- 3. In a potential transformer, full line voltage is impressed upon its terminals whereas a C.T. is connected in series with one line and a small voltage exists across its terminals. However, the C.T. carries the full line current.

- 4. Under normal operation the line voltage is nearly constant and, therefore, the flux density and hence the exciting current of a potential transformer varies only over a restricted range whereas the primary winding current and excitation of a C.T. vary over wide limits in normal operation.

# 3. PRECISION RECTIFIER AND ZERO CROSSING DETECTOR

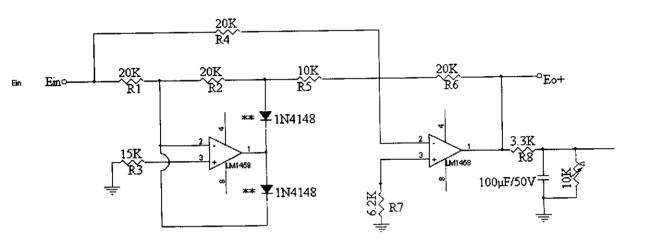

## 3.1 PRECISION RECTIFIER

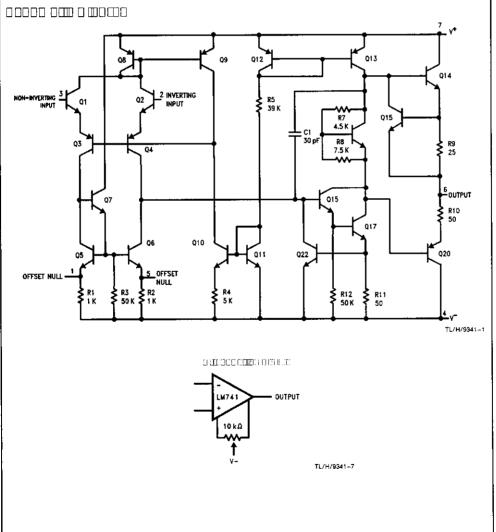

An absolute-value circuit, or full-wave precision rectifier, can be implemented by summing the output of a half-wave rectifier and its input with the proper phase and amplitude relations. Such a circuit in its basic form is shown in figure. This circuit will be the starting point for a number of other absolute-value circuits, which have evolved from this basic form.

In this circuit given below, A1 is an inverting rectifier similar to the figure. The output from A1 is added to the original input signal in A2 (a summing mixer) with the signal amplitude and phase relations shown. Negative alterations of Ein feeds A2 through 20-k $\Omega$  resistor, and E1 feed A2 through a 10-k $\Omega$  resistor. The net effect of this scaling is that, for equal amplitudes of Ein and E1, E1will provide twice as much current into the summing point.

This fact is used to advantage here, as the negative alteration of E1 produces twice the input current of that caused by the positive alternation of Ein. This causes a current of precisely half the amplitude, which E1 alone would generate due to the subtraction of Ein. It is the equivalent of having E1 feed through a  $20\text{-k}\Omega$  input receiver and having Ein non-existent during this half cycle, and it results in a positive going output at A2. During negative alterations of Ein, E1 is absent and Ein produces the alternate positive output swing that, in summation, produces the desired full-

wave rectified response. As before, operation with the opposite output polarity is possible by reversing D1 and D2.

# **Precision Rectifier Circuit**

The general –purpose dual-741 type is used in the above circuit. The relation-ships between resistors for proper circuit operation are noted in the illustration, and may be satisfied best by a single network. Note that resistor R6 can be used as an overall gain trim, or for scaling to net gains of (n) other than unity.

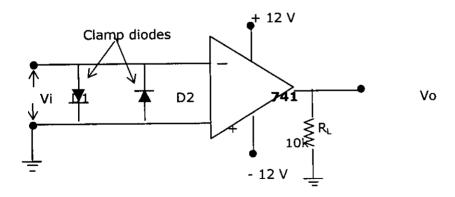

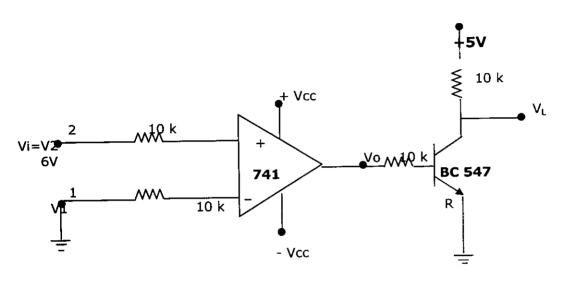

#### 3.2 ZERO CROSSING DETECTOR

An important application of comparator is the zero crossing detector or sine wave to square wave converter. The basic comparator may be used as zero crossing detector provided that  $V_R$  is set to zero. With  $V_i$  in the form of a sine wave, fig shows the output waveform. It is clear from fig that the output voltage  $V_o$  is driven into negative saturation when the input signal  $V_i$  passes through zero and goes in positive direction. Similarly when  $V_i$  passes through zero and goes in negative direction, the output voltage  $V_o$  is driven into positive saturation. This idealized waveform has vertical sides which in reality, should extend over a range of few mV of input voltage  $V_i$ .

Zero Crossing Detector

# Input and output waveforms

In some cases, the input voltage Vi may be a slowly changing waveform i.e. a signal low frequency. Then it takes Vi more time to cross zero level. Hence Vo may not be able to switch quickly from one saturation level to other saturation level. On the other hand, noise present at the op-amp input may cause Vo to fluctuate between the two saturation levels +Vsat and -Vsat, thus detecting zero crossing for noise voltages also in addition to Vi. Both the above problems may be overcome by using positive or regenerative feedback which causes the output Vo to change faster thereby eliminating the possibility of any false zero crossing due to noise voltages at the Op-amp input.

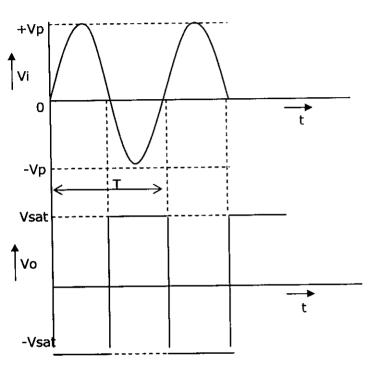

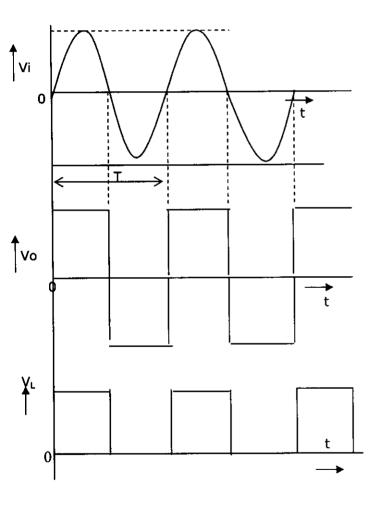

# 3.3 ZERO CROSSING DETECTOR FOR PHASE MEASUREMENT

# Zero Crossing Detector for phase angle measurement

Circuit of zero crossing detector of the figure is used for measurement of phase angle between two voltages or between voltage and current. In our project this is used to measure the phase angle between voltage and current to calculate the power factor of the circuit. Both the voltage and current are converted into square waves using the above circuit and this is given to the transistor to get only the positive half cycles. Then time interval between the voltage and current wave is measured using an NAND gate (DM 7400) which produces an output of 1 & 0. These outputs are given to 89c52 Microcontroller which with help of timer calculates the

time interval that is proportional to the phase difference between the voltage and current.

Pulse Waveforms for phase angle measurement

## 4.1 MICROCONTROLLER 89C52

## **4.11 ABOUT THE MICROCONTROLLER**

The microcontroller 89C52 is widely used in the electronic and almost all industries. Since the microcontroller controls all the operations it is essential to discuss about its architecture. The special function registers (SFRs) are described below.

#### **ACCUMULATOR**

ACC is the accumulator register. The mnemonics for accumulator specific instructions, however, refer to the accumulator simply as **A.** The accumulator is one of the important register.

#### **B REGISTER**

The B register is used during multiply and division operations. For other instructions, it can be treated as another scratch pad register.

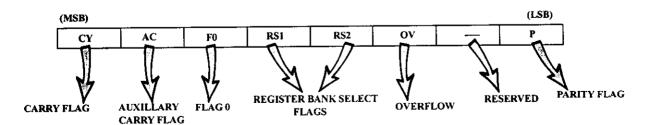

# **PROGRAM STATUS WORD (PSW)**

The program status word register contains the information regarding program status as described in the figure.

Program Status word

# 4.12 89C52 PIN DIAGRAM

|                                  | منت. |     |                       |                  |     |                                    |

|----------------------------------|------|-----|-----------------------|------------------|-----|------------------------------------|

| PORTEBITO [                      |      | l   | FIU                   | Ver              | 40  | vcc ∢sv                            |

| PORTEBITA [                      |      | 2   | P4.1                  | (रक्षिक्र स्था   | 34  | PORT 0 BET (I<br>(AEDIRESS/DATA 0) |

| MORTE BITE                       |      | 3   | P1.3                  | DPROBES          | 38  | PORTOBET (<br>(ADDRESS/DATA ()     |

| FORT FROM                        |      | 4   | P1.3                  | \D2) <b> %</b> 2 | 37  | PORT 9 BIT 2<br>(ADDRESS/DATA 2)   |

| PORT LBIT 4                      |      | 5   | PIA                   | ( 5333) Paul     | ,36 | PORTOBETS<br>(ADDRESS/DATA ))      |

| PORT FBIT 5                      |      | ó   | rl.s                  | (AD4) Pk4        | 75  | (ADDRESS/DATA/4)                   |

| PORT 1 BIT 6                     |      | 7   | å.14                  | (ADS) P4.5       | 34  | POKTOBIT 5<br>(ADDRESS/DATA 5)     |

| PORTEBILT                        |      | *   | P1.7                  | (AD6) P\$.0      | 33  | PORT 0 BIT 0<br>(ADDRESS/DATA 6)   |

| RESETINATUT                      |      | ¥   | <b>R</b> ST           | (AD7) PA7        | 32  | PORT 0 BIT 7<br>(ADDRESS/DATA 7)   |

| PORT 3 BIT 0<br>(RECEIVE DATA)   |      | ŭ1  | PAR (XRXD)            | (Vpp) E4         | 31  | EXTERNAL ENABLE                    |

| PORT J BIT I<br>TRANSMIT DATA)   |      | T.  | P3J (TXD)             | (FROG) ALE       | 34  | AUDRESS LATCH ÉNABLE               |

| FORT JETT 1<br>INTERRUPTIO       |      | 12  | P3.2 (INTV)           | PSES             | 24  | PROGRAM STROBE ENABLE              |

| PORT 3 BIT 3<br>(INTERRUPT I)    |      | ß   | PLI (NTI)             | (A15) F1.7       | 28  | HORT 2 BIT 7<br>(ADDRESS 15)       |

| PORT 3 BIT 4<br>(TIMER 4 INPLIT) |      | 14  | P3.4 (TV)             | (A14) P26        | 27  | PORT 2 BST 6<br>(ALMERERS 14)      |

| PORT 3 BIT 5<br>(TIMER ) INPUT)  |      | 1.5 | P35 (Tn               | (A13) #25        | 26  | FORT 2 BAT 5<br>(ADDRESS 13)       |

| PORT LBIT 6<br>(WRITE STROBE)    |      | Į h | P3.4 (WR)             | (A32) P2.4       | 75  | FORT 2 BIT 4<br>(ADDRESS 12)       |

| PORT 1 BUT 7<br>(READ/STROBE)    |      | 17  | PX7 ( <del>KB</del> ) | (A1D P2.3        | 24, | PORT 2 BIT 3 (ADVIRENS 11)         |

| CRYSTAL INPUT                    |      | LŔ  | XTAL i                | (410) P2.2       | 23  | FORT 2 BIT 2 - (ADDRESS 19)        |

| ryșial input 1                   |      | Ţ¥  | NEAL#                 | (A9) P2.1        | 72  | PORT 2 BIT 1.<br>(ADDRESS 9)       |

| GROUND                           |      | 19  | Ves                   | <br>(48) P2JJ    | 21. | PORT 2 BIT 0<br>(ADDIRESS 8)       |

|                                  | -    |     |                       |                  |     |                                    |

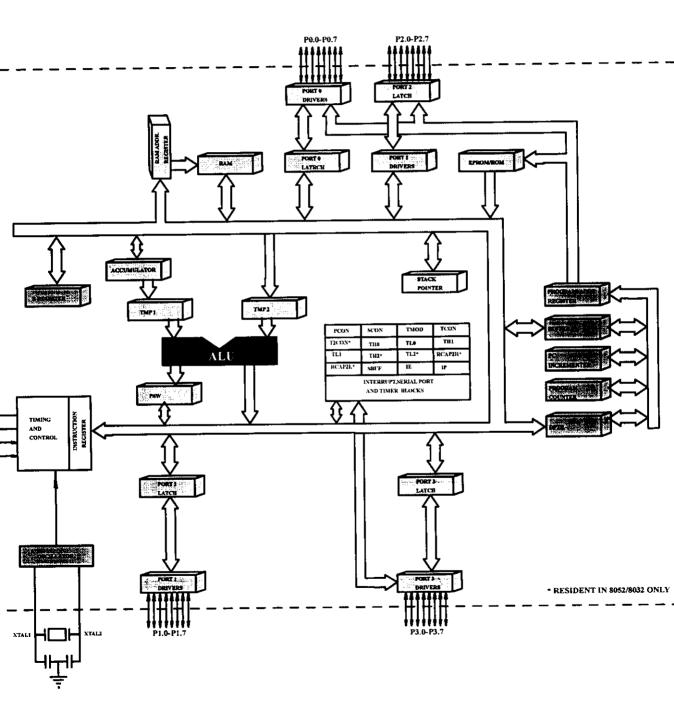

## 4.13 89C52 ARCHITECTURE

#### STACK POINTER

The stack pointer register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in on chip RAM, the stack pointer is initialized to 07H after a reset. This causes the stack to begin at location 08H.

#### **DATA POINTER**

The data pointer consists of 2 bytes which can be accessed as two separate bytes as DPH and DPL or as a single 16 bit register as a whole. It is being used to hold the 16 bit address to refer any data in the data memory.

#### **PORTS**

P0, P1, P2 and P3 are the special function registers (SFR) which are having the RAM address of 80H, 90H, A0H and B0H respectively. These registers can be bit addressable also.

#### **SERIAL DATA BUFFER**

The serial data buffer is actually two separate registers, a transmit buffer and a receive buffer register. When data is moved to SBUF, it goes to the data buffer where it is held for serial transmission. When data is moved from SBUF, it comes from the receiver.

## TIMER/COUNTER REGISTERS

The microcontroller 89C52 has two timer registers namely T0 and T1 which are 16 bit up counters. The counters are being used to monitor both external and internal events and to provide accurate delays. These registers can be accessed as single byte registers also. (TH0, TL0, TH1 and TL1).

#### **CONTROL REGISTERS**

Special function registers IP, IE, TMOD, TCON, SCON and PCON content control and status bit for the interrupt system, the timer/counter, and the serial ports.

#### **SERIAL INTERFACE**

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive buffered, meaning that it can commence the reception of second byte before a previously received byte has been read from the receive register. The serial port receive and transmit register are both accessed at special function register SBUF. Writing from SBUF loads the transmit register, and reading SBUF accesses a physically separate register. The serial port can operate in following four modes as shown in figure which can be controlled by SCON register.

| SM0 | SM1 | MODE | DESCRIPTION                      |

|-----|-----|------|----------------------------------|

| 0   | 0   | 0    | Shift register : baud = f/12     |

| 1   | 1   | 1    | 8 bit UART : baud = variable     |

| 0   | 0   | 2    | 9 bit UART : baud = f/32 or f/64 |

| 1   | 1   | 3    | 9 bit UART : baud = variable     |

#### Four serial Modes Of 89c52

#### **INTERRUPTS**

The 89c52 microcontroller consists of five interrupt sources in which three are internal and two are external. The two external interrupts are INTO and INT1 which can be level activated or transition activated, depending on bits of ITO and IT1 in register TCON. The other three interrupts, which are internal, are the Timer1, Timer2 interrupts and the serial port interrupt.

The Timer0 and Timer1 interrupts are generated by TF0 and TF1, which are set by a rollover in their respective timer/counter registers. The serial port interrupt is generated by the logical OR of RI and TI.

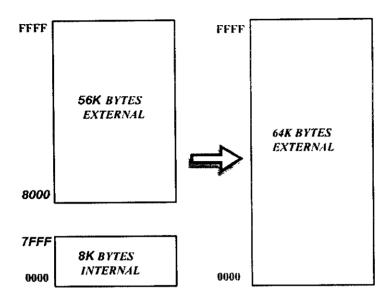

# 4.14 MEMORY ORGANISATION

#### **PROGRAM MEMORY**

The 89c52 has separate address spaces for program and data memory. The program memory can be up to 64K bytes long. The lower 8K can reside on-chip. The figure shows the map of the 89c52 program memory.

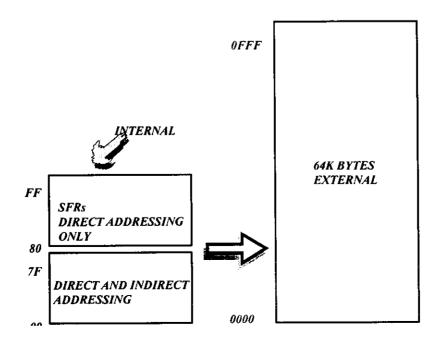

## **DATA MEMORY**

The 89c52 has 128 bytes of on-chip RAM, plus a number of Special Function Registers (SFRs). The lower 128 bytes of RAM which can be accessed by both direct and indirect addressing can be divided into three segments as,

1. Register Banks 0-3, 2. Bit Addressable Area, 3. Scratch Pad Area.

# 4.2 ANALOG TO DIGITAL CONVERTER (ADC0809)

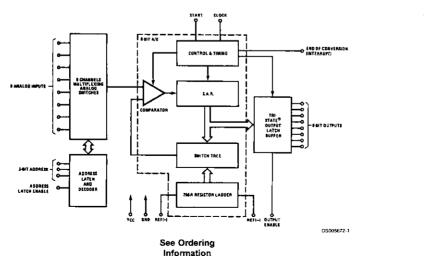

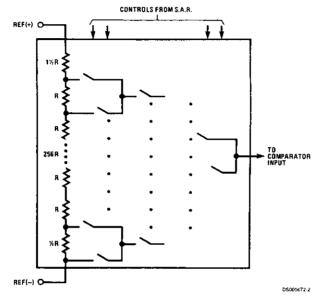

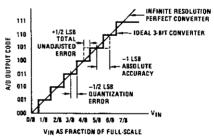

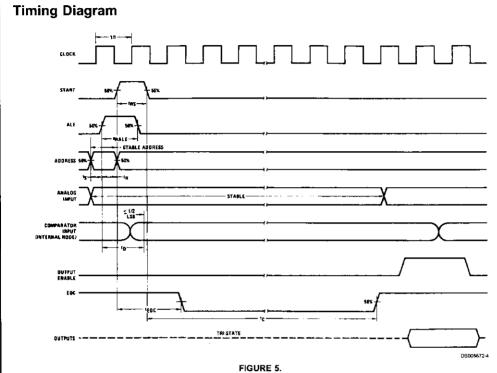

The ADC0809 data acquisition component is a monolithic CMOS device with an 8-bit analog-to-digital converter, 8-channel multiplexer and microprocessor compatible control logic. The 8-bit A/D converter uses successive approximation as the conversion technique. The 8-channel multiplexer can directly access any of 8-single-ended analog signals. The device eliminates the need for external zero and full-scale adjustments. Easy interfacing to microprocessors is provided by the latched and decoded multiplexer address inputs and latched TTL TRI-STATE outputs. The ADC0809 offers high speed, high accuracy, minimal temperature dependence, excellent long-term accuracy and repeatability, and consumes minimal power. These features make this device ideally suited to applications from process and machine control to consumer and automotive applications.

The device contains an 8-channel single-ended analog signal multiplexer. A particular input channel is selected by using the address decoder. Table below shows the input states for the address lines to select any channel. The address is latched into the decoder on the low-to-high transition of the address latch enable signal.

| SELECTED       | ADDRESS LINES |   |   |  |

|----------------|---------------|---|---|--|

| ANALOG CHANNEL | Ç             | В | Α |  |

| IN0            | L             | L | L |  |

| IN1            | L             | L | Н |  |

| IN2            | L             | Н | L |  |

| IN3            | L             | Н | Н |  |

| IN4            | Н             | L | L |  |

| IN5            | Н             | L | Н |  |

| IN6            | H             | Н | L |  |

| IN7            | Н             | Н | Н |  |

In our project the analog inputs namely Voltage and Current are to be converted in to digital outputs in order to access by the 89c52 microcontroller. At regular intervals one of the inputs is selected and converted to digital 8-Bit output data. The converted digital output is given to 89c52 through port 0.

The clock at which this ADC0809 is to be operated is 750 KHz. This clock signal comes from the external crystal oscillator operating at a frequency of 12 MHz. This 12 MHz clock is used for 89c52 microcontroller. By using counter this clock frequency of 12 MHz is divided to obtain 750 KHz and given as clock input for ADC0809. During each clock period the conversion take place.

Pin details of ADC0809 is shown below

Pin diagram of ADC0809

## 4.3 DM74LS138 DECODER

These Schottky-clamped circuits are designed to be used in high performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these decoders are usually less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible. The LS138 decodes one-of-eight lines; based upon the conditions at the three binary select inputs and the three enable inputs.

The decoder is used to select 8255-PPI and ADC0809 depending upon the address lines input of 89c52. By default the output of the decoder is high. As the chip is selected the output turns low which selects either ADC or 8255.

# 4.4 DM7414- HEX INVERTER WITH SCHMITT TRIGGER INPUTS

This device contains six independent gates each of which performs the logic INVERT function. Each input has hysteresis which increases the noise immunity and transforms a slowly changing input signal to a fast changing, jitter free output.

The function is given by Y=A'

| Input | Output |  |

|-------|--------|--|

| A     | Y      |  |

| L     | H      |  |

| H     | L      |  |

H=High Logic Level L = Low Logic Level

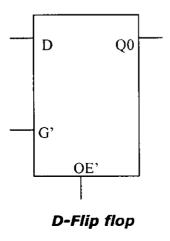

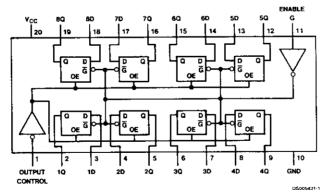

# 4.5 DM74LS373-TRANSPARENT LATCH

These 8-bit registers feature 3-STATE outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers. The eight latches of the DM54/74LS373 are transparent D-type latches meaning that while the enable (G) is high the Q outputs will follow the data (D) inputs. When the enable is taken low the output will be latched at the level of the data that was set up.

#### **Function Table**

| Output<br>Control | Enable<br>G | D        | Output |

|-------------------|-------------|----------|--------|

| L                 | Н           | Н        | Н      |

| L                 | Н           | L        | L      |

| L                 | L           | X        | Į Q0   |

| ! н \             | Χ           | <b>X</b> | j Z    |

H=High Level (Steady State), L = Low Level (Steady State), X = Don't Care

Z = High Impedance State, Q 0 = The level of the output before steady-state input conditions were established.

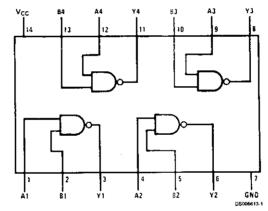

## 4.6 74LS393 COUNTER

The **74LS39** is actually dual 4-bit binary ripple counter. It consists of two 4-bit binary counters. There are separately two master resets to clear each 4-bit counter separately. Each counter has separate clock so that they can operate independently. The counters are triggered by a HIGH-to-LOW transition of the clock inputs.

We are using a master crystal of generating 12MHz signal for the microcontroller and our ADC operates at the 750 KHz. There is a requirement of generating 750 KHz frequency signal for ADC using the same crystal. This can be achieved by applying the master crystal signal to this counter and by loading the counter with proper count value before ADC begin operations.

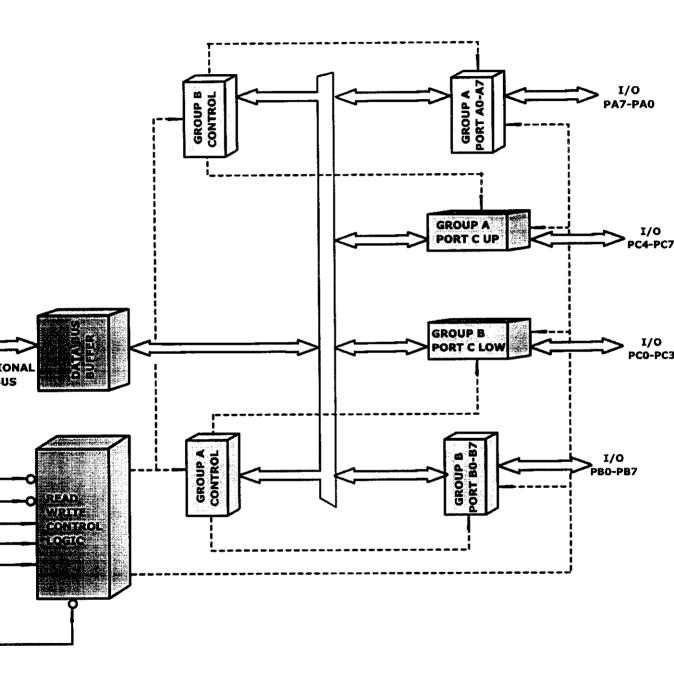

# 4.6 8255-PROGRAMMABLE PERIPHERAL INTERFACE

#### 4.61 DESCRIPTION

The 8255 is general purpose I/O interfacing device. It provides 24 I/O lines organized as three 8-bit I/O ports labeled A, B, and C. It is a very versatile device in the means that this can be programmed to look like three simple I/O ports (mode0), two handshaking I/O ports (mode1), or a bidirectional I/O port with five handshaking signals (mode2). There is also a bit reset/set mode that allows individual bits of port C to be set or reset for control purposes. Pin definitions and a block diagram are provided in the following figures.

#### PIN NAMES

| D7-D0                                 | DATA BUS (BIDIRECTIONAL) |

|---------------------------------------|--------------------------|

| RESET                                 | RESET INPUT              |

| CS                                    | CHIP SELECT              |

| RD                                    | READ INPUT               |

| WR                                    | WRITE INPUT              |

| A0,A1                                 | PORT ADDRESS             |

| PA7-PA0                               | PORT A (BIT)             |

| PB7-PB0                               | PORT B (BIT)             |

| PC7-PC0                               | PORT C (BIT)             |

| Vcc                                   | +5 VOLTS                 |

| GND                                   | 0 VOLTS                  |

| · · · · · · · · · · · · · · · · · · · |                          |

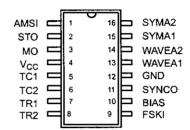

4.62 PIN DIAGRAM

**PIN DETAILS**

## 4.63 BLOCK DIAGRAM

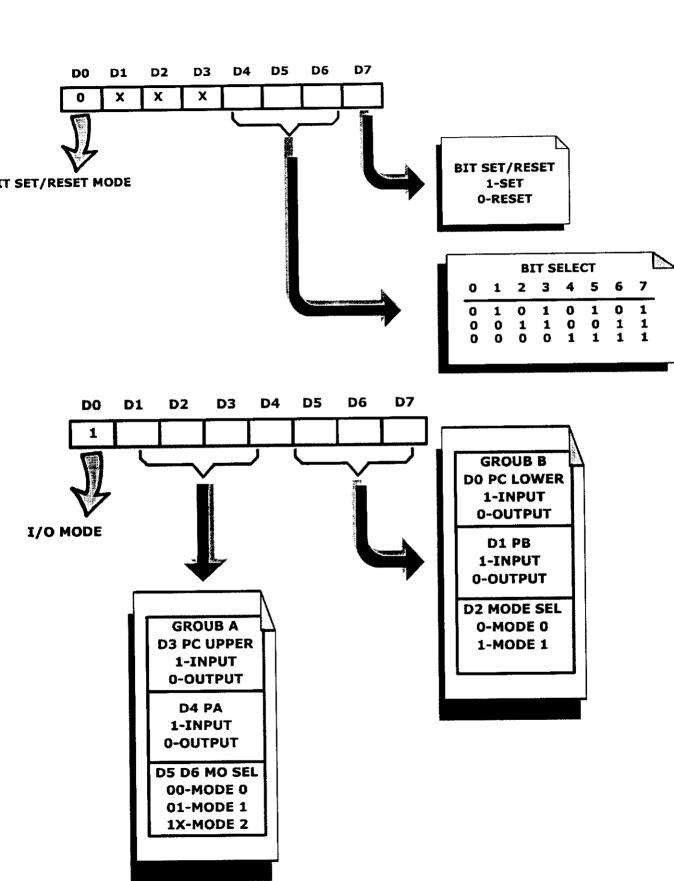

#### **CONTROL WORD**

As mentioned above the programmable peripheral interface 8255 can be operated in three different modes as well as bit SET/RESET mode. The mode of operation can be controlled by a word, which is going to be stored in control register of the 8255, called as control word. The format of the control word is shown below.

## MODE 0 (BASIC I/O)

When there is no need for conditional or handshaking I/O mode 0 can be selected. In this mode of operation all the ports are simply treated as I/O ports.

## MODE 1 (STROBED I/O)

This mode of operation is mainly intended for handshaking and interrupt driven I/O interfaces. Here, ports A and B are programmed as data ports and pot C is programmed to carry status signals.

## MODE 2 (STROBED BIDIRECTIONAL I/O)

When operated in mode 2, port A of the 8255 becomes a bidirectional data port supported by five handshaking signals. Port B can operate in mode 0 or mode 1.

## **BIT SET/RESET MODE**

When bit 7 of the 8255 control word is a 0, the bit set/reset mode is active. In this mode any one bit of port C can be set to a logic 1 or reset to a logic 0. Only one bit can be set or reset at a time. This feature of 8255 can be taken advantage of to generate strobe signals.

# **5. AM TRANSMITTER**

### **5.1 FSK GENERATOR**

In digital data communication, binary code is transmitted by shifting a carrier frequency between two preset frequencies. This type of transmission is called frequency shift keying technique. A 555 timer in astable mode can be used to generate FSK signals. When the input is high, transistor Q is cutoff and 555 timer works in the normal astable mode of operation. The frequency of the output waveform is given by

$$F0 = 1.45/(RA + 2RB) C$$

When the input is low  ${\tt Q}$  goes on and connects the resistance RC across Ra. The output frequency is given by

$$F0 = 1.45/((RA|RC)+2RB)C$$

The resistance is used to get the desired output frequency.

Frequency shift keying (FSK) is the mostly used method for transmitting digital data over telecommunications links. In order to use FSK a modulator-demodulator (modem) is needed to translate digital 1's and 0's into their respective frequencies and back again.

In FSK modulation, the carrier frequency is shifted in steps (or) levels corresponding to the levels of the digital modulating signal. In case of binary signal, two carrier frequencies are used, one was corresponding to binary '0' and another to binary '1'.

#### **TIMER**

The 555 timer used in the above circuit is highly stable for generating time delays or oscillations. A single 555 timer can provide a time delay ranging from microseconds to hours where as counter timer can have maximum timing range of days. The 555 timer can be used with supply voltage in the range of +5volts to +18volts and can drive load up to 200milli ampere. It is compatible with both TTL and CMOS logic circuits. Because of wide range of supply voltage the 555timers are versatile and easy to use in various applications. The various applications include oscillator, pulse generator, ramp generator, square wave generator, monoshot multivibrator, burglar alarm etc. In our circuit, astable mode of 555 timers is used.

#### **MODULATION**

The purpose of a communication is the source and user being physically separate from each other. To do this, the transmitter modifies the message signal into a suitable form for transmission over the channel. This modification is achieved by a process known as modulation, which involves varying some parameters of a carrier wave in accordance with the message signal. The receiver recreates the original message signal from a degraded version of the transmitted signal after propagation through the channel.

A process known as demodulation, which is a reverse process of modulation used in the transmitter, achieves the recreation. However owing to the unavoidable presence of noise and distortion in the received signal, we find that the receiver cannot recreate the original message signal exactly. The type of modulation scheme used influences the resulting degradation in the overall system performance. Specifically we find that some modulation schemes are less sensitive to the effects of noise and distortion than others.

## **5.2 AMPLITUDE MODULATION**

The amplitude of the carrier wave is varied in a ccordance with the amplitude of the modulating signal. Consider a sinusoidal carrier wave c (t)\_ defined by,

$$C(t) = Ac Cos (2*Pi*Fc*t+\phi),$$

where Ac is the carrier amplitude and Fc is the carrier frequency. We have assumed that the phase of the carrier wave is zero for specification of the message. The source of the carrier wave c (t) is physically independent of the source responsible for generating m (t). An amplitude-modulated wave may thus describe, in its most general form, as a function of time.

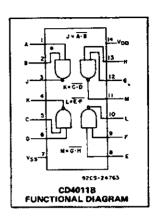

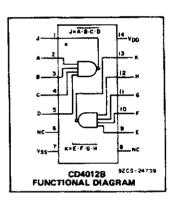

In the circuit shown, schmitt trigger NAND gate CD4011 is used. The carrier frequency is generated using the ceramic filter of value 10.7 MHz. The resistor R1 and R2 provide the necessary biasing. The modulated output is than transmitted through the antenna after passing through a capacitor. The antenna used is of aerial type. In our project the transmitted frequency is 5.5 MHz. The maximum distance to

Which we can transmit is around 30ft to 40ft, the distance to which it can be transmitted can be improved further by providing some amplification at the output of the amplitude modulation circuit.

AM Transmitter

## 4.3 CD4011-CMOS NAND GATES

The XR2206 IC generates two frequencies namely 1200 Hz and 1000 Hz representing the digital data 1 and 0 respectively. These generated frequencies get attenuated while transmitting. In order to avoid that, we are padding up those frequencies with the high frequency carrier of 5.5 MHz. This transmission is carried out using the CD4011- NAND GATES where the inputs are 5.5MHz carrier and one of the two low frequency signals. The presence of logic 1 is represented as 5.5MHz carrier output and logic 0 as zero Hz signal.

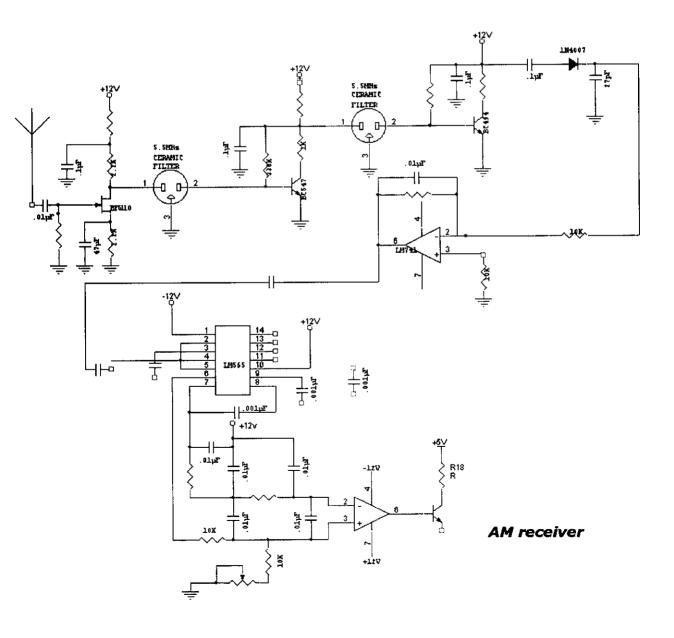

## **6.AM RECEIVER**

The encoded message has to now be decoded. The encoded message is received by receiving antenna and than given to demodulator circuit. This is then given to a DFSK circuit where 0's and 1's are separated out by using carrier at two different frequencies. Then the output is given to a P.C where message is decoded using the same algorithm as in encrypment process and the original message is taken out.

# **6.1 ENVELOPE DETECTOR**

An envelope detector is a simple and yet highly effective device that is well suited for the demodulation of a narrow band AM wave, for which the percentage modulation is less than 100%. Ideally, an envelope detector produces an output signal that follows the envelope of the input signal waveform.

Envelope detector consists of a diode and a resistor-capacitor filter. The operation is as follows. On the positive half-cycle of the input signal, the diode is forward-biased and the capacitor C charges up rapidly to the peak value of the input signal. When the input signal falls below this value, the diode becomes reverse biased and the capacitor C discharges slowly to the load resistor RI. The discharging process continues until the next positive half cycle. When the input signal becomes greater than the voltage across the capacitor, the diode conducts again and the process is repeated. Thus the demodulation is carried out. In our circuit we are using 0A79 diode.

In digital data communication and computer peripheral, binary data is transmitted by means of a carrier frequency, which is shifted between two preset frequencies. This type of data transmission is called frequency shift keying (FSK) technique. The binary data can be retrieved using FSK demodulators at the receiving end.

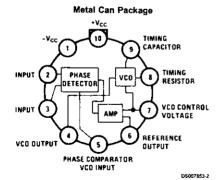

The 565 PLL is a very useful as a FSK demodulator. As the signal appears at the input, the loop locks to the input frequency and tracks it between the two frequencies with a corresponding and the DC shift at the output. A three-stage filter removed the carrier component and the output signal is made logic compatible by the voltage comparator.

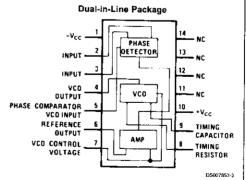

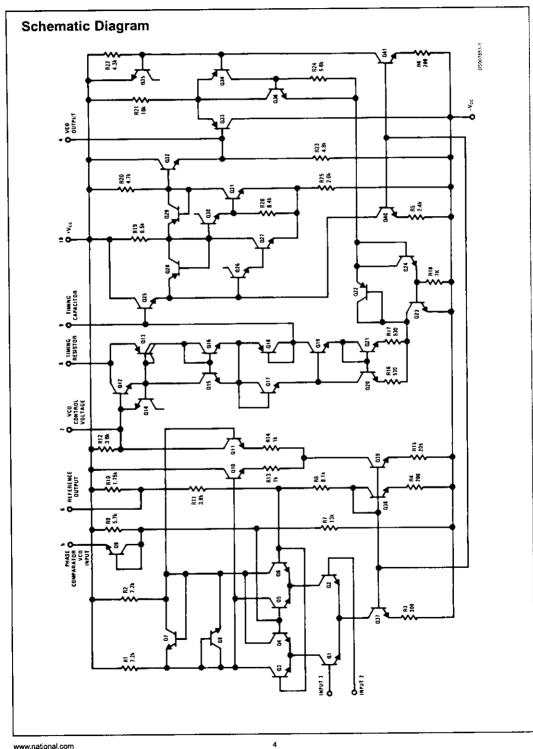

## 6.2 IC PLL 565

The phase detector of this PLL is comprised of differential amplifier pairs provided with current sink bias source. The output voltage phase detector is limited by diodes to maximum of  $\pm 0.7$ V.

This limiting action helps to minimize the effect of high amplitude noise pulses and other transient effects on the operation of the PLL. The phase detector has a balanced output and is supplied to the differential amplifier pair, which serves an amplifier stage in amplifying the phase detector; output a single ended output is taken from this stage from across the load resistor R1 and connected internally to the VCO.

Connection of an external capacitor C between Pin 7 and ground will produce a first order low-pass (lag) network. A capacitor C and a resistor R2 connected in series between pin 7 and ground will result in lag lead network.

The VCO consists of a voltage controlled current source, which supplies equal magnitude of charging and discharging currents to an externally connected (pin 9) timing capacitor CO. A timing resistor is connected between pin8 and positive power supply. The rest of the VCO circuit is Schmitt trigger with a differential amplifier output circuit. This controls the turn-on and turn-off for the switching action of the current source for the charging and discharging.

# MICROCONTROLLER PROGRAMMING

```

; #pragma src;

#include<reg51.h>

#include<math.h>

void htdt();

void dist();

void cal();

void disr();

void htdp();

void htdp1();

void ser_init();

void ser_out();

void ser_out0();

void ser_out1();

void ser_out2();

//void serout();

void lcd_init();

void lcd_dis(unsigned char*,unsigned char);

void del();

void delay();

void read();

void write();

void adc0();

void htd0();

; void dis0();

void adc1();

void htd1();

; void dis1();

void power();

void htd2();

void dis2();

void powf();

void htd3();

void dis3();

sbit pul=P3^2;

pdata unsigned char ch0 _at_ 0x08;

pdata unsigned char ch1 _at_ 0x09;

pdata unsigned char soc _at_ 0x10;

pdata unsigned char_porta _at_ 0x18;

pdata unsigned char portb _at_ 0x19;

pdata unsigned char portc _at_ 0x1a;

pdata unsigned char cwr _at_ 0x1b;

idata unsigned char a0,b0,c0,d0,a1,b1,c1,d1,a2,c2,e2,f2,g2,h2,i2,j2;

idata unsigned char i,j,x,dat0,dat1,ser_data;

idata unsigned int s,b2,d2;

unsigned int mask, mask2;

unsigned char mask1,data2;

//float pow_f,pow,dat;

unsigned int pow_f,pow,dat;

idata\ unsigned\ int\ countr=0, ix, b1p, d1p, f1p, h1p, bp, dp, fp, hp, reg=0, tt;

unsigned long av;

//float ttemp1,ttemp2,count1,energy=0,date;

unsigned int ttemp1,ttemp2,count1,energy=0,date;

idata unsigned char a1p,c1p,e1p,g1p,ap,cp,ep,gp,l;

idata unsigned int be,de,fe;

idata unsigned char ae,ce,ge,he,ee;

idata unsigned int bt, dt, ft;

idata unsigned char at,ct,gt,ht,et;

; main()

RSEG ?PR?main?KCT_PF

main:

USING

; SOURCE LINE # 59

; {

; SOURCE LINE # 60

; lcd_init();

; SOURCE LINE # 61

LCALL

Icd_init

; porta=0x80;

; SOURCE LINE # 62

; read();

```

```

; SOURCE LINE # 63

LCALL

L?0059

; delay();

; SOURCE LINE # 64

LCALL

delay

",16);

; lcd_dis(" PARAMETER

; SOURCE LINE # 65

R2,#HIGH (?SC_0)

MOV

MOV

R1,#10W (?SC_0)

LCALL

L?0062

; porta=0xc0;

; SOURCE LINE # 66

RO, #LOW (porta)

MOV

MOV

A,#GCOH

MOVX

@RO,A

; read();

; SOURCE LINE # 67

LCALL

read

; delay();

; SOURCE LINE # 68

LCALL

DISPLAY

; lcd_dis("

",16);

; SOURCE LINE # 69

MOV

R3,#0FFH

MOV

R2,#HIGH (?SC_17)

MOV

R1, #LOW (?SC_17)

MOV

R5,#010H

LCALL

_lcd_dis

; del();

; SOURCE LINE # 70

LCALL

del

; del();

; SOURCE LINE # 71

LCALL

del

; del();

; SOURCE LINE # 72

LCALL

del

; del();

; SOURCE LINE # 73

LCALL

; del();

; SOURCE LINE # 74

LCALL

del

; del();

; SOURCE LINE # 75

LCALL

; porta=0x80;

; SOURCE LINE # 76

; read();

; SOURCE LINE # 77

LCALL

L?0059

; delay();

; SOURCE LINE # 78

LÇALL

delay

; lcd_dis("

",16);

; SOURCE LINE # 79

LCALL

L?0061

; porta=0xc0;

; SOURCE LINE # 80

MOV

R0,#LOW (porta)

MOV

A,#0C0H

MOVX

@R0,A

; read();

; SOURCE LINE # 81

LÇALL

read

; delay();

; SOURCE LINE # 82

LCALL

delay

",16);

; lcd_dis("

; SOURCE LINE # 83

LCALL

L?0061

; EA=1;

: SOURCE LINE # 84

$ETB

EΑ

; TH0=0x00;

: SOURCE LINE # 85

```

```

CLR

MOV

TH0.A

; TL0=0x00;

; SOURCE LINE # 86

TL0,∧

MOV

; TMOD=0x01;

; SOURCE LINE # 87

TMOD,#01H

MOV

; ET0=1;

; SOURCEOLINE # 88

SETB

ET0

; TR0=1;

; SOURCE LINE # 89 TRO

SETB

?C0001:

; while(1)

; SOURCE LINE # 91

; SOURCE LINE # 92

; ser_init();

; SOURCE LINE # 93

LCALL

ser_init

; ser_data=0xff;

; SOURCE LINE # 94

MOV

RO,#LOW (ser_data)

MOV

@RO, #OFFH

; ser_out();

; SOURCE LINE # 95

LCALL

ser_out

; for(ix=1;ix<=50;ix++)

; SOURCE LINE # 97

MOV

RO,#LOW (IX)

@RO, # 00H

MOV

INC

R0

@R0,#01H

MOV

?C0003:

; {

; SOURCE LINE # 98

?C0006:

; while(pul==0);

; SOURCE LINE # 99

JNB

pul,?C0006

?C0008:

; while(pul==1);

; SOURCE LINE # 100

JB pul,?C0008

?C0010:

; while(pul==0);

; SOURCE LINE # 101

JNB

pul,?C0010

;

; bb:

; SOURCE LINE # 103

?main?bb:

; if(pul==1)

; SOURCE LINE # 104

pul,?C0005

JNB

; {

; SOURCE LINE # 105

; countr=countr+1;

; SOURCE LINE # 106

RO,#LOW (countr+01H)

MOV

@R0

INC

MOV

A,@R0

DEC

R0

JNZ

?main?bb

INC

@R0

?C0054:

; goto bb;

; SOURCE LINE # 107

?main?bb

SJMP

; }

; SOURCE LINE # 108

; }

```

```

0

; SOURCE LINE # 109

?C0005:

MOV

R0,#LOW (ix+01H)

INC

@R0

MOV

A,@80

R0

DEC

?C0055

JNZ

INC

@R0

?C0055:

MOV

R0,#: OW (ix+01H)

A,@R0

MOV

XRL

A,#033H

D€C

R0

A,@R0

ORL

2C0003

JNZ

?C0004:

; count1=countr/50;

; SOURCE LINE # 110

MOV

RO,#I.OW (countr)

A,@R0

MOV

MOV

R6,A

RO

INC

MOV

A,@R0

R7,A

MOV

R4,#00H

MOV

MOV

R5,#032H

?C?UIDIV

LCALL

MOV

count1,R6

MOV

count1+01H,R7

; cal();

; SOURCE LINE # 111

LCALL

; if(ttemp1>10000)

; SOURCE LINE # 112

SETB

A,ttemp1+01H

MOV

SUBB

A,#010H

MOV

A,ttemp1

SUBB

A,#027H

JC ?C0014

;{

; SOURCE LINE # 113

; ttemp1=10000;

; SOURCE LINE # 114

ttemp1,#027H

MOV

MOV

ttemp: +01H,#010H

; ttemp2=1;

; SOURCE LINE # 115

MOV

ttemp2,#00H

ttemp2+01H,#01H

MOV

; }

; SOURCE LINE # 116

?C0014:

; if(ttemp1<2000)

; SOURCE LINE # 117

C

CLR

MOV

A,ttemp1+01H

SUBB

A,#0D0H

MOV

A,ttemp1

A.#071-

SUBB

?C0015

JNC

; SOURCE LINE # 118

; ttemp1=10000;

; SOURCE LINE # 119

ttemp1,#027H

MOV

ttemp1+01H,#010H

MOV

; ttemp2=1;

; SOURCE LINE # 120

ttemp2,#00H

MOV

ttemp2+01H,#01H

MOV

; }

; SOURCE LINE # 121

?C0015:

; tt=ttemp1;

```

; SOURCE LINE # 122

```

RO,#LOW (tt)

MOV

MOV

@R0,ttemp1

ŔΟ

INC

@R0,ttemp1+01H

MOV

; htdp();

; SOURCE LINE # 123

LCALL

htdp

; disr();

; SOURCE LINE # 124

LCALL

disr

; mask=tt;

; SOURCE LINE # 125

MOV

R0, #LOW (tt)

MOV

A,@R0

MOV

mask,A

INC

R0

A,⊚R0

MOV

MOV

mask +01H,A

; ser_out2();

; SOURCE LINE # 126

LCALL

ser_out2

adc0();

; SOURCE LINE # 128

LCALL

adc0

; htd0();

; SOURCE LINE # 129

LCALL

; dis0();

; SOURCE LINE # 130

LCALL.

dis0

; del();

; SOURCE LINE # 131

LCALL

del

; ser_out0();

; SOURCE LINE # 132

LCALL

ser_out0

adc1();

; SOURCE LINE # 134

LCALL

; htd1();

; SOURCE LINE # 135

LCALL

htd1

; dis1();

; SOURCE LINE # 136

LCALL

dis1

; del();

; SOURCE LINE # 137

LCALL

; ser_out1();

; SOURCE LINE # 138

LCALL

ser_out1

;

; del();

; SOURCE LINE # 140

LCALL

; del();

; SOURCE LINE # 141

del

LCALL

; del();

; SOURCE LINE # 142

LCALL

del

; del();

; SOURCE LINE # 143

LCALL

del

; del();

; SOURCE LINE # 144

LCALL

; del();

; SOURCE LINE # 145

LCALL

; del();

; SOURCE LINE # 146

LCALL

del

; del();

```

```

; SOURCE LINE # 147

LCALL

dei

power();

; SOURCE LINE # 149

LCALL

power

; powf();

; SOURCE LINE # 150

LCALL

iwoq

; htd2();

; SOURCE LINE # 151

LCALL

; dis3();

; SOURCE LINE # 152

dis3

LCALL

; mask=dat;

: SOURCE LINE # 153

MOV

mask,dat

MOV

mask+01H,dat+01H

; ser_out2();

; SOURCE LINE # 154

LCALL

ser_out2

date=energy;

; SOURCE LINE # 156

MOV

date, energy

date+01H,energy+01H

MOV

; htd3();

; SOURCE LINE # 157

LCALL

htd3

; dis2();

; SOURCE LINE # 158

LCALL

dis2

; mask=date;

; SOURCE LINE # 159

MOV

mask,date

mask + 01H,date+01H

MOV

; ser_out2();

; SOURCE LINE # 160

LCALL

ser_out2

; del();

; SOURCE LINE # 161

LCALL

; del();

: SOURCE LINE # 162

LCALL

; del();

; SOURCE LINE # 163

LCALL

del

; del();

; SOURCE LINE # 164

LCALL

del

; del();

; SOURCE LINE # 165

LCALL

;}

; SOURCE LINE # 167

⊔MP

?C0001

; END OF main

CSEG

AT 0000BH

⊔MP

timer0

;}

; void timer0(void) interrupt 1

• RSEG ?PR?timer0?KCT_PF

USING

timer0:

PUSH

ACC

PUSH

В

PSW

PUSH

PSW, # 00H

MOV

PUSH

AR0

```

```

PUSH

AR4

PUSH

AR5

PUSH

AR6

AR7

PUSH

USING

0

; SOURCE LINE # 170

; unsigned char reg1;

TR0=0;

; SOURCE LINE # 173

CLR

TR0

; reg1++;

; SOURCE LINE # 174

INC

reg1?140

; if(reg1==0x10)

; SOURCE LINE # 175

A,reg!?140

MOV

CUNE

A,#010H,?C0017

; {

; SOURCE LINE # 176

reg1=0;

; SOURCE LINE # 177

MQV

reg1?140,#00H

energy=energy+(pow_f/3600);

; SOURCE LINE # 178

MOV

R6,pow f

R7,pow_f+01H

MOV

MOV

R4,#0EH

R5 #010H

MOV

LCALL

?C?UIDIV

MOV

A,R/

ADD

A,energy+01H

MOV

energy+01H,A

MOV

A,R6

ADDC

A,energy

MOV

energy,A

; }

; SOURCE LINE # 179

?C0017:

; TH0=0x00;

; SOURCE LINE # 180

MOV

TH0,#00H

; TL0=0x00;

; SOURCE LINE # 181

MOV

TL0,#00H

; TR0=1;

; SOURCE LINE # 182

SETB

TRO

; }

; SOURCE LINE # 183

POP

AR /

POP

AR6

POP

AR5

POP

AR4

POP

ARC

PSW/

POP

POP

В

POP

ACC

RÉTI

; END OF timer0

; void ser_init()

RSEG ?PR?ser_init?KCT_PF

ser_init:

USING

; SOURCE LINE # 186

; {

; SOURCE LINE # 187

; TH1=0x72;

; SOURCE LINE # 188

MOV

TH1,#072H

; TMOD=0x20;

; SOURCE LINE # 189

```

```

MOV

TMOD,#020H

; TR1=1;

; SOURCE LINE # 190

SETB

; delay();

; SOURCE LINE # 191

delay

LCALL

; SCON=0x40;

; SOURCE LINE # 192

<sup>⊖</sup> MOV

SCON, #040H

; }

; SOURCE LINE # 193

RET

; END OF ser_init

; void ser_out()

RSEG ?PR?ser_out?KCT_PF

ser_out:

USING

0

; SOURCE LINE # 195

; {

; SOURCE LINE # 196

; SBUF=ser_data;

; SOURCE LINE # 197

پ MO۷ پ

RO,#LOW (ser_data)

MOV

A,@RO

MOV

SBUF, A

; delay();

; SOURCE LINE # 198

LCALL

delay

; SCON=0x40;

; SOURCE LINE # 199

MOV

SCON, #040H

;}

; SOURCE LINE # 200

RET

; END OF ser_out

; void adc0()

RSEG ?PR?adc0?KCT PF

adc0:

USING

; SOURCE LINE # 202

; {

; SOURCE LINE # 203

; x=ch0;

O

; SOURCE LINE # 204

MOV

RO,#LOW (ch0)

A,@R0

MOVX

MOV

RO,#LOW(x)

MOV

@R0,A

; delay();

; SOURCE LINE # 205

LCALL

delay

; dat0=soc;

; SOURCE LINE # 206

MOV

RO,#LOW (soc)

MOVX

A,@R0

R0,≈LOW (dat0)

MOV

MOV

@R0,A

, }

; SOURCE LINE # 207

RET

; END OF adc0

; void htd0()

RSEG ?PR?htd0?KCT PF

htd0:

USING

```

; 50 RCE LINE # 209

```

; {

; SOURCE LINE # 210

; a0=dat0/0x64;

; SOURCE LINE # 211

MOV

R0,#LOW (dat0)

A,@R0

MOV

MOV

R7 A

∪ MOV

B,#064H

DIV

AB

MOV

R0,#LOW (a0)

MOV

@RC,A

; b0=dat0%0x64;

; SOURCE LINE # 212

MOV

A,R7

MOV

B,#064H

DIV

AΒ

MOV

R0,#10W (b0)

MOV

@R0,8

; c0=b0/0x0a;

; SOURCE LINE # 213

MQV

A,@R0

MOV

ŔŹ,∧

MOV

B,#0Aii

DIV

AΒ

R0, = LOW (c0)

MOV

MOV

@R0,A

; d0=b0%0x0a;

; SOURCE LINE # 214

MOV

A,R7

B,#CAH

MOV

AΒ

DIV

R0,#LOW (d0)

MOV

MOV

@R0,B

; }

; SOURCE LINE # 215

RET

; END OF htd0

;

; void dis0()

RSEG ?PR?dis0?KCT PF

dis0:

USING

; SOURCE LINE # 217

: {

; SOURCE LINE # 218

; porta=0x89;

; SOURCE LINE # 219

MOV

R0,#LOW (porta)

MOV

A,#089H

MOVX

@R0,A

; read();

; SOURCE LINE # 220

LCALL

read

; delay();

; SOURCE LINE # 221

LCALL

delay

; porta='V';

: SOURCE LINE # 222

MOV

R0,#LOW (porta)

MOV

A,#056H

MOVX

@R0,A

; write();

; SOURCE LINE # 223

LCALL

write

; delay();

0

; SOURCE LINE # 224

LCALL

; porta=1:1;

; SOURCE LINE # 225

MOV

RO,#LOW (porta)

A,#03AH

MOV

MOVX

@R0, A

; write();

; SOURCE LINE # 226

```

| ; | delay();       | LCALL                            | write                                                                               |

|---|----------------|----------------------------------|-------------------------------------------------------------------------------------|

|   | porta=a0+0x30; | LCALL                            | ; SOURCE LINE # 227<br>delay                                                        |

|   |                | MOV<br>MOV<br>ADD<br>MOV<br>MOVX | ; SOURCE LINE # 228<br>RO,#LOW (a0)<br>A,@RC<br>A,#030H<br>R1,#LOW (porta)<br>@R1,A |

| , | write();       | LCALL                            | ; SOURCE LINE # 229 write                                                           |

| ; | delay();       | LCACL                            | ; SOURCE LINE # 230                                                                 |

| ; | porta=c0+0x30; | LCALL                            | delay                                                                               |

|   | write();       | MOV<br>MOV<br>ADD<br>MOV<br>MOVX | ; SOURCE LINE # 231<br>R0,#LOW (c0)<br>A,@R0<br>A,#030H<br>R1,#LOW (porta)<br>@R1,A |

| • | write(),       | LCALL                            | ; SOURCE LINE # 232<br>write                                                        |

| ; | delay();       |                                  | ; SOURCE LINE # 233                                                                 |

| ; | porta=d0+0x30; | LCALL                            | <b>de</b> lay                                                                       |

| ; | write();       | MOV<br>MOV<br>ADD<br>MOV<br>MOVX | ; SOURCE LINE # 234<br>R0,#LOW (d0)<br>A,@R0<br>A,#030H<br>R1,#LOW (porta)<br>@R1,A |

|   | 4-1            | LCALL                            | ; SOURCE LINE # 235<br>write                                                        |

| ; | delay();       | JLCALL                           | ; SOURCE LINE # 236<br>delay                                                        |

|   | porta='';      |                                  | ; SOURCE LINE # 239                                                                 |

| , | write();       | LCALL                            | ; SOURCE LINE # 238<br>L?0057                                                       |

| ; | delay();       | LCALL                            | ; SOURCE LINE # 239                                                                 |

| ; | porta=' ';     | LCALL                            | delay ; SOURCE LINE # 240                                                           |

| ; | write();       |                                  | ; SOURCE LINE # 241                                                                 |

| ; | delay();       | LCALL                            | L?0057                                                                              |

| ; | porta='';      | LCALL                            | ; SOURCE LINE # 242<br>delay                                                        |

| ; | write();       |                                  | ; SOURCE LINE # 243                                                                 |

|   | delay();       | LCALL                            | ; SOURCE LINE # 244<br>L?0058                                                       |

| ; | - "            | <b>L</b> CALL                    | ; SOURCE LINE # 245<br>delay                                                        |

| ; | porta='';      |                                  | ; SOURCE LINE # 246                                                                 |

| ; | write();       | <b>LC</b> ALL                    | ; SOURCE LINE # 247<br>L?0058                                                       |

| ; | delay();       |                                  | ; SOURCE LINE # 248                                                                 |

| : | porta='':      | LCALL                            | delay                                                                               |

; porta='';

```

; SOURCE LINE # 249

; write();

; SOURCE LINE # 250

LCALL

L?0058

; delay();

; SOURCE LINE # 251

JLCALL

delay

; porta='';

; SOURCE LINE # 252

; write();

; SOURCE LINE # 253

LCALL

L?0058

; delay();

; SOURCE LINE # 254

LÇALL

delay

; porta='';

; SOURCE LINE # 255

; write();

; SOURCE LINE # 256

LCALL

L?0058

; delay();

; SOURCE LINE # 257

⊔MP

delay

; END OF dis0

; }

; void ser_out0()

RSEG ?PR?ser_out0?KCT_PF

ser_out0:

USING

; SOURCE LINE # 260

; {

; SOURCE LINE # 261

; ser_data=dat0;

; SOURCE LINE # 262

MOV

R0,#LOW (dat0)

MOV

A,@R0

MOV

R0,#LOW (ser_data)

@R0,A

; ser_out();

; SOURCE LINE # 263

IJMP

ser_out

; END OF ser_out0

;}

; void adc1()

RSEG ?PR?adc1?KCT_PF

adc1:

USING

; SOURCE LINE # 266

; SOURCE LINE # 267

; x=ch1;

; SOURCE LINE # 268

MOV

R0,#LOW (ch1)

MOVX

A,@RJ

MOV

R0,#LOW (x)

MOV

@R0,A

; delay();

; SOURCE LINE # 269

LCALL

delay

; dat1=soc;

; SOURCE LINE # 270

MOV

RO, #LOW (soc)

MOVX

A,@R0

MOV

R0,#LOW (dat1)

MOV

@R0,A

;}

; SOURCE LINE # 271

RET

; END OF adc1

```

```

;

; void htd1()

RSEG ?PR?htd1?KCT_PF

htd1:

USING

; SOURCE LINE # 273

; {

; SOURCE LINE # 274

; a1=dat1/0x64;

: SOURCE LINE # 275

MOV

R0, #LOW (dat1)

A,@R0

MOV

R7,A

MOV

MOV

B,#064H

DIV

AB

MOV

MOV

R0,#LOW (a1)

@R0,A

; b1=dat1%0x64;

; SOURCE LINE # 276

MOV

A,R7

MOV

B.#064H

DIV

ΑB

R0,#LOW (b1)

MOV

MOV

@R0,B

; c1=b1/0x0a;

; SOURCE LINE # 277

MOV

A,@R0

MOV

R7,∧

B,#0AH

MOV

DIV

AB

MOV

R0,#LOW (c1)

MOV

@R0,A

; d1=b1%0x0a;

; SOURCE LINE # 278

MOV

A,R7

B,#0AH

MOV

DIV

ΑB

R0,#LOW (d1)

MOV

MOV

@R0,B

; }

; SOURCE LINE # 279

RET

; END OF htd1

; void dis1()

RSEG ?PR?dis1?KC1 PF

dis1:

USING

; SOURCE LINE # 281

;{

; SOURCE LINE # 282

; porta=0xc0;

; SOURCELINE # 283

MOV

RO,#LOW (porta)

A,#0C0H

MOV

MOVX

@R0,A

; read();

; SOURCE LINE # 284

LCALL

; delay();

; SOURCE LINE # 285

LCALL

delay

; porta='I';

; SOURCE LINE # 286

MOV

R0,#LOW (porta)

MOV

A,#049H

MOVX

@R0,A

; write();

; SOURCE LINE # 287

LCALL

; delay();

; SOURCE LINE # 288

LCALL

delay

```

```

; porta=':';

; SOURCE LINE # 289

MOV

R0,#1.OW (porta)

MOV

A,#03AH

MOVX

@RO,A

; write();

; SOURCE LINE # 290

LCALL

; delay();

; SOURCE LINE # 291

LCALL

delay

; porta=a1+0x30;

: SOURCE LINE # 292

MOV

R0,#LOW (a1)

A,@R0

MOV

A,#030H

ADD

MOV

R1,=LOW (porta)

MOVX

6,13@

; write();

; SOURCE LINE # 293

LCALL

; delay();

; SOURCE LINE # 294

LCALL

delay

; porta=c1+0x30;

; SOURCE LINE # 295

MOV

R0,#LOW (c1)

MOV

A,@R0

A,#030H

OADD

MOV

R1,#LOW (porta)

MOVX

@R1,A

; write();

; SOURCE LINE # 296

LCALL

; delay();

; SOURCE LINE # 297

LCALL

: porta='.:

; SOURCE LINE # 298

RO,#LOW (porta)

MOV

A,#02EH

MOV

MOVX

@R0,A

; write();

; SOURCE LINE # 299

LCALL

; delay();

; SOURCE LINE # 300

LCALL

delay

; porta=d1+0x30;

; SOURCE LINE # 301

R0,#LOW (d1)

MOV

MOV

A,@R0

ADD

A,#030H

MOV

R1,#LOW (porta)

MOVX

@R1,A

; write();

; SOURCE LINE # 302

LCALL

write

; delay();

; SOURCE LINE # 303

LCALL.

; porta='';

; SOURCE LINE # 304

; write();

; SOURCE LINE # 305

JCALL

L?0058

; delay();

; SOURCE LINE # 306

LCALL

; porta='';

; SOURCE LINE # 307

; write();

; SOURCE LINE # 308

LCALL

L?0058

; delay();

```

; SOURCE LINE # 309

```

LCALL

delay

; porta=' ';

; SOURCE LINE # 310

; write();

; SOURCE LINE # 311

LCALL

; delay();

; SOURCE LINE # 312

LCALL

delay

; porta=' ';

; SOURCE LINE # 313

write();

; SOURCE LINE # 314

LCALL

L?0058

; delay();

: SOURCE LINE # 315

LCALL

; porta='';

; SOURCE LINE # 316

; write();

; SOURCE LINE # 317

LCALL

L?0058

; delay();

; SOURCE LINE # 318

LCALL

delay

; porta=' ';

; SOURCE LINE # 319

; write();

; SOURCE LINE # 320

LCALL

L?0058

; delay();

; SOURCE LINE # 321

LCALL

delay

; porta=' ';

; SOURCE LINE # 322

; write();

; SOURCE LINE # 323

LCALL

; delay();

; SOURCE LINE # 324

dLCALL

delay

; porta='';

; SOURCE LINE # 325

; write();

; SOURCE LINE # 326

LCALL

L?0058

; delay();

; SOURCE LINE # 327

LIMP

delay

; END OF dis1

;}

; void ser_out1()

RSEG ?PR?ser_out1?KCT_PF

ser_out1:

USING

; SOURCE LINE # 330

: {

; SOURCE LINE # 331

; ser_data=dat1;

; SOURCE LINE # 332

MOV

R0,#LOW (dat1)

MOV

A,@R0

RO,#LOW (ser_data)

MOV

MOV

@R0,A

; ser_out();

; SOURCE LINE # 333

LIMP

ser_out

; END OF ser_out1

; }

; void power()

```

o

```

RSEG ?PR?power?KCT PF

power:

USING

; SOURCE LINE # 336

; {

; SOURCE LINE # 337

; float volt, cur;

; volt=dat0;

; SOURCE LINE # 339

MOV

R0,#LOW (dat0)

MOV

A,@RO

MOV

R4,A

CLR

LCALL

?C?FCASTC

MOV

volt?:241+03H,R7

MOV

volt?:241+02H,R6

MOV

volt?1241+01H,R5

volt?1241,R4

MOV

; cur=(float)dat1/10;

; SOURCE LINE # 340 R0,#LOW (dat1)

MOV

MOV

A,@R0

MOV

R4,A

CLR

LCALL

?C?FCASTC

CLR

R3,A

MOV

MOV

R2,A

MQV

R1,#020H

R0,#041H

MOV

LCALL

?C?FPDIV

;---- Variable 'cur?1242' assigned to Register 'R4/R5/R6/R7' ----

; pow=voit*cur;

; SOURCE LINE # 341

MOV

R3, volt?1241+03H

MOV

R2, volt?1241+02H

MOV

R1,volt?1241+01H

MOV

R0, volt?1241

?C?FPMUL

LCALL

LCALL

?C?CASTF

MOV

pow,R6

MOV

pow+01H,R7

; dat=pow*100;

; SOURCE LINE # 342

MOV

R4,#00H

MOV

R5,#064H

LCALL

?C?IMUL

MOV

dat,RG

MOV

dat +G1H,R7

; }

; SOURCE LINE # 343

♥

RET

; END OF power

; void htd2()

RSEG ?PR?htd2?KCT PF

htd2:

USING

; SOURCE LINE # 345

;{

; SOURCE LINE # 346

; a2=dat/0x2710;

; SOURCE LINE # 347

MOV

R6,dat

MOV

R7,dat+01H

CIOV

R4,#027H

MOV

R5,#010H

LCALL

?C?U:DIV

MOV

R0,#LOW (a2)

MOV

@R0,AR7

; b2=(unsigned long)dat%0x2710;

; SOURCE LINE # 348

MOV

R6,dat

MOV

R7,dat+01H

```

```

ÇLR

MOV

R4,A

MOV

R5,A

MOV

R3.#010H

VON

R2, #027H

MOV

R1.A

R0,A

MOV

LCALL

?C?ULDIV

MOV

R6,AR2

MOV

R7,AR3

MOV

R0,#LOW (b2)

MOV

@R0,AR6

INC

Ř0

@R0,AR7

•

MOV

; c2=b2/0x3e8;

; SOURCE LINE # 349

DEC

R0

A,@RO

MOV

MOV

R2,A

INC

RO

A,@RC

MOV

MOV

R3,A

MOV

R4,#03H

MOV

R5,#058H

MOV

R7.A

R6,AR2

MOV

LCALL

?C?UIDIV

MOV

R0,#LOW (c2)

MOV

@R0,AR7

; d2=b2%0x3e8;

; SOURCE LINE # 350

MOV

R4,#03H

MOV

R5,#0E8H

MOV

R7,Ak3

MOV

R6,AR2

LCALL

?C?UIDIV

MOV

R0,#LOW (d2)

MOV

@R0,AR4

INC

R0

MOV

@R0,AR5

; e2=d2/0x64;

; SOURCE LINE # 351

DEC

RO

A,@R0

MOV

MOV

R2,A

R0

INC

MOV

A,@RO

MOV

R3,A

MOV

R4,#00H

MOV

R5,#064H

MOV

R7,A

MOV

R6,AR2

LCALL

?C?UIDIV

R0,#LOW (e2)

@R0,AR7

MOV

MOV

; f2=d2%0x64;

; SOURCE LINE # 352

MOV

R4,#00H

310V

R5,#064H

MOV

R7,AR3

MOV

R6,AR2

LÇALL

VICIUSDS

MOV

R0,#LOW (f2)

MOV

@R0,AR5

; g2=f2/0x0a;

; SOURCE LINE # 353

MOV

A,@RO

MOV

R7,∧

B.#0AH

MOV

DIV

AΒ

INC

R0

MQV

@RO,A

; h2=f2%0x0a;

; SOURCE LINE # 354

MOV

A,R7

MOV

B,#0AH

```

```

DIV

AΒ

INC

R0

MOV

@R0,B

; }

; SOURCE LINE # 355

RET

; END OF htd2

; void htd3()

RSEG ?PR?htd3?KCT_PF

htd3:

USING

: SOURCE LINE # 357

; {

: SOURCE LINE # 358

; ae=date/0x2710;

; SOURCE LINE # 359

MOV

R6,date

MOV

R7,date+01H

MOV

R4,≑027H

MOV

R5.#010H

LCALL

?C?UIDIV

MOV

RO,#LOW (ae)

@R0,AR7

MOV

; be=(unsigned long)date%0x2710;

; SOURCE LINE # 360

MOV

R6,date

R7,date+01H

MOV

CLR

R4,A

MOV

R5,A

MOV

MOV

R3.#010H

R2,#027H

MOV

PIOV

R1,A

MQV

RO,A

LCALL

?C?ULDIV

MOV

R6,AR2

MOV

R7,AR3

RO,#LOW (be)

MOV

MOV

@R0,AR6

\bar{R}0

INC

@RO,AR7

MOV

; ce=be/0x3e8;

; SOURCE LINE # 361

DEC

R0

A,@R0

MOV

R2,A

MOV

INC

RO

MOV

A,@RC

R3,A

MOV

R4,#03H

MOV

R5,#0ESH

MOV

R7,A

MOV

MOV

R6,AR2

?C?UIDIV

LCALL

MOV

RO,#LOW (ce)

@R0,AR7

MOV

: de=be%0x3e8;

: SOURCE LINE # 362

R4,#03H

MOV

MOV

R5,#0E8H

MOV

R7,AR3

MOV

R6,AR2

LCALL

?C?UIDIV

R0,#LOW (de)

MOV

MOV

@R0, AR4

RO

INC

@R0,AR5

MOV

; ee=de/0x64;

; SOURCE LINE # 363

RC

DEC

A,@R0

MOV

R2,A

MOV

INC

R0

```

```

MOV

A,@R0

MOV

R3,A

MOV

R4,#00H

MOV

R5,#064H

MOV

R7,A

MOV

R6, AR2

?C?UIDIV

LCALL

MOV

R0,#LOW (ee)

MOV

@R0, AR7

; fe=de%0x64;

; SOURCE LINE # 364

MOV

R4,#00H

MOV