# DESIGN AND IMPLEMENTATION OF KWhr METER

## **USING EMBEDDED SYSTEMS**

#### A PROJECT REPORT

#### Submitted by

J.MOHANAPRIYA

(71201105025)

M.SAGAYA SABINA

(71201105044)

**G.YOGASRI**

(71201105073)

in partial fulfillment for the award of the degree

of

## **BACHELOR OF ENGINEERING**

in

## ELECTRICAL AND ELECTRONICS ENGINEERING

Under the guidance of

Mr.V.Kandasamy

## KUMARAGURU COLLEGE OF TECHNOLOGY, COIMBATORE

ANNA UNIVERSITY::CHENNAI-600 025

APRIL 2005

### **ANNA UNIVERSITY: CHENNAI-600 025**

#### **BONAFIDE CERTIFICATE**

Certified that this project report "DESIGN AND IMPLEMENTATAION OF kWhr METER USING EMBEDDED SYSTEMS" is the bonafide work of J.MOHANAPRIYA (71201105025)

M.SAGAYA SABINA (71201105044)

G.YOGASRI (71201105073)

who carried out the project work under my supervision.

**SIGNATURE**

Prof.K.Regupathy subramaniam, B.E., M.Sc. DEAN/EEE,

Kumaraguru college

of technology

**SIGNATURE**

Mr.V.Kandasamy,M.Tech, Lecturer,EEE, Kumaraguru college of technology

## **CERTIFICATION OF EVALUATION**

**College : KUMARAGURU COLLEGE OF TECHNOLOGY**

**Branch**: Electrical And Electronics Engineering

Semester : Eighth semester

| SI.No. | Name of the students | Title of the project                  | Name of the supervisor with designation |

|--------|----------------------|---------------------------------------|-----------------------------------------|

| 01     | J.MOHANAPRIYA        | "Design and                           | Mr.V.KANDASAMY                          |

| 02     | M.SAGAYA SABINA      | implementation                        | LECTURER.                               |

| 03     | G.YOGASRI            | of kWhr meter using embedded systems" |                                         |

The report of the project work submitted by the above students in partial fulfillment for the award of Bachelor of Engineering degree in Electrical and Electronics Engineering of Anna University were evaluated and confirmed to be report of the work done by the above students and then evaluated.

(INTERNAL EXAMINER)

(EXTERNAL EXAMINER)

**ACKNOWLEDGEMENT**

#### **ACKNOWLEDGEMENT**

The satisfaction that accompanies the successful completion of any task would be incomplete without mentioning the people who gave us constant guidance and support.

We would like to express our deep sense of gratitude towards our project guide Mr.V.Kandasamy,M.Tech lecturer, for directing us towards a more application-oriented project and for his support and interest in all our endeavors.

We would like to thank our project coordinator **Prof.K.Rajan M.E** assistant professor for having channelized our thoughts towards this project.

We would like to thank our former head of the department **Dr.T.M.Kameswaran PhD** for his constant encouragement and support.

We also thank our Dean **Prof.Reghupathy Subramanian B.E, M.sc** for his constant guidance and support.

Further we would like to acknowledge the support shown by our beloved principal **Dr.K.K.Padmanabhan B.Sc(Engg)**, **Ph.D.**

We also extend our heartiest thanks to all our staff members, non-technicians, without them we would have never attained this form.

SYNOPSIS

## **SYNOPSIS**

The Kilowatt-hour meter cum cost indicator using embedded systems is a very reliable energy meter. It is designed so as to measure and display the number of units consumed and its corresponding cost. All houses, apartments, offices and industries are equipped with energy meter. At present, analog energy meters are very commonly used. In these energy meters, the number of units consumed for a certain period can be found by calculating the difference between readings at the start and end of the period in an energy meter. Our proposed energy meter digitally displays the number of units consumed and corresponding costs for it.

The Microcontroller we have used is PIC 16F877. It has only 35 single word instructions and thus easily programmable. It has an inbuilt ADC, which reduces the complexity of the circuit. In our project we have used EEPROM data memory.

The interfacing to the LCD display is done directly through the I/O ports of the PIC. We have also transmitted the data to the pc through serial communication.

# DEDICATED TO OUR BELOVED PARENTS AND FRIENDS

## **LIST OF CONTENTS**

| CHAPTER | NO                                                      | TITLE PAG                                                                                                   | E NO |

|---------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|

|         |                                                         | Synopsis iv                                                                                                 |      |

|         |                                                         | List Of Tables xii                                                                                          |      |

|         |                                                         | List Of Figures xii                                                                                         |      |

| 1.      |                                                         | INTRODUCTION                                                                                                | 1    |

|         | 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3<br>1.4              | Need For Our Project Analog Energy Meter Principle of Operation Disadvantages Electrical Energy Tariff      |      |

| 2.      |                                                         | METHODOLOGY                                                                                                 | 5    |

|         | 2.1<br>2.2                                              | Schematic Diagram Explanation                                                                               |      |

| 3.      |                                                         | HARDWARE                                                                                                    | 9    |

|         | 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.2.2 | Power Supply Unit Rectifier Filter Regulator Voltage & Current Measurement Specifications Absolute Circuits |      |

|         | 3.2.3                                                   | Voltage Measurement                                                                                         |      |

|    | 3.2.4<br>3.3<br>3.4                               | Current Measurement Power Factor Measurement LCD Display                                                                                  |    |

|----|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4. |                                                   | MICROCONTROLLER UNIT                                                                                                                      | 21 |

|    | 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.4<br>4.5 | PIC 16F877 Features Memory Organisation Program Memory Organisation Data Memory Organisation I/O Ports Analog To Digital Converter Timers |    |

| 5. |                                                   | SERIAL DATA COMMUNICATION                                                                                                                 | 31 |

|    | 5.1<br>5.2<br>5.3                                 | Introduction Pin Description Characteristics Of MAX 232                                                                                   |    |

| 6. |                                                   | SOFTWARE                                                                                                                                  | 35 |

|    | 6.1<br>6.2                                        | Flow Chart<br>Program                                                                                                                     |    |

| 7. |                                                   | CONCLUSION                                                                                                                                | 59 |

|    | 7.1                                               | Future Enhancement                                                                                                                        |    |

|    |                                                   | APPENDIX                                                                                                                                  | 61 |

|    |                                                   | REFERENCES                                                                                                                                | 89 |

# **LIST OF FIGURES**

| FIGURE NO | TITLE                              | PAGE NO |

|-----------|------------------------------------|---------|

| 2.1       | Block diagram                      | 6       |

| 2.2       | Overall circuit diagram            | 8       |

| 3.1       | Block diagram of power supply unit | 10      |

| 3.2       | Power supply unit                  | 11      |

| 3.2.3     | Voltage measurement circuit        | 14      |

| 3.2.4     | Current measurement circuit        | 17      |

| 3.3.1     | Power factor measurement circuit   | 19      |

| 4.1       | 16f877 Pin diagram                 | 23      |

| 4.2       | 16f877 Architecture                | 24      |

| 4.3       | Program memory organization        | 25      |

# **LIST OF TABLES**

| TABLE NO | TITLE                      | PAGE NO |

|----------|----------------------------|---------|

| 3.3.1    | Truth table for ex-or gate | 18      |

| 4.1      | Bank selection             | 26      |

| 5.2      | RS 232 pin assignments     | 32      |

INTRODUCTION

## **CHAPTER 1**

#### INTRODUCTION

## 1.1 Need For Our Project

Energy plays a significant role in development of nation. Today there is a trend towards tremendous growth and phenomenal modernization of electrical system throughout the world. Energy is infact power integrated over a period of time. Energy meters are essentially integrating instruments reading a continuous quantity and are quite different from other integrating instruments. They measure power over a period of time, integrating it into energy. Thus the amount of electrical energy supplied to the customers is metered.

Induction type meters are the most common form of AC energy meters used in everyday domestic and industrial installations. There are various disadvantages encountered in analog energy meters. Errors in conventional energy meters are mainly due to forces at the rotor bearings and in register mechanism. These errors are avoided in digital energy meters. In case of digital measurements the readings obtained are precise and accurate. Our proposed energy meter using embedded system displays the energy consumed over a period of time and its corresponding cost and thus manual calculations are eliminated.

In small industries, when the cost goes beyond the limit luxury equipment like fans, refrigerators and air conditioners can be turned off to reduce energy consumption.

## 1.2 ANALOG ENERGY METER

An energy meter is a device that is used to measure the energy consumed by the electrical equipment connected to the supply. The Induction Type Energy Meter is universally used in domestic and industrial AC circuits.

## 1.2.1 PRINCIPLE OF OPERATION

The main principle of operation of analog equipments mainly depends on magnetic field produced. In analog energy meters the eddy currents produced due to magnetic flux plays an important role in energy measurement. The single-phase energy meter consists of two coils namely current coil and pressure coil. The current coil is made up of few turns of thick wire and is connected in series with the load. The pressure coil consists of few turns of thin wire and is connected in parallel with the supply. An aluminum disc mounted on a spindle is placed between two coils. The two fluxes produced by the two coils interact with aluminium disc and produces eddy currents in the disc and hence the disc starts rotating. The speed of the disc is proportional to the energy consumed by the load.

## 1.2.2 DISADVANTAGES

Disadvantages present in analog meters are

- The lifetime of analog meters are very less.

- The readings obtained are not precise and accurate.

- The readings obtained can easily be tampered.

- Presence of mechanical moving parts.

## 1.3 ELECTRICAL ENERGY

The unit of energy is Joule, which is the work done when a force of 1N acts through a distance of 1m in the direction of the force.

Electrical energy voltage in current in time in in watt hour = volts \* amps \* hours

## 1.4 TARIFF

The rate at which electrical energy supplied to the customer is known as tariff. The various types of tariff are

- > Simple tariff

- > Flat rate tariff

- ➤ Block rate tariff

- > Two port tariff

- > Maximum demand tariff

- > Power factor tariff

- > Three port tariff

The TNEB tariff for most of the organizations like schools, colleges, hospitals, residential houses, hotels and shops falls in one of the first three tariffs.

**METHODOLOGY**

## **CHAPTER 2**

## **METHODOLOGY**

## 2.1 SCHEMATIC DIAGRAM

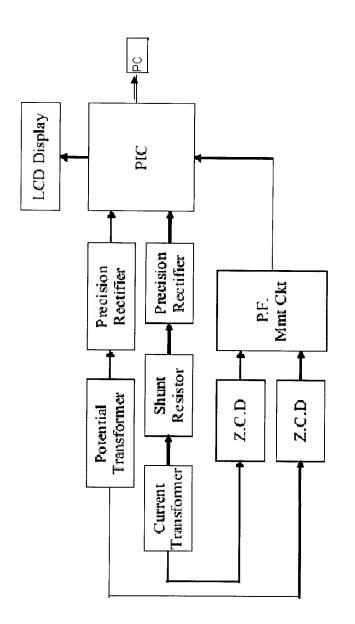

The schematic diagram of our project is shown below in figure 2.1.

Fig 2.1 BLOCK DIAGRAM

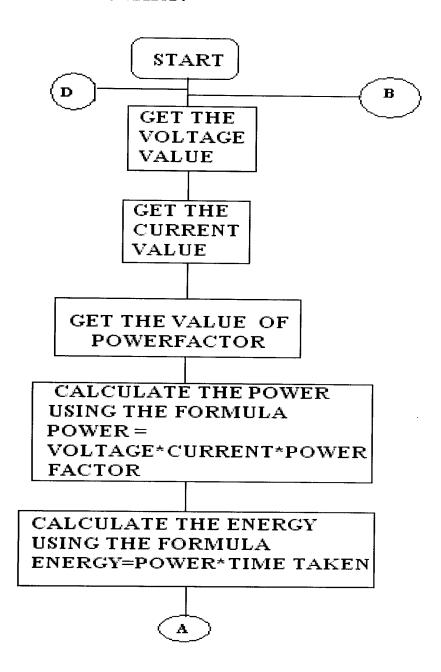

The voltage and current signals are sensed and stepped down using potential transformer and current transformer respectively. The voltage and current signals are then given to precision rectifier to convert into an equivalent D.C signal. The current measurement circuit is similar to the voltage measurement circuit except for the shunt resistor included in the current measurement circuit.

The time lag between the voltage and the current signal is calculated using a zero crossing detector along with an XOR gate from which power factor can be calculated. The voltage signal, current signal and the power factor are fed to the PIC microcontroller.

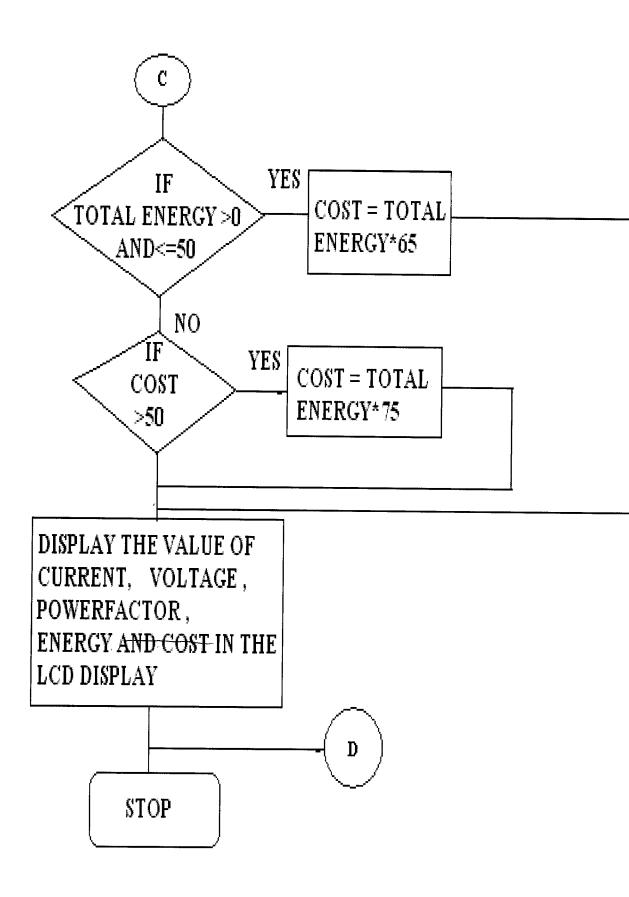

The PIC 16F877 is used to calculate the energy and the cost for the number of units consumed. The voltage, current, powerfactor, energy and the cost are displayed using a LCD. The PIC is also interfaced to PC.

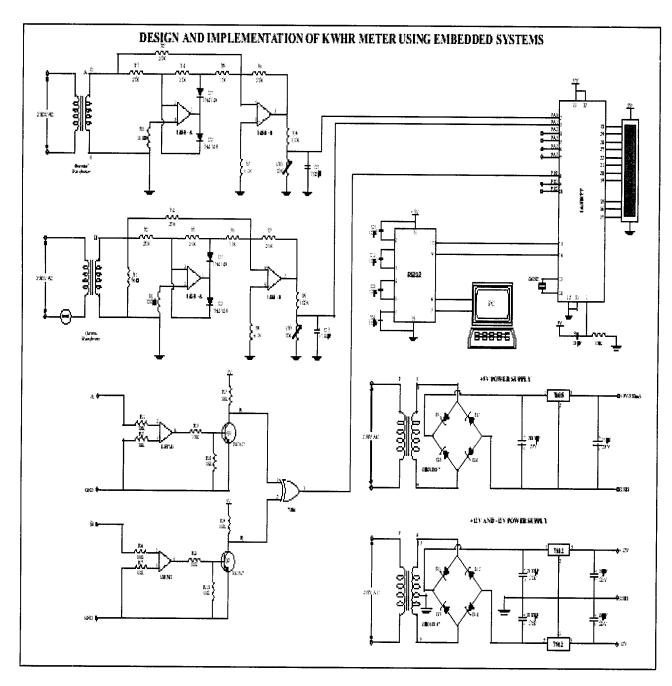

Fig.2.2 OVERALL CIRCUIT DIAGRAM

**HARDWARE**

## **CHAPTER 3**

#### **HARDWARE**

#### 3.1 POWER SUPPLY UNIT

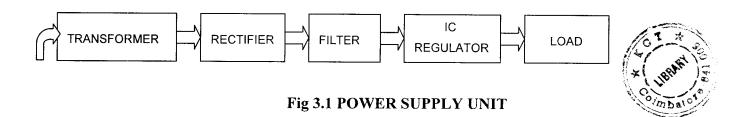

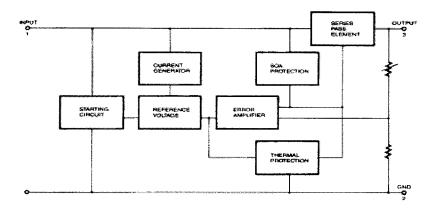

Since all the power circuits work only with low D.C. voltage we need a power supply unit to provide the appropriate voltage supply. The general power supply unit is shown in fig.3.1

This unit consists of transformers, rectifiers, filters and regulators. The input AC voltage diode rectifier then provides a full wave rectified, typically 230Vrms is connected to a transformer to obtain the desired step-down AC voltage. A diode rectifier then provides a full-wave rectified voltage that is initially filtered by a simple capacitor filter to produce a DC voltage. This resulting DC voltage usually has some ripple or AC voltage variations. A regulator circuit can use this DC input to provide DC voltage that not only has less ripple voltage but also remains the same DC value even if the DC voltage varies, or when the load connected to the output DC voltage changes.

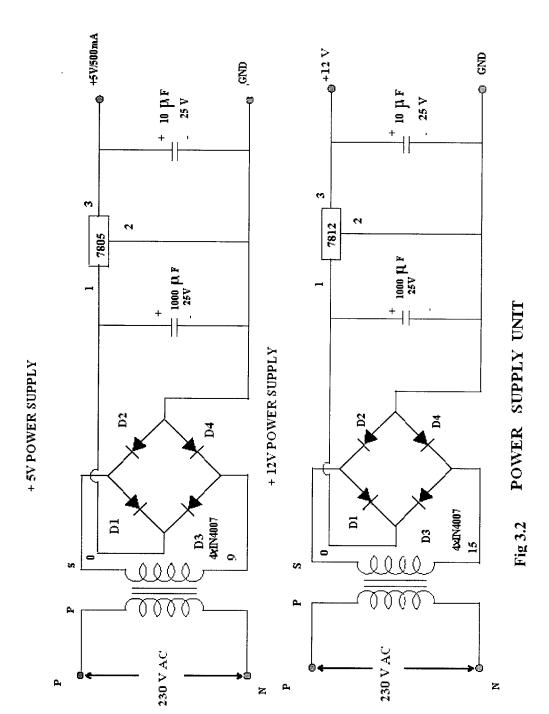

The power supply unit comprises of two circuits, one providing a +5V supply and the other providing +12V and -12V supply. The circuit diagrams for the same are shown in the Figure 3.2.

## 3.1.1 RECTIFIER

The DC level obtained from a sinusoidal input can be improved 100% using a process called full-wave rectification. It uses 4 diodes in a bridge configuration. From the basic bridge configuration we see that two diodes (say D2, D3) are conducting while the other two diodes (D1,D4) are in "off" state during the period t=0 to T/2. Accordingly for the negative half cycle of the input the conducting diodes are D1 and D4. Thus the polarity across the load is the same.

#### 3.1.2 FILTER

The filter circuit used here is the capacitor is connected at the rectifier output, and a DC is obtained across it. The filtered waveform is essentially a DC voltage with negligible ripples, while is ultimately fed to the load.

### 3.1.3 REGULATORS

The voltage regulator is a device, which maintains the output voltage constant irrespective of the change in supply variations, load variation and temperature changes. The fixed voltage regulator is a three terminal device which has an unregulated dc input voltage, Vi, applied to one input terminal, a regulated output dc voltage, Vo, from a second terminal, with the third terminal connected to ground .For a selected regulator, IC device specifications list a voltage range over which the input voltage can vary to maintain a regulated output voltage over a

range of load current. The specifications also list the amount of output voltage change resulting from a change in load current or in input voltage.

Here we use two fixed voltage regulators namely LM7812, LM7805 and LM7912. The IC7812 is a +12V regulator, IC7912 is a -12V regulator and IC7805 is a +5V, regulator. The series 78 regulators provide regulated voltages from -5 to -24 V.

## 3.2 VOLTAGE & CURRENT MEASUREMENT

## 3.2.1 SPECIFICATIONS

## a) Potential Transformer ratings

Primary:

230V AC

Secondary:

6V AC

## b) Current Transformer ratings

Primary:

15A

Secondary:

5A

## 3.2.2 VOLTAGE MEASUREMENT

Voltage measurement circuit comprises of a potential transformer and precision rectifier. Potential transformer is used for sensing and stepping down the voltage signal. Precision rectifier converts the stepped down AC signal into an equivalent DC signal. The DC output voltage signal is then given to the zero crossing detector and the PIC microcontroller unit.

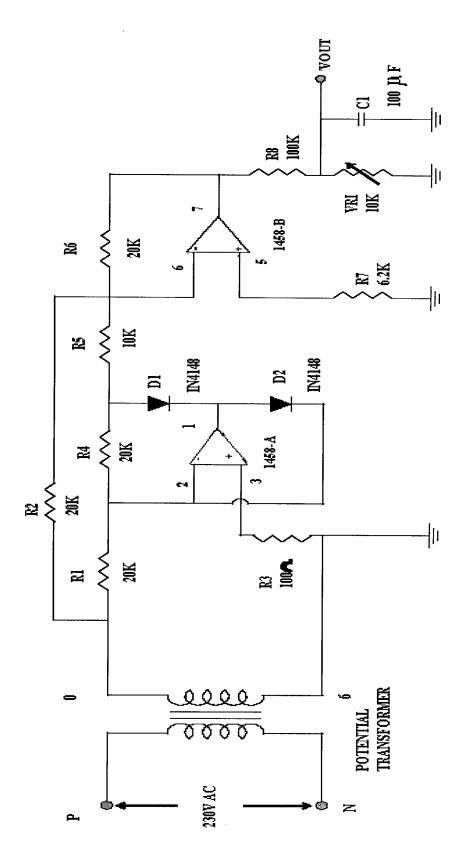

Fig 3.2.2 VOLTAGE MEASUREMENT CIRCUIT

#### 3.2.3 ABSOLUTE VALUE CIRCUITS

An absolute-value circuit, or full-wave precision rectifier, can be implemented by summing the output of a half-wave rectifier and its input with the proper phase and amplitude relations. This circuit will be the starting point for a number of other absolute-value circuits, which have evolved from this basic form.

In this circuit, A1 is an inverting rectifier similar to the figure. The output from A1 is added to the original input signal in A2 (a summing mixer) with the signal amplitude and phase relations shown. Negative alterations of Ein feeds A2 through 20-k $\Omega$  resistor, and E1 feed A2 through a 10-k $\Omega$  resistor. The net effect of this scaling is that, for equal amplitudes of Ein and E1, E1will provide twice as much current into the summing point. This fact is used to advantage here, as the negative alteration of E1 produces twice the input current of that caused by the positive alternation of Ein.

This causes a current of precisely half the amplitude, which E1 alone would generate due to the subtraction of Ein. It is the equivalent of having E1 feed through a 20-k $\Omega$  input receiver and having Ein non-existent during this half cycle, and it results in a positive going output at A2. During negative alterations of Ein, E1 is absent and Ein produces the alternate positive output swing that, in summation, produces the desired full-wave rectified response. As before, operation with the opposite output polarity is possible by reversing D1 and D2.

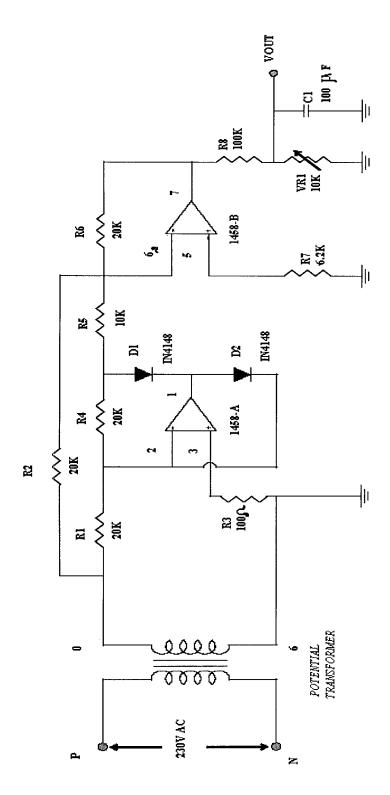

#### 3.2.4 CURRENT MEASUREMENT

The current measurement circuit consists of Current transformer of turns ratio 5:1. The Current Transformer's primary winding is connected in series with the line. The secondary of the Current Transformer is connected to a precision rectifier network. The shunt resistor of value 56 ohm is connected across the CT. Hence we have ac voltage proportional to the current flowing through the primary of the CT given as the input to the rectifier unit and by a similar procedure as seen in case of voltage measurement, we get pure DC at the output stage of the rectifier. The current measurement circuit is shown in figure 3.2.4.

Fig 3.2.4 CURRENT NEASUREMENT CIRCUIT

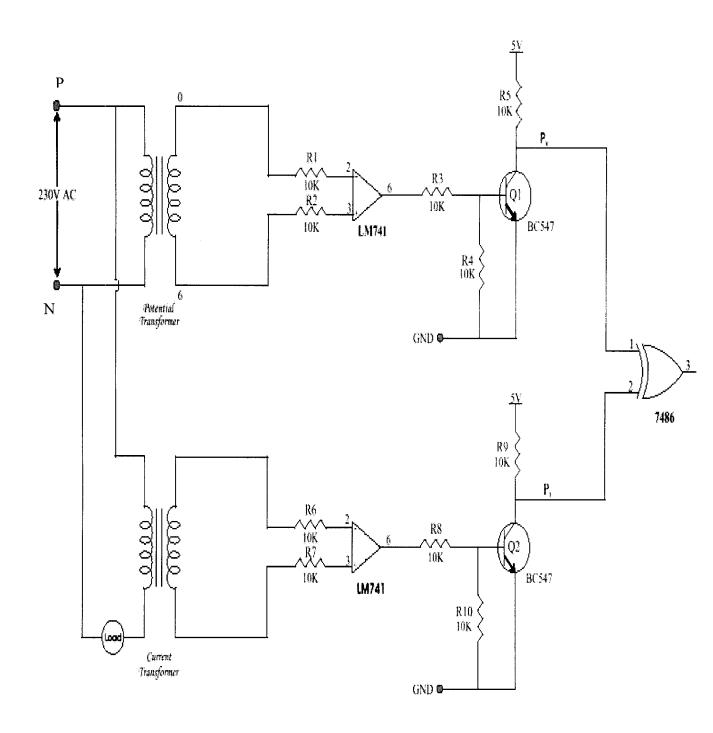

## 3.3. POWER FACTOR MEASUREMENT

The power factor measurement circuit consists of PT, CT, zero crossing detector and finally an XOR gate. PT and CT are used to sense the voltage and current signals respectively. Zero crossing detector, converts the sine wave into square wave. The circuit is also called a sine to square wave generator.

The square pulse outputs of the ZCD circuits are given as an input to an XOR gate. The output of the gate depends upon the input given. The truth table of XOR gate is

$$Y = AB' + A'B.$$

**TABLE: 3.3.1. TRUTH TABLE FOR**

|   | XOR | GATE |

|---|-----|------|

| A | В   | Y    |

| 0 | 0   | 0    |

| 0 | 1   | 1    |

| 1 | 0   | 1    |

| 1 | 1   | 0    |

The XOR gate will produce the output when both the inputs to the gate are not in the same state. So the output of the gate is the indirect measure of phase angle between the voltage and current. A timer is incremented in millisecond, which is equivalent to corresponding phase angle in degrees. Leading or lagging power factor is determined based on the pulse at the output of voltage's Zero Crossing Detector.

Fig 3.3.1 POWER FACTOR MEASUREMENT CIRCUIT

### 3.4 LCD DISPLAY

In our project, the readings obtained as shown on an LCD display. An LCD consists of two glass panels, with the liquid crystal material sand-witched between them. The inner surface of the glass plate is coated with transparent electrodes, which define the character, symbols or patterns to be displayed. Polymetric layers are present in between the electrodes and the light crystal, which makes the liquid crystal electrodes to maintain a defined oriented angle.

Polarisers are pasted outside the glass panels. These polarisers would rotate the light rays passing through them to a definite angle, in a particular direction. When the LCD is in off state, light rays are rotated by the two polarisers and the liquid crystal, such that the light rays come out of the LCD without any orientation, and hence the LCD appears transparent.

When sufficient voltage is applied to the electrodes, the liquid crystal molecules would be aligned in a specific direction. The light rays passing through the LCD would be rotated by the polarisers, which would result in activating /highlighting the desired characters. The LCD's are lightweight with only a few millimeters thickness. Since the LCD's consume less power, they are compatible with low power electronic circuits, and can be powered for long durations. The LCD doesn't generate light and so light is needed to read the display. By using backlighting, reading is possible in the dark. The LCD's have long life and a wide operating temperature range.

**MICROCONTROLLER UNIT**

## **CHAPTER 4**

#### MICROCONTROLLER UNIT

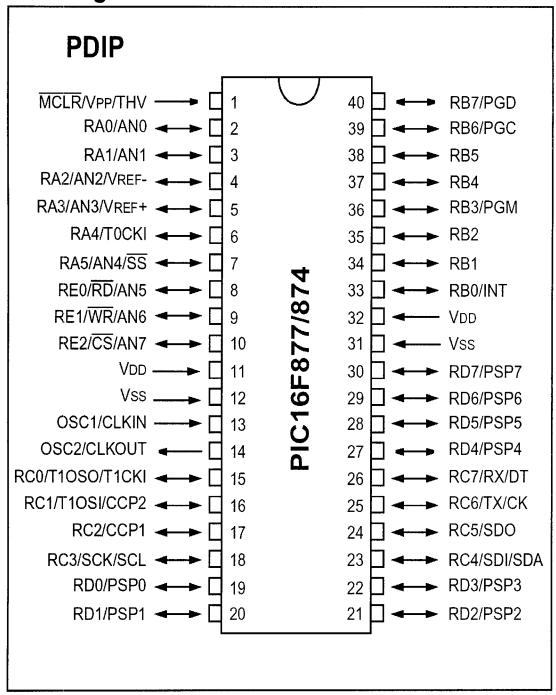

#### 4.1 PIC 16F877 ARCHITECTURE

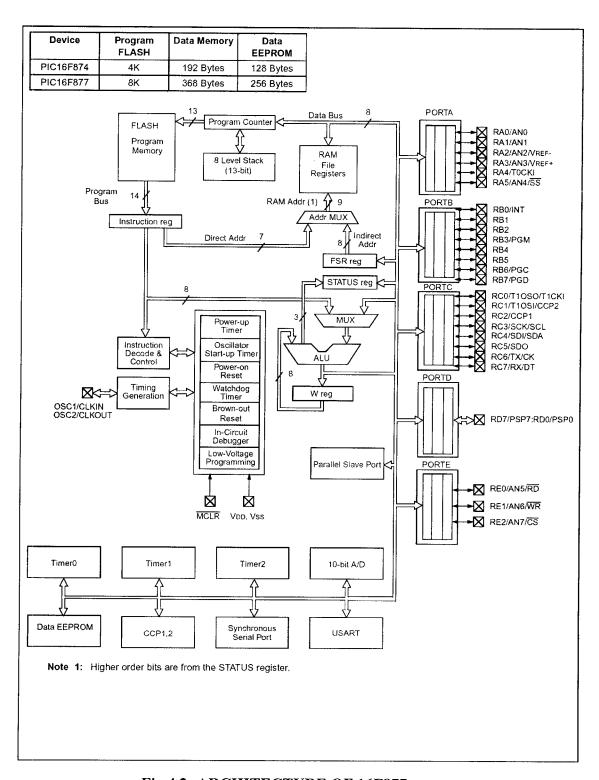

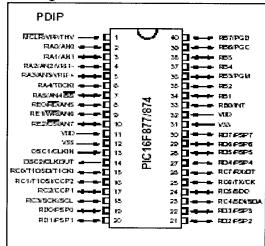

The microcontroller that we have used is PIC 16F877. The PIC series comprises of PIC16F873, PIC16F874, PIC16F876 and PIC16F877. PIC16F873 and PIC16F874 are 28-pin packages. In our project we have used the PIC16F877 for its outstanding features like:

- High-performance RISC CPU

- Only 35 single word instructions to learn

- Up to 8K x 14 words of FLASH Program Memory

- Up to 368 x 8 bytes of Data Memory (RAM)

- Up to 256 x 8 bytes of EEPROM data memory

- Processor read/write access to program memory

- Wide operating voltage range: 2.0V to 5.5V

- High Sink/Source Current: 25 mA

# Pin Diagram

Fig 4.1: PIN DIAGRAM OF 16F877

#### **ARCHITECTURE:**

Fig 4.2: ARCHITECTURE OF 16F877

## 4. 2 MEMORY ORGANIZATION:

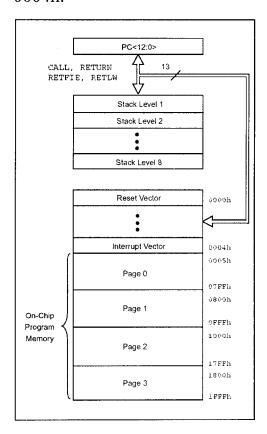

There are three memory blocks in each of these PIC MCU's. The Program Memory and Data Memory have separate buses so that concurrent access can occur.

#### **4.2.1 PROGRAM MEMORY ORGANIZATION:**

The PIC16F87X devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16F877/876 devices have 8K x 14 words of FLASH program memory. Accessing a location above the physically implemented address will cause a wrap around. The reset vector is at 0000h and the interrupt vector is at 0004h.

Fig.4.3 PROGRAM MEMORY ORGANISATION

### 4.2.2 DATA MEMORY ORGANIZATION

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

**Table 4.1 BANK SELECTION**

All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

The register file can be accessed either directly, or indirectly through the File Select Register, FSR.

The special function registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into 2 sets: Core (CPU) and peripheral. The registers present in SFR's are explained in brief.

The STATUS register contains the arithmetic status of the ALU, the RESET, status and bank select bits for data

memory. The OPTION-REG register is a readable and writable register, which contains various control bits to configure the TMRO prescales/WDT postscaler, TMRO and the weak pull-ups on port B.

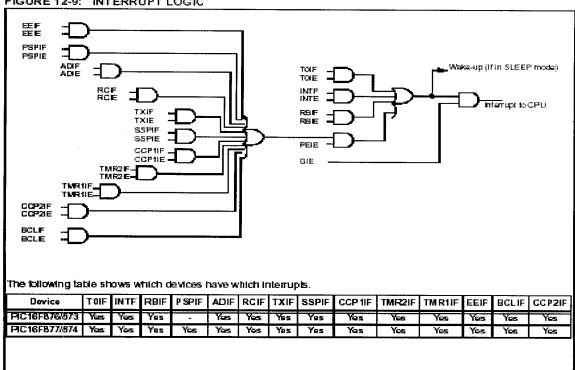

The INTCON register is a readable and writable register, which contains various enable and flag bits for the TMRO register overflow, RB port change and external RBO/INT pin interrupts.

The PIE1 register contains the individual enable bits for peripheral interrupts.

The PIR1 register contains the individual flag bits for peripheral interrupts.

The PIE2 register contains the individual enable bits for CCP2 peripheral interrupt, the SSP bus collision interrupt and EEPROM write operation interrupt's

The PIR2 register contains the individual flag bits for CCP2 peripheral interrupt, the SSP bus collision interrupt and EEPROM write operation interrupt's.

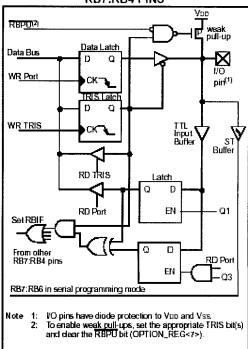

#### **4.3 I/O PORTS**

There are totally 6 ports present in PIC16F877. They are port A, port B, port C, port D, port E and parallel slave port.

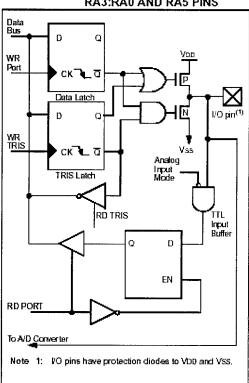

## PORTA AND THE TRISA REGISTER:

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISA

bit (=0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

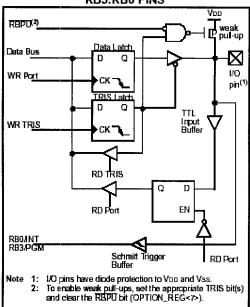

#### PORTB AND THE TRISB REGISTER:

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

#### PORTC AND THE TRISC REGISTER:

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

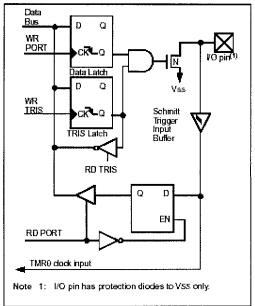

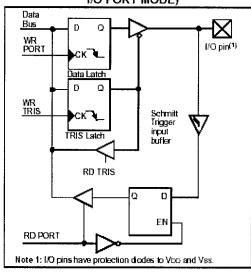

#### **PORTD AND TRISD REGISTERS:**

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### PORTE AND TRISE REGISTER:

PORTE has three pins, RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configurable as inputs or outputs.

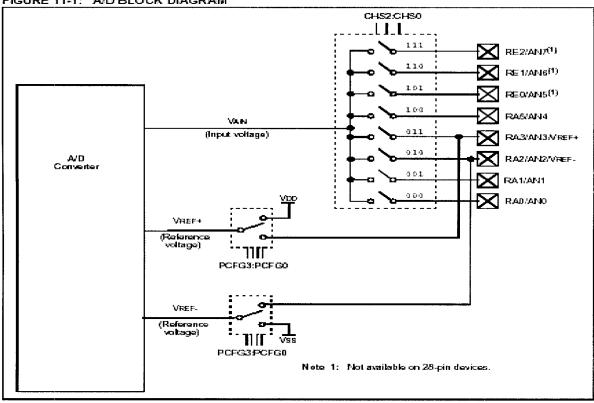

## 4.4 ANALOG TO DIGITAL CONVERTER

The Analog-to-Digital (A/D) Converter module has eight inputs for the 40 device. The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. The A/D conversion of the analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low voltage reference input that is software selectable to some combination of VDD, VSS, RA2 or RA3.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers.

These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register controls the operation of the A/D module. The port pins can be configured as analog inputs (RA3 can also be the voltage reference) or as digital I/O.

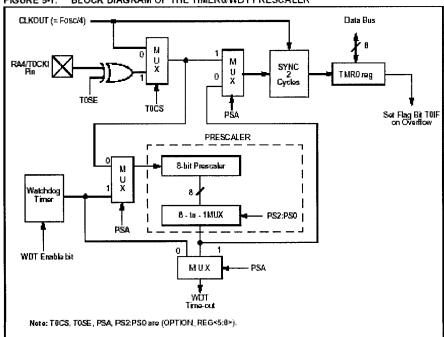

### 4.5 TIMERS

#### TIMER 0 MODULE

The timer 0 module timer/counter has the following features:

- > 8-bit timer counter

- Readable and writable

- > 8-bit software programmable prescaler

- > Internal and external clock select

- > Interrupt on overflow from ffh to ooh

- > Edge select for external clock

The TMRO interrupt is generated when the TMRO register overflows from ffh to ooh. This overflow sets bit TOIF (INTCON<2>). The interrupt can be masked by cleaning bit TOIE (INTCON<5>). Bit TOIF must be cleared in software by timer 0 module. Interrupt service routine before re-sending the interrupt. The TMRO interrupt cannot awaken the processor from sleep, since timer is shut-off during sleep.

SERIAL DATA COMMUNICATION

# **CHAPTER 5**

# **SERIAL DATA COMMUNICATION**

#### 5.1 INTRODUCTION

Modem and other devices used to send serial data are often referred to as data communication equipment or DCE. The terminals or computers that are sending or receiving the data are referred to as data terminal equipment or DTE. In response to the need for signal and handshake standards between DTE and DCE, the Electronic Industries Association (EIA) developed standard RS-232c. This standard describes the functions of 25 signals and handshake pins for serial data transfer. It also describes the voltage levels, Impedance levels, rise and fall times, Maximum bit rates, and maximum capacitance for these signal lines. RS232-c specifies 25 signal pins and it specifies that the DTE connector should be a male, and the DCE connector should be a female.

**TABLE: 5.1. RS232 PIN ASSIGNMENTS**

| Pin1 | Received line signal detector ( data carrier detect ) |

|------|-------------------------------------------------------|

| Pin2 | Received data                                         |

| Pin3 | Transmit data                                         |

| Pin4 | Data terminal ready                                   |

| Pin5 | Signal ground                                         |

| Pin6 | Data set ready                                        |

| Pin7 | Request to send                                       |

| Pin8 | Clear to send                                         |

| Pin9 | Ring indicator                                        |

## 5.1. PIN DESCRIPTION

# **DTR** (Data Terminal Ready)

When the terminal is turned on, after going through a self-test, it sends out signal DTR to indicate that it is ready for communication.

### DSR (Data Set Ready)

When DCE is turned on and has gone through the self-test, it asserts DSR to indicate that it is ready to communicate.

# RTS (Request to Send)

When DTE device such as has a byte to transmit, it asserts RTS to signal the modem that it has a byte of data transmit.

#### CTS (Clear To Send)

In response to RTS when the modem has room for storing the data it is to receive, it sends out signal CTS to the DTE (pc) to indicate that it can receive the data now.

## **DCD( Data Carrier Detect)**

The modem assert signal DCD to inform the DTE (pc) that a valid carrier has been detected and that contact between it and other modem is established.

# RI (Ring Indicator)

An output from the modem (DCE) and an input to a pc (DTE) indicates that the telephone is ringing. It goes on and off in synchronization with the ringing sound.

While signals DTR and DSR are used by the pc and modem respectively, to indicate that they are alive and well, it is RTS

and CTS that actually control the flow of data. RTS and CTS are also referred to as hardware control flow signals.

This concludes the description of the most important pins of the RS232 handshake signals plus TxD, RxD and ground. Ground is also referred to as SG (signal ground).

### **5.2 CHARACTERISTICS OF MAX 232**

## 5.2.1. ELECTRICAL CHARACTERISTICS OF MAX 232

Vcc = 6V.

V + = 12V.

V - = 12V.

#### **5.2.2. INPUT VOLTAGE**

T1 in, T2 in = -0.3 to (Vcc + 0.3V)

R1 in, R2 in = +30V or -30V.

#### **5.2.3. OUTPUT VOLTAGE**

TI out, T2 out = ((V+) + 0.3V) to ((V-) + 0.3V).

R1 out, R2 out = -0.3V to (Vcc + 0.3V).

Power dissipation = 375 mW.

Output resistance =  $300\Omega$ .

**SOFTWARE**

# **CHAPTER 6**

### **SOFTWARE**

# **6.1 FLOW CHART:**

#### **6.2 PROGRAM**

```

#include<pic.h>

//V,I & PF in single chip PIC

#include<math.h>

static bit pb1 @((unsigned)&PORTB*8+1);

static bit pb2 @((unsigned)&PORTB*8+2);

static bit pb4 @((unsigned)&PORTB*8+4);

static bit pb5 @((unsigned)&PORTB*8+5):

static bit input @((unsigned)&PORTE*8+0):

((pb4=0),(pb2=1),(pb1=0),(pb5=0),(pb5=1))

#define DISCTR

#define DISDAT

((pb4=0), (pb2=0), (pb1=1), (pb5=0), (pb5=1))

static bit key2 @((unsigned) &PORTC*8+0);

void lcd init();

void lcd rd();

void lcd wr();

void lcd_disp(unsigned char);

void lcd condis(const unsigned char*, unsigned int);

void hex dec(unsigned char);

void hex dec curr(unsigned int);

void hex dec pf(int);

void hex dec pow(unsigned int);

void hex dec cost(unsigned int);

```

```

void hex dec ap(unsigned int);

void delay(unsigned int);

void ser txn(unsigned char);

void ser_contxn(const unsigned char*,unsigned int);

void eeprom wr(unsigned char, unsigned char):

char eeprom rd(unsigned char);

unsigned char h,hr,t,o,ptt,pth,ph,pt,po,i;

unsigned char tkw,q,s,l,hi;

unsigned char dh1,dh2,b,count,pf;

unsigned int p,ene,kw,cost,enel;

unsigned int pttr,pthr,phr;

float x,y;

bit fac,m,k1,k2;

void interrupt timer1(void)

{

if(TMR1IF==1 && fac==1)

//for power factor cal

{

TMR1ON=0;

TMR1IF=0;

TRISC=0xf0;

count++;

```

```

TMR1H=0xff;

TMR1L=0x9b;

TMR1ON=1;

}

else if(TMR1IF==1 && fac==0) //for time cal

TMR1ON=0;

b++;

if(b==15) //for 1 sec

{

b=0;

s++;

if(s==10) //for 10 sec

{

s=0;

m=1;

}

TMR1IF=0;

TMR1ON=1;

}

main()

{

```

```

ADCON1=0x02;

TRISE=0x07;

TRISB=0x00;

count=0;

TRISD=0;

TRISC=0xff;

lcd_init();

lcd_condis("POWER MONITORING",16);

delay(10000);

\operatorname{eeprom\_rd}(0x00);

ptt=q;

eeprom rd(0x01);

//read ENERGY from EEPROM

pth=q;

eeprom_rd(0x02);

ph=q;

eeprom_rd(0x03);

pt≐q;

eeprom rd(0x04);

po=q;

enel=(ptt*10000+pth*1000+ph*100+pt*10+po);

eeprom_rd(0x08);

ptt=q;

eeprom_rd(0x09);

//read ENERGY from EEPROM

pth=q;

eeprom rd(0x0a);

```

```

ph=q;

eeprom_rd(0x0b);

pt=q;

eeprom_rd(0x0c);

po=q;

tkw=(ptt*10000+pth*1000+ph*100+pt*10+po);

GIE=1;

PEIE=1;

TMR1IE=1;

TMR1L=0x00;

TMR1H=0x00;

PORTD=0x01;

lcd rd();

while(1)

ADCON0=0x00;

ADON=1;

delay(255);

ADCON0=0x05;

while(ADCON0!=0x01);

dh1=ADRESH;

PORTD=0x80;

lcd_rd();

lcd_condis("V:",3);

```

```

hex dec(dh1);

ser_contxn("Voltage:",8);

ser_txn(h+0x30);

ser_txn(t+0x30);

ser_txn(o+0x30);

ser_contxn(" ",6);

ADON=0;

ADCON0=0x08;

ADON=1;

delay(255);

ADCON0=0x0d;

while(ADCON0!=0x09);

dh2=ADRESH;

PORTD=0x87;

lcd rd();

lcd condis(" I:",3);

hex_dec_curr(dh2);

ser contxn("Current:",8);

ser_txn(h+0x30);

ser txn(t+0x30);

ser_txn('.');

ser_txn(o+0x30);

ser contxn(" ",6);

```

```

GIE=1;

PEIE=1;

TMR1IE=1;

TMR1ON=0;

hi=TMR1H;

l=TMR1L;

TMR1H=0xff;

TMR1L=0x9b;

fac=1;

while(input==0);

TMR1ON=1;

while(input==1);

fac=0;

TMR1L=1;

TMR1H=hi;

x=count*1.8;

x=x*3.14;

x=x/180;

y=cos(x);

y=y*100;

pf=y;

PORTD=0xc0;

lcd_rd();

```

```

lcd_condis("PF:",3);

hex_dec_pf(pf);

count=0;

ser_contxn("PF:",3);

ser_txn(h+0x30);

ser_txn('.');

ser_txn(t+0x30);

ser_txn(o+0x30);

",6);

ser contxn("

p=dh1*dh2;

p=p/100;

p=p*pf;

if(m==1)

{

m=0;

p=p/360;

ene=enel+p;

enel=ene;

PORTD=0xc7;

lcd rd();

lcd_condis(" E:",3);

hex_dec_pow(ene);

```

```

ser_contxn(" Energy:",8);

ser_txn(ptt+0x30);

ser_txn(pth+0x30);

ser txn(ph+0x30);

ser_txn(pt+0x30);

ser_txn('.');

ser_txn(po+0x30);

ser_contxn("

",6);

eeprom wr(0x00,ptt);

eeprom_wr(0x01,pth);

eeprom wr(0x02,ph);

eeprom wr(0x03,pt);

eeprom_wr(0x04,po);

if(ene \ge 10000)

kw=ene/10000;

tkw=tkw+kw;

enel=ene%10000;

PORTD=0xc7;

lcd_rd();

lcd_condis(" E:",3);

hex_dec_pow(ene);

hex_dec_ap(tkw);

```

```

eeprom wr(0x08,ptt);

eeprom wr(0x09,pth);

eeprom_wr(0x0a,ph);

eeprom_wr(0x0b,pt);

eeprom wr(0x0c,po);

}

if(key2==0 && k2==0) k2=1;

if(key2==1 \&\& k2==1)

{

k2=0;

if(tkw>0 && tkw<=50)

PORTD=0x01;

lcd_rd();

PORTD=0x80;

lcd_rd();

lcd_condis("UNITS:",6);

hex_dec ap(tkw);

lcd disp(ptt+0x30);

lcd disp(pth+0x30);

lcd disp(ph+0x30);

lcd_disp(pt+0x30);

lcd_disp(po+0x30);

cost=tkw*65;

PORTD=0xc0;

```

```

lcd_rd();

hex_dec_cost(cost);

ser_contxn(" Cost:",6);

ser_txn(ptt+0x30);

ser_txn(pth+0x30);

ser_txn(ph+0x30);

ser_txn('.');

ser txn(pt+0x30);

ser_txn(po+0x30);

",6);

ser_contxn("

delay(50000);

delay(50000);

delay(50000);

delay(50000);

PORTD=0x01;

lcd_rd();

}

else if(tkw>50)

{

PORTD=0x01;

lcd rd();

PORTD=0x80;

lcd rd();

lcd condis("UNITS:",6);

hex_dec_ap(tkw);

```

```

lcd disp(ptt+0x30);

lcd disp(pth+0x30);

lcd_disp(ph+0x30);

lcd_disp(pt+0x30);

lcd_disp(po+0x30);

cost=tkw*75;

PORTD=0xc0;

lcd rd();

hex_dec_cost(cost);

ser contxn(" Cost:",6);

ser_txn(ptt+0x30);

ser_txn(pth+0x30);

ser txn(ph+0x30);

ser_txn('.');

ser_txn(pt+0x30);

ser_txn(po+0x30);

ser_contxn("

",6);

delay(50000);

delay(50000);

delay(50000);

delay(50000);

PORTD=0x01;

lcd rd();

```

}

```

void lcd_init()

TRISD=0;

PORTD=0x38;

lcd_rd();

PORTD=0x0c;

lcd_rd();

PORTD=0x06;

lcd_rd();

PORTD=0x01;

lcd_rd();

PORTD=0x80;

lcd_rd();

}

void lcd_disp(unsigned char lr)

PORTD=lr;

lcd_wr();

void lcd_condis(const unsigned char *word,unsigned int n)

{

```

```

for(i=0;i<n;i++)

PORTD=word[i];

lcd wr();

void lcd rd()

DISDAT;

//send data to lcd data lines

//to select rs,rw=0;en=1

PORTD=0x04;

DISCTR;

//send data to ctrl lines

delay(125);

//t0 select rs,re,en=0

PORTD=0x00;

DISCTR;

//send data to ctrl lines

void lcd_wr()

DISDAT;

//send data to lcd data lines

//to select rs=1,rw=0,en=1;

PORTD=0x05;

//send data to ctrl lines

DISCTR;

delay(125);

PORTD=0x01;

//to select rs=1,rw=0,en=0;

//send data to ctrl lines

DISCTR;

```

```

void hex dec(unsigned char val)

h=val/100;

hr=val%100;

t≔hr/10;

o=hr%10;

lcd_disp(h+0x30);

lcd_disp(t+0x30);

lcd_disp(o+0x30);

}

void hex_dec_curr(unsigned int vai)

h=vai/100;

hr=vai%100;

t=hr/10;

o=hr%10;

lcd_disp(h+0x30);

lcd_disp(t+0x30);

lcd_disp('.');

lcd_disp(o+0x30);

}

void hex dec cost(unsigned int pv)

{

```

```

// unsigned int pttr,pthr,phr;

ptt=pv/10000;

pttr=pv%10000;

pth=pttr/1000;

pthr=pttr%1000;

ph=pthr/100;

phr=pthr%100;

pt=phr/10;

po=phr%10;

lcd_disp(ptt+0x30);

lcd disp(pth+0x30);

lcd_disp(ph+0x30);

lcd_disp('.');

lcd_disp(pt+0x30);

lcd_disp(po+0x30);

}

void hex_dec_pow(unsigned int pv)

{

unsigned int pttr,pthr,phr;

ptt=pv/10000;

pttr=pv%10000;

pth=pttr/1000;

pthr=pttr%1000;

```

```

ph=pthr/100;

phr=pthr%100;

pt=phr/10;

po=phr%10;

lcd_disp(ptt+0x30);

lcd_disp(pth+0x30);

lcd_disp(ph+0x30);

lcd_disp(pt+0x30);

lcd_disp('.');

lcd_disp(po+0x30);

}

void hex_dec_ap(unsigned int pv)

ptt=pv/10000;

pttr=pv%10000;

pth=pttr/1000;

pthr=pttr%1000;

ph=pthr/100;

phr=pthr%100;

pt=phr/10;

po=phr%10;

void hex dec pf(int pfval)

{

```

```

h=pfval/100;

hr=pfval%100;

t=hr/10;

o=hr%10;

lcd disp(h+0x30);

lcd_disp('.');

lcd_disp(t+0x30);

lcd_disp(o+0x30);

}

void eeprom_wr(unsigned char addr,unsigned char wlr)

GIE=0;

//desable all interrupts

EEPGD=0;

//access EEPROM data memory

EEADR=addr;

//select memory location to store setpoint

EEDATA=wlr;

WREN=1;

EECON2=0x55;

//for enable write cycle

EECON2=0xaa;

//

//start write operation

WR=1;

while(!EEIF); //wait until write is finished

EEIF=0;

WREN=0;

GIE=1;

```

```

char eeprom_rd(unsigned char radd)

{

EEADR=radd;

//select memory location to store setpoint

//access EEPROM data memory

EEPGD=0;

RD=1;

q=EEDATA;

//read the setpoint

return(q);

}

void ser_txn(unsigned char te)

{

SPBRG=51;

//for 1.2 kb baud rate

BRGH=0;

//for low baud rate

SYNC=0;

//asynchronous mode

//Enable the serial port

SPEN=1;

// TX9=1;

//enable the ninth data bit

TXEN=1;

//enable TXion

TXREG=te;

delay(2500);

TXIF=0;

}

void ser_contxn(const unsigned char *dat,unsigned int m)

unsigned int j;

for(j=0;j < m;j++)

```

```

TXREG=dat[j];

delay(1500);

}

void delay(unsigned int del)

{

while(del--);

}

```

**CONCLUSION**

## **CHAPTER 7**

#### CONCLUSION

Thus the system calculates the energy utilization of a consumer over a certain period and its corresponding cost is calculated according to the tariff imposed. The system also monitors the electrical parameters like voltage, current, power factor, power, energy and also the actual cost of consumption bypassing the need for manual calculation. The system is interfaced with the personal computer and the data's are transferred to the computer through serial communication.

# 7.1 FUTURE ENHANCEMENT

# 1. ATTACHING A PRINTER FOR BILLING:

A printer can be attached to enable direct printing of the electrical parameters like voltage, current, power, energy, no of units consumed, cost and even the meter number and the EB division.

#### 2. CUTTING THE LOADS AUTOMATICALLY:

Various luxury electrical appliances which consume high power can be cut off at predetermined rates with the help of relays interfaced the micro controller.

**APPENDIX**

# PIC16F87X

### 28/40-pin 8-Bit CMOS FLASH Microcontrollers

#### Devices Included in this Data Sheet:

- PIC16F873

- PIC16F876

- PIC16F874

- PIC16F877

#### Microcontroller Core Features:

- High-performance RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two cycle

- Operating speed: DC 20 MHz clock input

DC 200 ns instruction cycle

- Up to 8K x 14 words of FLASH Program Memory,

Up to 368 x 8 byles of Data Memory (RAM)

Up to 256 x 8 byles of EEPROM data memory

- Pinout compatible to the PIC16C73B/74B/76/77

- Interrupt capability (up to 14 sources)

- Eight level deep hardware stack

- Direct, indirect and relative addressing modes.

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code-protection

- Power saving SLEEP mode

- · Selectable oscillator options

- Low-power, high-speed CMOS FLASH/EEPROM technology

- Fully static design

- In-Circuit Serial Programming™ (ICSP) via two nins

- · Single 5V in-Circuit Serial Programming capability

- · In-Circuit Debugging via two pins

- Processor read/write access to program memory

- Wide operating voltage range: 2.0V to 5.5V

- · High Sink/Source Current: 25 mA

- Commercial and Industrial temperature ranges

- Low-power consumption:

- < 2 mA typical @ 5V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- < 1 μA typical standby current

#### Pin Diagram

#### Peripheral Features:

- Timer0: 8-bit timer/counter with 8-bit prescaler.

- Timer1: 16-bit itmer/counter with prescaler, can be incremented during sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules

- Capture is 16-bit, max resolution is 12.5 ns.

- Compare is 16-bit, max resolution is 200 ns.

- PWM max, resolution is 10-bit

- 10-bit multi-channel Analog-to-Digital converter.

- Synchronous Sertal Port (SSP) with SPI<sup>®</sup> (Master Mode) and I<sup>2</sup>C<sup>®</sup> (Master/Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with 9-bit address detection

- Parallel Slave Port (PSP) 8-bits wide, with external RD, WR and CS controls (40.44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

TABLE 1-1: PIC16F873 AND PIC16F876 PINOUT DESCRIPTION

| Pin Name           | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-------------|--------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN         | 9           | 9            |               | STYCMCG(*)     | Oscillator crystal input/external alock source input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSC2/CLKOUT        | 10          | 10           | 0             |                | Ose lister crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKCUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MOLEV PROTHV       | 1           | 1            | MP            | aT             | Master clear (reset) input or programming voltage input or high<br>voltage test mode control. This pin is an active low reset to the<br>device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Danielm            |             |              | 1             |                | PORTA is a bi-directional VO port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RADVANO<br>RAT/ANT | 2           | 2            | NO            | TTL            | RAO can also be analog inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAZYANZ/VRET-      | 3           | 3.           | PO.           | TTL            | PA1 can also be analog input t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | 4           | *            | 1/0           | TTL            | RA2 dan also be analog input2 or negative analog reference<br>voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RAS/ANSWREF+       | 5           | 5            | 1/0           | TTL            | RAS can also be analog input3 or positive analog reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RA4/TOCKI          | 6           | 6            | 1/0           | ST             | RA4 est also be the clock input to the TimerO module. Outputs open drain type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RASSS/AN4          | 7           | 7            | 1/0           | TTL            | RA5 can also be analog input4 or the stave select for the<br>synchronous sarial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    |             |              |               |                | PORTB is a bi-directional I/O port. PORTB can be software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RBOINT             | 21          |              |               |                | programmed for internal week pull-up on all inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |