P-1439

# COLLISION PREVENTION AND GATE SECURITY IN RAILWAY

#### A PROJECT REPORT

Submitted by

P.MALATHI

-71201105022

**V.RAJESWARI**

-71201105040

V.T.VADIVUKKARASI

-71201105066

in partial fulfillment for the award of the degree

of

#### BACHELOR OF ENGINEERING

in

#### ELECTRICAL AND ELECTRONICS ENGINEERING

Under the guidance of

Mr.C.UdhayaShankar

KUMARAGURU COLLEGE OF TECHNOLOGY, COIMBATORE

ANNA UNIVERSITY: CHENNAI 600 025

APRIL 2005

# ANNA UNIVERSITY : CHENNAI-600 025 BONAFIDE CERTIFICATE

Certified that this project report titled "COLLISION PREVENTION AND GATE SECURITY IN RAILWAY" is the bonafide work of

P.MALATHI

- Register No. 71201105022

V.RAJESWARI

Register No. 71201105040

V.T.VADIVUKKARASI

Register No. 71201105066

who carried out the project work under my supervision.

MEMF 814105

Signature of the Head of the Department

and reality reality

Signature of the guide

Prof.K.Regupathy Subramanian, B.E., M.Sc.

DEAN/EEE, Kumaraguru college of technology. Mr.C.UdhayaShankar, M.Tech.

Lecturer, EEE,

Kumaraguru college

of technology.

#### CERTIFICATE OF EVALUATION

College : KUMARAGURU COLLEGE OF TECHNOLOGY

**Branch**: Electrical And Electronics Engineering

Semester : Eighth semester

| Sl.No. | Name of the students | Title of the project    | Name of the supervisor with designation |

|--------|----------------------|-------------------------|-----------------------------------------|

| 01     | P.MALATHI            | "Collision              |                                         |

| 02     | V.RAJESWARI          | prevention<br>and Gate  | Mr.C.UDHAYASHANKAR<br>LECTURER.         |

| 03     | V.T.VADIVUKKARASI    | security in<br>Railway" |                                         |

The report of the project work submitted by the above students in partial fulfillment for the award of Bachelor of Engineering degree in Electrical and Electronics Engineering of Anna University were evaluated and confirmed to be report of the work done by the above students and then evaluated.

(INTERNAL EXAMINER)

(EXTERNAL EXAMINER)

# DEDICATED TO OUR BELOVED PARENTS AND WELL WISHERS

#### **ACKNOWLEDGEMENT**

The successful completion of our project can be attributed to the combined efforts made by us and the contribution made in one form or the other, by the individuals we hereby acknowledge.

We are highly privileged to thank Dr.K.K.Padmanabhan, B.Sc., (Engg)., M.Tech., Ph.D., MISTE and F.I.E principal, Kumaraguru College of Technology for providing the necessary facilities for successful completion of the project.

We express our heartfelt gratitude and thanks to the Head of Electrical and Electronics Department, Dr.T.M.Kameswaran, B.E., M.Sc (Engg)., Ph.D., F.I.E., for encouraging us to choose this project and for being with us right from the beginning of the project and guiding us at every step.

We wish to express our deep sense of gratitude and indebtedness to the Dean, Electrical and Electronics Department, Prof.K.RegupathySubramaniam, B.E (Hons)., M.Sc., for his enthusiasm and encouragement, which has been instrumental in the success of the project.

We wish to place on record our deep sense of gratitude and profound thanks to our guide Mr.C.UdhayaShankar, M.Tech., Lecturer, Electrical and Electronics department, for his valuable guidance, constant encouragement, continuous support and co-operation rendered throughout the project.

We are also thankful to all teaching and non teaching staffs of Electrical and Electronics engineering department for their kind help and encouragement in making our project successful.

Last but not least we extend our sincere thanks to all our parents and friends who have contributed their ideas and encouraged us for completing the project successfully.

#### **ABSTRACT**

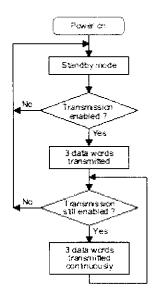

The main objective of our project is to avoid the number of railway accidents occurring in the unmanned level crossings by providing necessary and detailed information regarding the train arrival and its current position to the public at the gate and also to prevent the direct collision occurring between the two trains traveling in the same track.

The gate control part is done by glowing appropriate LEDs relevant to the train position and switching ON the buzzer at appropriate time along with automated gate closing. The information regarding the time that will be taken for the train to reach the gate and its velocity will be displayed at the gate using LCD display continuously. The opening and closing of the gate will be controlled using servomotor operated by relays.

The collision prevention part is done by transmitting and receiving the train and track number information within a particular area, so that if any train comes in the same track, further enhancements can be done either to stop the train or to change the track. The microcontroller used here is ATMEL 89C51.

## TABLE OF CONTENTS

| CHAPTER NO. | TITLE                                | PAGE NO. |

|-------------|--------------------------------------|----------|

|             | ABSTRACT                             | vi       |

|             | LIST OF TABLES                       | ix       |

|             | LIST OF FIGURES                      | ix       |

| 1.          | INTRODUCTION                         |          |

|             | 1.1.A strategy of railway            |          |

|             | accidents in India                   | 1        |

|             | 1.2. Need for our project.           | 3        |

| 2.          | PROJECT DESCRIPTION                  |          |

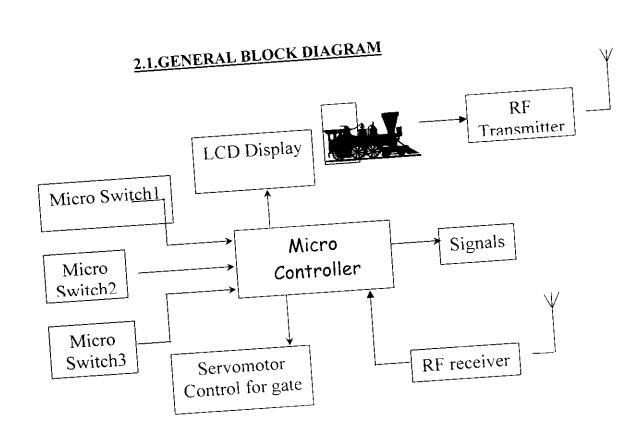

| 4.          | 2.1. General block diagram           | 5        |

|             | 2.2. Introduction to Microcontroller | 6        |

|             | 2.3. LCD display                     | 14       |

|             | 2.4. Servo motor                     | 16       |

|             | 2.5. Circuit explanation             |          |

|             | 2.5.1.Power supply circu             | uit 17   |

|             | 2.5.2.Relay circuit                  | 20       |

|             | 2.5.3 Keypad                         | 21       |

|             | 2.5.4.RF Transmitter                 | 23       |

| 2.5.5.RF Receiver 2        | 4  |

|----------------------------|----|

| 2.6.Main circuits          |    |

| 2.6.1.Transmitter circuit  | 25 |

| 2.6.2.Receiver circuit     | 26 |

| 2.6.3.Gate control circuit | 30 |

| 2.7. Software description  |    |

| 2.7.1.Gate control         | 32 |

| 2.7.2.Transmitter          | 43 |

| 2.7.3.Receiver             | 45 |

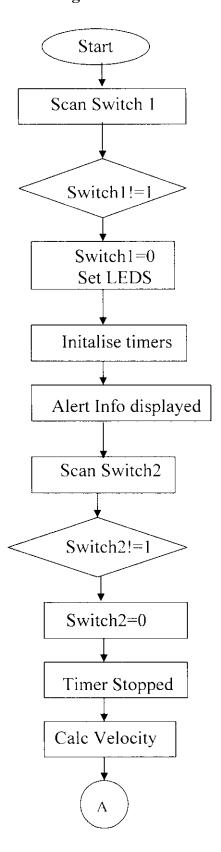

| 2.7.4. Flow chart          | 49 |

| 3. CONCLUSION AND FUTURE   |    |

| ENHANCEMENTS               | 51 |

| 4. APPENDICES              | 52 |

| 5. REFERENCES              | 79 |

#### List of tables

| Serial no. | Title                                      | page no. |

|------------|--------------------------------------------|----------|

| 2.1        | Interrupt Enable Register                  | 12       |

| 2.2        | Positive Voltage Regulators in 7800 series | 19       |

|            | List of figures                            |          |

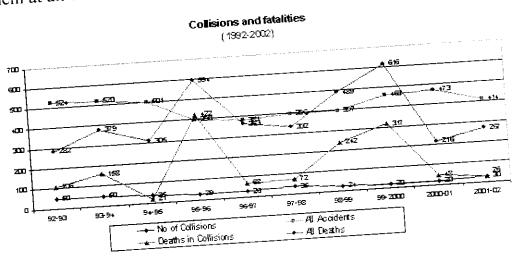

| 1.1        | Collisions and fatalities                  | 2        |

| 2.1        | General Block Diagram                      | 5        |

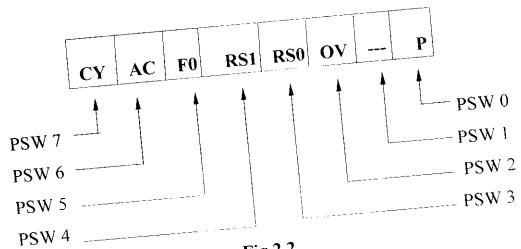

| 2.2        | Program Status Word                        | 11       |

| 2.3        | 5V power supply                            | 18       |

| 2.4        | Fixed positive voltage regulator           | 18       |

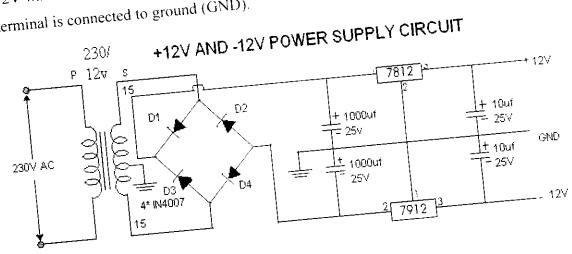

| 2.5        | +12V and -12V power supply                 | 19       |

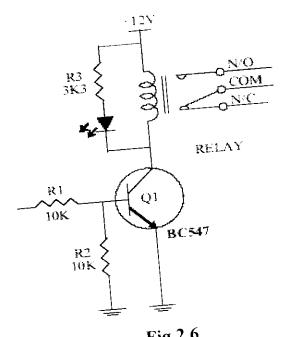

| 2.6        | Relay circuit                              | 20       |

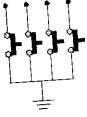

| 2.7        | Keypad                                     | 21       |

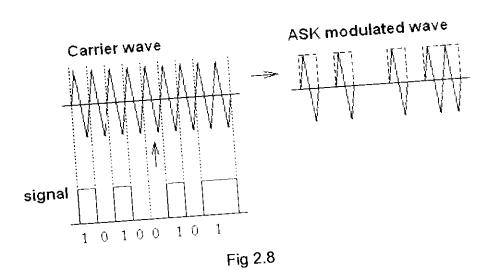

| 2.8  | ASK modulation         | 22 |

|------|------------------------|----|

|      | RF Transmitter circuit | 23 |

| 2.9  | RF Receiver circuit    | 24 |

| 2.10 |                        | 25 |

| 2.11 | Transmitter circuit    | 26 |

| 2.12 | Receiver circuit       | 30 |

| 2.13 | Gate control circuit   |    |

| 2.14 | Flow chart             | 49 |

#### CHAPTER 1

#### INTRODUCTION:

## 1.1.A strategy of railway accidents in India:

Accident is an occurrence in the course of working of Railway which does or may affect the safety of the Railway passengers or servants or which affect the safety of others, or which does or may cause delay to a train or loss to the Railway. The term 'accident' envelopes a wide spectrum of occurrences or consequences not necessarily leading to a mishap. 'Failures of railway equipment' are also treated as technical and potential 'accidents' for the purposes of managing the assets safely. Asset failures are continuously monitored and efforts made to oversee that they do not cause actual accidents. Consequential train accidents include train accidents having serious repercussion in terms of loss of human life, injury, damage to Railway property or interruption to rail traffic of laid down threshold levels and values. These consequential train accidents include Collision, Derailments, Fire in Trains, Collisions of trains at Level Crossings and few miscellaneous incidents. All other train accidents, which are below the threshold values, are treated as "other train accidents". Such categorization is, broadly, in consonance with practices adopted in many of world railways, though varying in details and degree. Indicative Accidents, distinct from Consequential Train Accidents include all cases of 'train passing signal at danger', 'averted collision', breach of block rules etc.

Collisions are the most dreaded accidents for any railway-man. These can be 'side collisions', 'Rear-end' and 'head-on collisions'.

Trains ramming into another from behind are called rear-end collisions, while trains colliding on the same track from opposite ends, are called head-on collisions and are the most fatal of all accidents. Side collisions can occur either in station area, while converging or diverging or by fouling the adjacent track in multiple lines territory. Rear-end collisions and head-on collisions can occur at stations or between the stations. Of the total consequential train accidents, that occurred during the last decade, the percentage of collisions involving passenger carrying trains was 4% only, but they are highly volatile mishaps and call for necessary steps to prevent them at all costs.

Fig. 1.1

Of the total consequential train accidents, that occurred during the last decade, the accidents at *level crossings* were about 16%. Accidents at manned level crossings were at the level of 4% of the total consequential train accidents, whereas unmanned level crossings accidents shared 12% of mishaps.

Accidents at unmanned level crossings occur primarily due to dashing of road vehicles with the oncoming trains and cause fatality of the road user. A road vehicle driver, though having the advantage of

maneuverability and lesser braking distances and shorter reaction time as compared to train drivers, fails to maintain the level of alertness, normally expected, while crossing such intersections, where he is supposed to take necessary precautions as stipulated in the Motor Vehicles Act 1988. It has been observed that over 85% of all accidents occurring at unmanned level crossings, involved passenger carrying trains, reflecting that the road vehicle drivers normally misjudge the speed of the oncoming trains and take chances while crossing the rail track.

On an average, every year, 141 persons died and 158 injured in the accidents occurring at unmanned level crossings only during the last decade, contributing a share of 37% of the total fatalities in all accidents. 9% of the total fatalities occurred in manned level crossing accidents, thus indicating that 46% of train accident fatalities take place at rail-road intersections only.

#### 1.2.NEED FOR OUR PROJECT:

Whether it is systems failure or human error that causes accidents, experts believe a majority of them could have been avoided if proper signaling equipment was installed. Trains are recklessly added, but the corresponding investment in technology and equipment, which will automatically ensure safety, is disregarded. A growing network, populist demands and poor funds have given the Indian Railways a bloody track record in the past decade. Since 1986, railway ministry reveal more than 5,000 people have died in train accidents across the country.

India has the second-largest rail network in the world and it transports the largest number of passengers – four billion people – annually. Rail experts argue that accidents will inevitably occur in such a mammoth system.

"While sophisticated communication and automation systems have considerably reduced the number of accidents in the West, there has been a steep increase in the number of accidents in India," says Rajmani Singh who retired from the Railway Board last year.

Thus from the data as seen above tells us the importance of safety measures to be adopted in railways. If that is automated, then it becomes easier to control the disasters. The size and complexity of the previous operations, growing traffic and changing technologies, placed previous a heavy burden on manual information system. So need for modernization in such systems is important now a days.

In **our project**, the *time* taken for the train to cover the *distance* that is already known between two keys is sensed using the timers. From the distance and the time known, the *velocity of the train* can be calculated. Thus the time that will be taken for the train to reach the gate is known approximately and the status of the train can be displayed at the gate location. This is a part of the project. And the other is that the *transmitter* kept at one train transmits the train information to the *receiver* kept at the other train if traveling in the same track at a reasonable distance. This will be useful to stop the trains by some mechanism or the other. Microcontroller employed for this purpose is 89C51.

#### **CHAPTER 2**

## PROJECT DESCRIPTION:

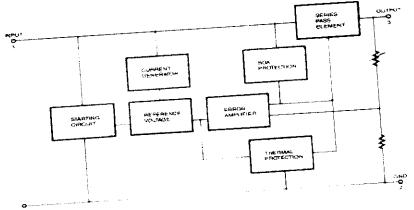

Fig 2.1

.

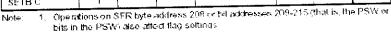

# 2.2.INTRODUCTION TO MICROCONTROLLER

A Micro controller consists of a powerful CPU tightly INTRODUCTION: coupled with memory RAM, ROM or EPROM, various I / O features such as Serial ports, Parallel Ports, Timer/Counters, Interrupt Controller, Data Acquisition interfaces-Analog to Digital Converter (ADC), Digital to Analog Converter (DAC), everything integrated onto a single Silicon Chip.

Any microcomputer system requires memory to store a sequence of instructions making up a program, parallel port or serial port for communicating with an external system, timer / counter for control purposes like generating time delays, Baud rate for the serial port, apart from the controlling unit called the Central Processing Unit

## ADVANTAGES OF MICROCONTROLLERS:

1. If a system is developed with a microprocessor, the designer has to go for external memory such as RAM, ROM or EPROM and peripherals and hence the size of the PCB will be large enough to hold all the required peripherals. But, the micro controller has got all these peripheral facilities on a single chip so development of a similar system with a micro controller reduces PCB size and cost of the

One of the major differences between a micro controller and a design. microprocessor is that a controller often deals with bits, not bytes as in the real world application, for example switch contacts can only be open or close, indicators should be lit or dark and motors can be either turned on or off and so forth.

# INTRODUCTION TO ATMEL MICROCONTROLLER

SERIES: 89C51 Family

TECHNOLOGY: CMOS

# The major Features of 8-bit Micro controller ATMEL 89C51:

- 8 Bit CPU optimized for control applications

- Extensive Boolean processing (Single bit Logic) Capabilities.

- On Chip Flash Program Memory

- On Chip Data RAM

- Bi-directional and Individually Addressable I/O Lines

- Multiple 16-Bit Timer/Counters

- Full Duplex UART

- Multiple Source / Vector / Priority Interrupt Structure

- On Chip Oscillator and Clock circuitry.

- On Chip EEPROM

- SPI Serial Bus Interface

- Watch Dog Timer

#### MEMORY ORGANIZATION:

\* Logical Separation of Program and Data Memory \*

All Atmel Flash micro controllers have separate address spaces for program and data memory. The logical separation of program and data memory allows the data memory to be accessed by 8 bit addresses. Which can be more quickly stored and manipulated by an 8 bit CPU Nevertheless 16 Bit data memory addresses can also be generated through the DPTR register.

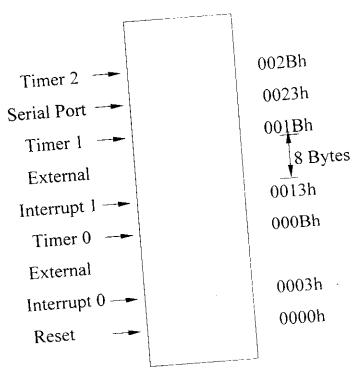

Fig shows the map of the lower part of the program memory, after PROGRAM MEMORY: reset, the CPU begins execution from location 0000h. As shown in Fig each interrupt is assigned a fixed location in program memory. The interrupt causes the CPU to jump to that location, where it executes the service routine. External Interrupt 0 for example, is assigned to location 0003h. If external Interrupt 0 is used, its service routine must begin at location 0003h. If the interrupt in not used its service location is available as general-purpose

The interrupt service locations are spaced at 8 byte intervals program memory. 0003h for External interrupt 0, 000Bh for Timer 0, 0013h for External interrupt 1,001Bh for Timer1, and so on.

Longer service routines can use a jump instruction to skip over subsequent interrupt locations. If other interrupts are in use. The lowest addresses of program memory can be either in the on-chip Flash or in an external memory. To make this selection, strap the External Access (EA) pin to either Vcc or GND. For example, in the AT89C51 with 4K bytes of onchip Flash, if the EA pin is strapped to Vcc, program fetches to addresses 0000h through 0FFFh are directed to internal Flash. Program fetches to addresses 1000h through FFFFh are directed to external memory.

#### DATA MEMORY:

The Internal Data memory is dived into three blocks namely,

- The lower 128 Bytes of Internal RAM. •\*•

- The Upper 128 Bytes of Internal RAM. **\*** \*

- Special Function Register. \*

#### 89C51 MEMORY STRUCTURE

#### ADDRESSING MODES:

#### DIRECT ADDRESSING:

In direct addressing, the operand specified by an 8-bit address field in the instruction. Only internal data RAM and SFR's can be directly addressed.

#### INDIRECT ADDRESSING:

In Indirect addressing, the instruction specifies a register that contains the address of the operand. Both internal and external RAM can indirectly address. The address register for 8-bit addresses can be either the Stack Pointer or R0 or R1 of the selected register Bank. The address register for 16-bit addresses can be only the 16-bit data pointer register, DPTR.

Program memory can only be accessed via indexed addressing this INDEXED ADDRESSING: addressing mode is intended for reading look-up tables in program memory. A 16 bit base register (Either DPTR or the Program Counter) points to the base of the table, and the accumulator is set up with the table entry number. Adding the Accumulator data to the base pointer forms the address of the table entry in program memory.

REGISTER INSTRUCTION: The register banks, which contains registers R0 through R7, can be accessed by instructions whose opcodes carry a 3-bit register specification. Instructions that access the registers this way make efficient use of code, since this mode eliminates an address byte. When the instruction is executed, one of four banks is selected at execution time by the row bank select bits in PSW.

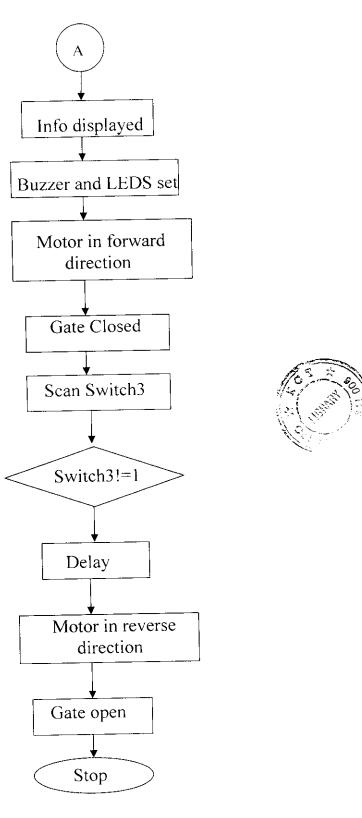

## PROGRAM STATUS WORD:

Program Status Word Register in Atmel Flash Micro controller:

The Program Status Word contains Status bits that reflect the current status of the CPU. The PSW shown in Fig resides in SFR space. The PSW contains the Carry Bit, The auxiliary Carry (For BCD Operations) the two register bank select bits, the Overflow flag, a Parity bit and two user Definable status Flags.

Fig 2.2

PSW 0: Parity of Accumulator Set By Hardware To 1 if it contains an Odd number of 1s, Otherwise it is reset to 0.

PSW1: User Definable Flag

PSW2: Overflow Flag Set By Arithmetic Operations

PSW3: Register Bank Select

PSW4: Register Bank Select PSW5: General Purpose Flag.

PSW6: Auxiliary Carry Flag Receives Carry Out from

Bit 1 of Addition Operands

PSW7: Carry Flag Receives Carry Out From Bit 1 of ALU Operands.

The Carry Bit, in addition to serving as a Carry bit in arithmetic operations also serves the as the "Accumulator" for a number of Boolean Operations .The bits RS0 and RS1 select one of the four register banks. A number of instructions register to these RAM locations as R0 through R7. The status of the RS0 and RS1 bits at execution time determines which of the four banks is selected.

The Parity bit reflect the Number of 1s in the Accumulator .P=1 if the Accumulator contains an even number of 1s, and P=0 if the Accumulator contains an even number of 1s. Thus, the number of 1s in the Accumulator plus P is always even. Two bits in the PSW are uncommitted and can be used as general-purpose status flags.

The AT89C51 provides 5 interrupt sources: Two External interrupts, INTERRUPTS two-timer interrupts and a serial port interrupts. The External Interrupts INTO and INT1 can each either level activated or transition - activated, depending on bits ITO and IT1 in Register TCON. The Flags that actually generate these interrupts are the IEO and IE1 bits in TCON. When the service routine is vectored to hardware clears the flag that generated an external interrupt only if the interrupt WA transition - activated. If the interrupt was level - activated, then the external requesting source (rather than the on-chip hardware) controls the requested flag. Tf0 and Tf1 generate the Timer 0 and Timer 1 Interrupts, which are set by a rollover in their respective Timer/Counter Register (except for Timer 0 in Mode 3). When a timer interrupt is generated, the on-chip hardware clears the flag that generated it when the service routine is vectored to. The logical OR of RI and TI generate the Serial Port Interrupt. Neither of these flag is cleared by hardware when the service routine is vectored to. In fact, the service routine normally must determine whether RI or TI generated the interrupt and the bit must be cleared in software.

#### IE: Interrupt Enable Register

| 11100.   |    | _   |     |     | T   |

|----------|----|-----|-----|-----|-----|

| EA - ET2 | ES | ET1 | EX1 | ET0 | EX0 |

Enable bit = 1 enabled the interrupt

Enable bit = 0 disables it.

| ymbo | <u>1</u> P | osition |      | Function                                                                                                                                                                                     |

|------|------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA   |            | IE.     | If   | Pal enable / disable all interrupts.  EA = 0, no interrupt will be  Acknowledge.  FEA = 1, each interrupt source is  Individually enabled to deabled by  Setting or clearing its enable bit. |

|      | -          | IE.6    |      | Undefined / reserved                                                                                                                                                                         |

|      | ET2        | IE.5    |      | Timer 2 Interrupt enable Bit                                                                                                                                                                 |

|      | ES         | IE.     | 1    | Serial Port Interrupt enabled bit.                                                                                                                                                           |

| -    | ET1        | IE      | .3   | Timer   Interrupt enable bit.                                                                                                                                                                |

| -    | EX         | 1 11    | E.2  | External Interrupt 1 enable bit.                                                                                                                                                             |

| -    | ET         | 0 1     | E.I  | Timer 0 Interrupt enable bit.                                                                                                                                                                |

|      |            | X0      | IE.0 | External Interrupt 0 enable bit.                                                                                                                                                             |

Table 2.1

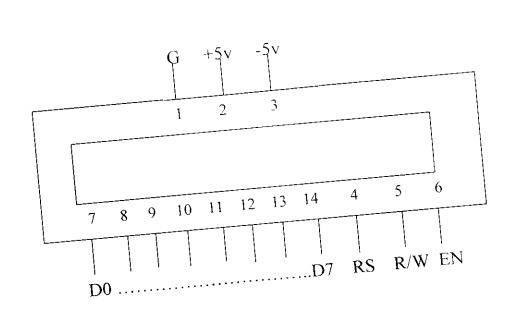

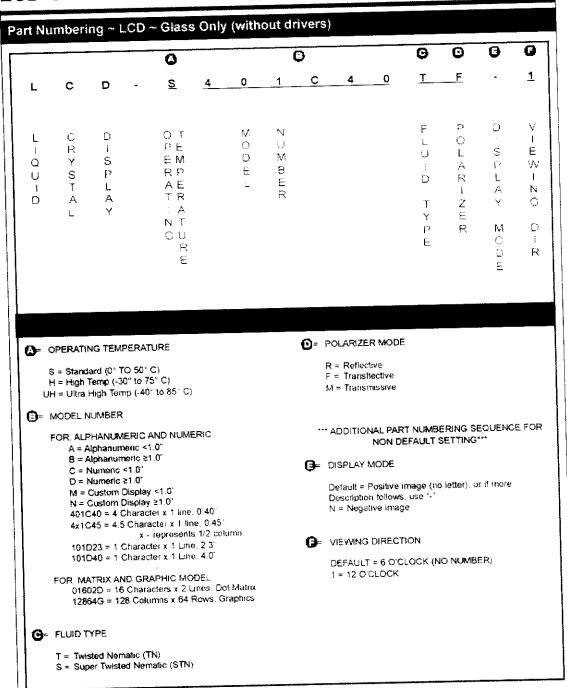

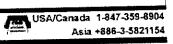

## 2.3.LCD DISPLAY

Short for liquid crystal display, a type of display used digital INTRODUCTION: watches and many portable computers. LCD displays utilize two sheets of polarizing material with a liquid crystal solution between them. An electric current passed through the liquid causes the crystals to align so that light cannot pass through them. Each crystal, therefore, is like a shutter, either allowing light to pass through or blocking the light.

Monochrome LCD images usually appear as blue or dark gray images on top of a grayish-white background. Color LCD displays use two basic techniques for producing color: Passive matrix is the less expensive of the two technologies. The other technology, called thin film transistor (TFT) or active-matrix, produces color images that are as sharp as traditional CRT displays, but the technology is expensive.

When the LCD is in the off state, light rays are rotated by the two polarisers and the liquid crystal, such that the light rays come out of the LCD without any orientation, and hence the LCD appears transparent. When sufficient voltage is applied to the electrodes, the liquid crystal molecules would be aligned in a specific direction. The light rays passing through the LCD would be rotated by the polarisers, which would result in activating /

The LCD's are lightweight with only a few millimeters thickness. highlighting the desired characters. Since the LCD's consume less power, they are compatible with low power electronic circuits, and can be powered for long durations.

The power supply should be of +5V, with maximum allowable transients of 10mv. To achieve a better / suitable contrast for the display, the voltage (VL) at pin 3 should be adjusted properly.

The ground terminal of the power supply must be isolated properly so that no voltage is induced in it. The module should be isolated from the other circuits, so that stray voltages are not induced, which could cause a flickering display.

The LCD variables en, rw and rs are interfaced to the pins 5,6 and 7 pins of the port 2. LCD initialization is done by sending corresponding hexadecimal values .For the display to appear in the first line, 0x80 is to be sent and for second line, 0xc0 is sent. The location at which the display has to appear is to be sent appropriately.

RS – reset

R/W - read/ write

EN - enable

## 2.4.SERVO MOTOR

The motors used for the automatic control systems are called Servomotors. They are used to convert an electrical signal applied to them into an angular displacement of the shaft. They can either operate in a continuous duty or step duty depending on the construction.

In general, a servomotor should have the following features,

- Linear relationship between the speed and the electric control signal.

- Steady state stability

- Wide range of speed control

- Linearity of mechanical characteristics throughout the entire speed

- Low mechanical and electrical inertia and fast response.

There are varieties of servomotors available for control system applications. The suitability of a motor for a particular application depends on the characteristics of the system, the purpose of the system and its operating conditions.

Here, the servomotor is used for the gate control mechanism, which is to open and close the gate. The ON/OFF and the directions of the motor are controlled using two relays respectively. After the train crosses the second switch, the red LED and the buzzer is ON to indicate the train arrival and the motor is made to run in forward direction to close the gate. After the train crosses the third switch and green LED is ON. the motor is made to run in the reverse direction to close the gate.

## 2.5.CIRCUIT EXPLANATION

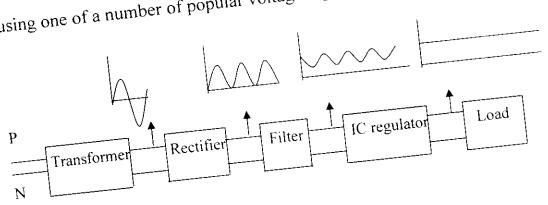

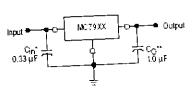

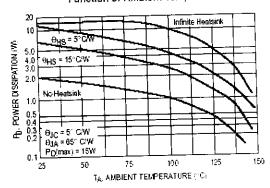

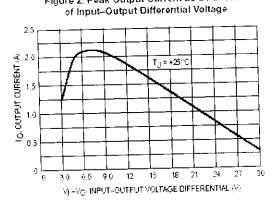

A block diagram containing the parts of a typical power supply and 2.5.1.POWER SUPPLY CIRCUIT: the voltage at various points in the unit is shown. The ac voltage, typically 120 V rms, is connected to a transformer, which steps that ac voltage down to the level for the desired dc output. A diode rectifier then provides a fullwave rectified voltage that is initially filtered by a simple capacitor filter to produce a dc voltage. This resulting dc voltage usually has some ripple or ac voltage variation. A regulator circuit can use this dc input to provide a dc voltage that not only has much less ripple voltage but also remains the same dc value even if the input dc voltage varies somewhat, or the load connected to the output dc voltage changes. This voltage regulation is usually obtained using one of a number of popular voltage regulator IC units.

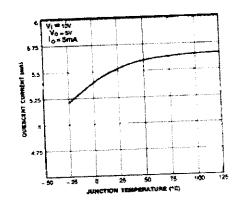

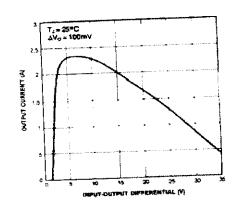

Voltage regulators comprise a class of widely used ICs. Regulator IC IC VOLTAGE REGULATORS: units contain the circuitry for reference source, comparator amplifier, control device, and overload protection all in a single IC. IC units provide regulation of either a fixed positive voltage, a fixed negative voltage.

A power supply can be built using a transformer connected to the ac supply line to step the ac voltage to a desired amplitude, then rectifying that ac voltage, filtering with a capacitor and RC filter, if desired, and finally regulating the dc voltage using an IC regulator. The regulators can be selected for operation with load currents from hundreds of milliamperes to tens of amperes, corresponding to power ratings from mw to tens of watts.

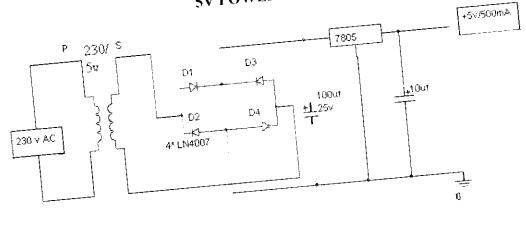

#### 5V POWER SUPPLY

Fig 2.3

## THREE-TERMINAL VOLTAGE REGULATORS:

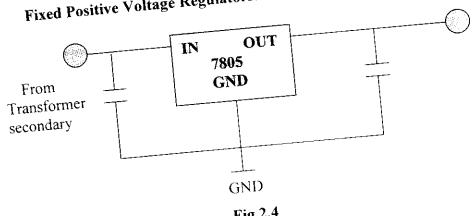

The following Fig shows the basic connection of a three-terminal voltage regulator IC to a load. The fixed voltage regulator has an unregulated dc input voltage, Vi, applied to one input terminal, a regulated output dc voltage, Vo, from a second terminal, with the third terminal connected to ground. For a selected regulator, IC device specifications list a voltage range over which the input voltage can vary to maintain a regulated output voltage over a range of load current.

#### Fixed Positive Voltage Regulators:

Fig 2.4

# Positive Voltage Regulators in 7800 series

| C Part | Output Voltage | Minimum Vi (V) |

|--------|----------------|----------------|

| Crait  | (V)            | 7.3            |

| 7805   | +5             |                |

|        | +6             | 8.3            |

| 7806   | +8             | 10.5           |

| 7808   | +10            | 12.5           |

| 7810   | +12            | 14.6           |

| 7812   |                | 17.7           |

| 7815   | +15            | 21.0           |

| 7818   | +18            | 27.1           |

| 7824   | +24            |                |

The series 78 regulators provide fixed regulated voltages from 5 to 24 V. Figure shows how one such IC. a 7812, is connected to provide voltage regulation with output from this unit of +12V dc. An unregulated input voltage Vi is filtered by capacitor C1 and connected to the IC's IN terminal. The IC's OUT terminal provides a regulated + and connected to the IC's IN terminal. The IC's OUT terminal provides a regulated + 12V which is filtered by capacitor C2 (mostly for any high-frequency noise). The third IC terminal is connected to ground (GND).

Fig 2.5

#### 2.5.2.RELAY CIRCUIT:

Fig 2.6

In this circuit transistor BC547 is used as a switch. The control signal is given to the base terminal of the transistor. The collector is attached to the relay coil. Relays are electromechanical devices. There are two types of relays.

1. Normally closed

We are using normally opened type relay. When the controller output is high the transistor will be in the ON state, so relay is energized. When the controller output from is low the transistor will be in the OFF state, so relay is de-energized. So according to the controller output the relay can be switched ON or OFF, thus giving the required output.

In case of relays used for servo motor control, relay1 is used for ON or OFF of the motor and relay2 is used for forward or reverse rotation of the motor.

#### 2.5.3.KEY PAD

Fig 2.7

The keypad is used in the collision prevention part to enter the train and the track number accordingly and is interfaced with the micro controller. Four keys are placed among which two are used for entering the train number and the other two for entering the track number. Keys 1 and 2 are programmed to enter the train number and 3 and 4 are used for entering the track number. Thus according to the requirement the number of keys can be varied and we can obtain several combinations out of them.

In case of gate control, in the place of sensors, keys are used here at positions 1,2 and 3. The first two keys are used for calculating and displaying the time taken by the train to reach the gate and the train velocity and to close the gate. The third key is used to open the gate after the train leaves the gate.

#### ASK modulation

There are three ways in which the bandwidth of the channel carrier may be altered simply. These techniques give rise to amplitudeshift-keying (ASK), frequency-shift-keying (FSK) and phase-shift-keying (PSK), respectively and ASK is used here.

ASK describes the technique the carrier wave is multiplied by the digital signal f(t). Mathematically, the modulated carrier signal  $\delta(t)$  is:

$$\delta(t) = f(t) \sin(2\Pi fc t + \phi)$$

,  $fc = 433.93MHz$ .

Amplitude modulation has the property of translating the spectrum of the modulation f(t) to the carrier frequency. The bandwidth of the signal remains unchanged. The fact that AM simply shifts the signal spectrum is often used to convert the carrier frequency to a more suitable value without altering the modulation. This process is known variously as mixing, up-conversion or down-conversion. Some form of conversion will always be present when the channel carrier occupies a frequency range outside the modulation frequency range.

## 2.5.4.RF TRANSMITTER CIRCUIT

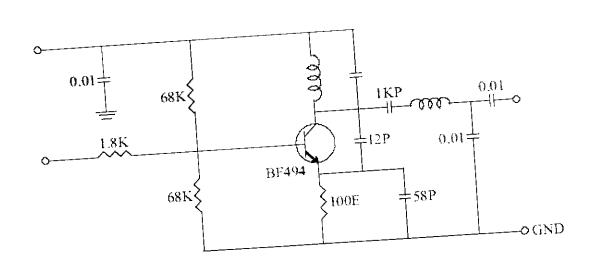

Fig 2.9

The RF Transmitter works on the concept of ASK modulation.

- > It is driven by a single 9V supply from a battery

- > The carrier frequency is 433.9 MHz

- ➤ It uses a common emitter amplifier biased with a voltage divider circuit

- > The parallel circuit components of 0.1mH inductor and 0.01uF capacitor make up the tank circuit

- > The 0.01uF capacitor at the signal entry point is an bypass

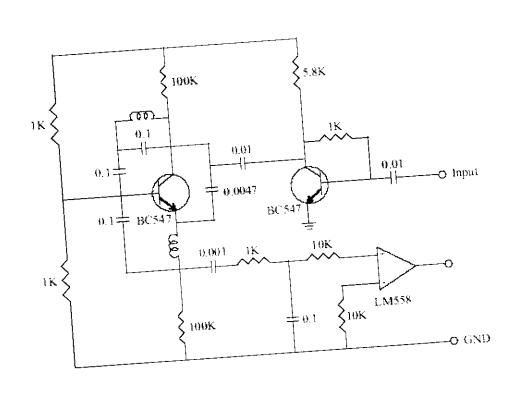

## 2.5.5.RF RECEIVER CIRCUIT

Fig 2.10

- > The circuit consists of a preamplifier that serves two purposes, to give reasonably well-defined input impedance and provide isolation between the oscillations of the super regenerator and the antenna, reducing unwanted radiation.

- > The super-regenerator input is applied to the tank circuit via a small value capacitor to minimize the loading of the circuit.

- > The non-linearity of the device when operated in this mode also detects the AM signals and the output is taken at the biasing resistor and is low pass filtered using an RC network.

#### 2.6. MAIN CIRCUITS

## 2.6.1.TRANSMITTER CIRCUIT

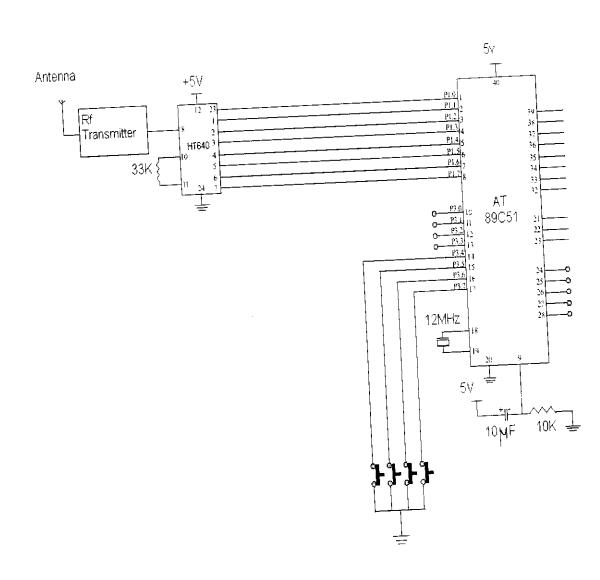

Fig 2.11

Fig 2.12

# **EXPLANATION:**

## TRANSMITTER:

- There are four keys, two for entering the train number and the other two for entering the track number as explained earlier.

- When the train number and the track number are entered, the micro controller sends the entered number to the encoder.i.e., HT640, so that the parallel data is converted to serial for transmission.

- Then the serial data is transmitted through the rf transmitter which is explained earlier.

- The keys 1,2,3 and 4 are connected to the pins 14,15,16 and 17 of the micro controller respectively.

- Two keys are provided with a combination of numbers, which represents the train number.

- The other two keys are programmed with a single digit number, which is the track number.

- When keys 1 and 3 are pressed, then a train number and a track number are transmitted and when keys 1 and 4 are pressed, then the same train number with a different track number is sent.

- similarly for the combinations of key 2 with 3 and 4.

## RECEIVER:

- The transmitted train number and the track number are received through the rf receiver and the data is sent to the decoder i.e., HT648L.

- The serial data is converted to parallel again and then given to the micro controller, with the help of the decoder HT648L.

- The data given to the micro controller is then sent to the LCD display where the entered train number and the track number are displayed.

## ENCODER AND DECODER

## HT640 encoder:

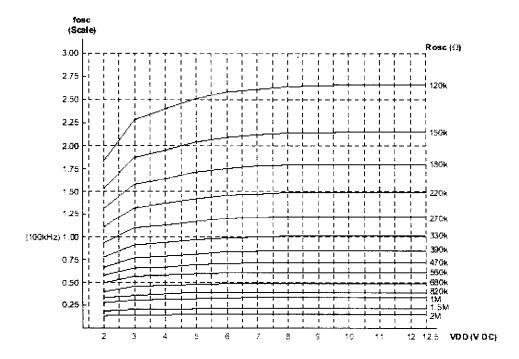

The HT640 encoders are a series of CMOS LSIs for remote control system applications. They are capable of encoding 18 bits of information, which consists of N address bits, and 18 N data bits. Each address/data input is externally programmable if bonded out. It is otherwise set floating internally. The programmable address/ data is transmitted together with the header bits via an RF or an infrared transmission medium upon receipt of a trigger signal. The capability to select a TE trigger type or a DATA trigger type further enhances the application flexibility HT640 Encoder series of encoders.

## **FEATURES:**

- ➤ Operating voltage: 2.4V~12V

- > Low power and high noise immunity CMOS technology

- Low standby current

- > Three words transmission

- Built-in oscillator needs only 5% resistor

- > Easy interface with an RF or infrared transmission media

- > Minimal external components

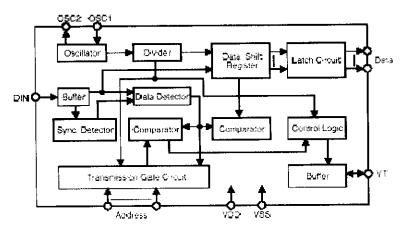

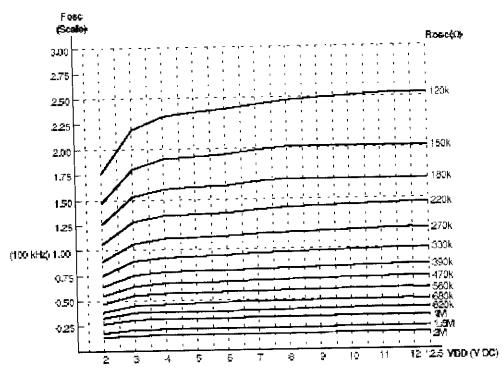

## HT648L decoder:

The HT648L decoders are a series of CMOS LSIs for remote control system applications. They are paired with the 318 series of encoders. The HT648L decoder receives serial address and data from that series of encoders that are transmitted by a carrier using an RF or an IR transmission medium. It then compares the serial input data twice continuously with its local address. If no errors or unmatched codes are encountered, the input data codes are decoded and then transferred to the output pins. The VT pin also goes high to indicate a valid transmission. The HT648L decoders are capable of decoding 18 bits of information that consists of N bits of address and 18 N bits of data.

## **FEATURES:**

- Operating voltage: 2.4V~12V

- Low power and high noise immunity CMOS technology

- Low standby current

- Capable of decoding 18 bits of information

- > 8~18 address pins

- > 0~8 data pins

- Trinary address setting

- Two times of receiving check

- Built-in oscillator needs only a 5% resistor

- Valid transmission indictor

- > Easily interface with an RF or an infrared transmission medium

- Minimal external components

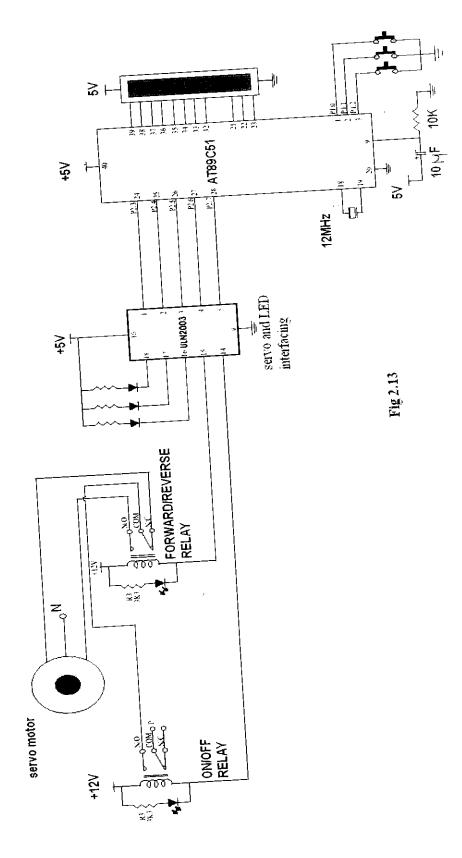

# 2.6.3.GATE CONTROL CIRCUIT

# GATE CONTROL CIRCUIT:

The basic component used for gate control the keys which are provided at the places of the sensors i.e., sensors are provided when used practically. Three keys are employed here each connected to the micro controller. In this case, when the train reaches sensor1, the micro controller starts calculating the time till the train reaches the sensor2. As the distance between the two switches and also the time difference between the two are known, using these information, the micro controller is made to calculate the velocity of the train and the time taken by the train to reach the gate. These two are displayed using LCD display.

After the train leaves the sensor2, the calculated time is decremented such that, when the train reaches the gate, the display shows zero.

To alert the people that the gate is going to close, an alarm system is provided which produces a sound when there is a few seconds to gate closing. Opening and closing of the gate is done by using a servo motor which can be made to rotate in both forward and reverse direction easily through relays. Two relays are used here, one for ON and OFF of the motor and the other one for forward and reverse rotation of the motor.

Three LEDs are provided here, yellow, red and green to glow at corresponding time intervals i.e., when the train reaches the sensor1, sensor2 and when it leaves the sensor3 respectively.

The LEDs are connected to the micro controller through an interface, ULN2003.

# 2.7.SOFTWARE DESCRIPTION:

```

2.7.1.GATE CONTROL:

#include<reg51.h>

void scan_full();

void scan();

void ser_out_st(unsigned char *,unsigned char);

void ser_out(unsigned char);

void ser_init();

void dela(unsigned int);

void chk_ndata_sub();

void display_all();

void chk start();

void chk_ndata();

void htd(unsigned int);

void display();

void read(unsigned char);

void write(unsigned char);

void lcd_init(void);

void lcd_dis(unsigned char *,unsigned char);

void delay(unsigned int);

void del(unsigned char);

//initializing port 2 to lcd variables

sbit en=P2^7;

sbit rw=P2^6;

sbit rs=P2^5;

sbit p7=P1^7;//matrix keys connected to pins of port1

sbit p6=P1^6;

```

```

sbit p4=P1^4;

sbit p3=P1^3;

sbit p0=P1^0;

sbit ndata = P3^4;

// initializing pins of port 2 to LEDs

sbit red = P2^4;//2.2

sbit green = P2^3;//2.1

sbit yellow = P2^2;//2.0

sbit forward = P2^0;//2.4 // forward and reverse bits for motor

sbit reverse = P3^3;//2.3

// initializing port pin to buzzer

sbit buzzer = P2^1;

bit z,y,start_bit,ndata_bit,flag,flag1,forward_bit,key1,key2,key3,one_bit;

unsigned char thous, hund, ten, one, hund_r;

unsigned int thous_r;

unsigned int time, sec, train;

unsigned char datum[5],val,add=0xc5,dtmf,e;

float velocity,time_sec;

main()

{

// buzzer bit initialised

buzzer=0;

forward=reverse=0; // reverse and forward bit initialised

// initializing LCD varaibles

lcd_init();

read(0x01);

while(1)

{

first:

// initialize red and yellow LEDs to zero

red=yellow=0;

// to display at first line of LCD

read(0x80);

lcd_dis("EMBEDDED RAILWAY",16);

```

```

read(0xc0); // to display at second line of LCD

lcd_dis(" CONTROLLER ",16);

val=0;

EA=ET0=1;

// to operate the timer at mode 2

TMOD=0x21;

TH0=TL0=0;

scn:

scan();

if(!key1) goto scn; // scanning key 1

key1=0;

read(0x01);

yellow=1; // yellow LED ON to indicate train is approaching

green=0;

flag=1; // timer in incrementing mode

time=0;

TR0=1; // timer ON

scn1:

scan();

read(0x80); //display at first line

lcd_dis(" ALERT... ",16);

read(0xc1); // display position at second line of LCD

lcd_dis("TIME:",6);

read(0xcB); // display position at second line of LCD

lcd_dis("sec",3);

htd(sec); // fn to convert the hex data to decimal

read(0Xc7);

display();

if(!key2) goto scn1; // if key2 is pressed

```

```

key2=0;

TR0=0;

flag=0;

display_all();

velocity=0.5*3600/sec; // calculating velocity

htd(velocity);

read(0X86);

display();

time_sec=2*3600/velocity; // calculating time to reach the gate

flag1=1; // timer in decrementing mode

time=0;

TR0=1;

scn2:

scan();

if(time_sec==0)

{

TR0=0;

}

htd(time_sec); // hexa to decimal conversion

// display location

read(0XC7);

display();

if(time_sec<=35 && time_sec>30)

buzzer=1; // buzzer ON when 35s remain to reach the gate

Ì

if(time_sec<=30 && time_sec>29)

{

yellow=0; //yellow Led is OFF

```

```

red=1; // Red LED ON when 30s remain to reach the gate

read(0x80);

lcd_dis(" GATE CLOSED ",16);

read(0xc1); //display location at second line

lcd_dis("TIME :",6);

read(0xcB);

lcd_dis("sec",3);

if(one_bit==0) forward_bit=1;

}

if(forward_bit==1)

one_bit=1; // servo motor ON/OFF control

{

forward_bit=0;

// servo motor forward/ reverse control

forward=1;

dela(125); // calling delay fn.

forward=0;

reverse=0;

buzzer=0; // buzzer OFF

}

if(!key3) goto scn2; //scanning key3

key3=0;

time=flag=flag1=0; //reset the flags

TR0=1;

read(0x80); //display at first line

lcd_dis(" GATE OPEN ",16);

read(0xC0);

lcd_dis(" HAPPY JOURNEY ",16);

time=0;

```

```

reverse=1; // motor run in reverse direction

delay(50000); //delay fns. called

delay(50000);

delay(50000);

forward=1; // in forward direction

delay(50000); // delay fns. called

delay(50000);

delay(25000);

forward=0; // forward and reverse bits reset

reverse=0;

time=flag=flag1=sec=time_sec=one_bit=0;

red=0; // red Led is OFF

green=1; // green LED ON to indicate train has crossed the gate

TR1=0; // timers reset

TR0=0;

EA=ET0=0;

TMOD=0; // timer mode reest

TH0=TL0=0;

// continuing scanning process

goto first;

}

void t0_isr(void) interrupt 1 // interrupt service routine

{

TR0=0;

T0 = 0;

if(flag==1 && time>=0x10) //timer in incrementing mode

time++;

{

```

```

time=0;

sec++;

if(sec>=999) sec=999;

if(flag1==1 && time>=0x10) // timer in decrementing mode

time=0;

time_sec--;

if(time_sec==0xffff) time_sec=0;

}

TR0=1;

}

//display fn.

void display()

{

write(hund+0x30);

write(ten+0x30);

write(one+0x30);

// hexa to decimal conversion

void htd(unsigned int hex_val)

thous=hex_val/1000;

thous_r=hex_val%1000;

hund=thous_r/100;

hund\_r = thous\_r\% 100;

ten=hund_r/10;

one=hund_r%10;

ì

```

```

void delay(unsigned int b)// the only delay routine, which is user variable &

is decided by the values given in the brackets

{

do b-=1;

while (b!=0);

void del(unsigned char del) // delay fn.

while(del--)

delay(65000);

}

void lcd_init() //initialisng LCD display

{

read(0x38);

// reading at appropriate locations

read(0x06);

read(0x0c);

void read(unsigned char i) // read fn.

{

P0=i;

// enable bit high

en=1;

// disable reset and read write bits

rs=rw=0;

delay(125); // delay fn. called

en=0; // enable bit low

delay(125);

```

```

void write(unsigned char i) //write fn.

P0=i;

en=rs=1; // enable and reset bit high

rw=0; // read write bit low

delay(125); // delay fn. called

en=0; //enable bit low

delay(125);

void lcd_dis(unsigned char *mess,unsigned char n)

{

unsigned char i; // i is the character to be displayed

for(i=0;i \le n;i++) // n is the no. of characters to be displayed

write(mess[i]);

delay(255); // delay fn. called

}

}

void display all()

{

read(0x80); // display at first line

Km/h ",16);

lcd dis("SPEED:

read(0xc0); // display at second line

lcd_dis(" TIME :000 sec ",16);

void dela(unsigned int del)

while(del--)

```

```

htd(time_sec); // hexa to decimal conversion

read(0XC7);

display();

void ser_init()

//e6=1200 b/s,72=110 b/s

TH1=0xe6;

TMOD=0x21; //auto-reload mode for serial comm

TR1=1;

delay(255);

SCON=0x58; // SCON reg for serial commn.

void ser_out(unsigned char ser_data)

SBUF=ser_data;

delay(255);

SCON=0x58;

delay(2000);

void ser_out_st(unsigned char *mess,unsigned char n)

{

unsigned char i;

for(i=0;i < n;i++)

ser_out(mess[i]);

```

```

}

void scan()

{

p0=0;

p3=1;

if(p6==0)

delay(20000); // delay fn. called

key1=1;

key2=key3=0;

p3=0;

p0=1;

if(p7==0)

delay(20000);

key3=1;

key1=key2=0;

}

else if(p4==0)

{

delay(20000);

key2=1;

key1=key3=0;

}

}

```

## 2.7.2.TRANSMITTER:

```

#include<reg51.h>

void transm(unsigned char);

sbit key1 = P3^4; //initializing pins of port3 to keys

sbit key2 = P3^5;

sbit key3 = P3^6;

sbit key4 = P3^7;

main()

{while(1)

{

if(key1==0) // key1 for train no.

{

again:

if(key3==0) //key3 for track no.

transm(0x03); // transm fn. called

transm(0x04);

transm(0x05);

transm(0x01);

goto end;

else if(key4==0) // key4 for track no.

transm(0x03); // transm fn. called

transm(0x04);

transm(0x05);

transm(0x02);

goto end;

```

```

else goto again;

else if(key2==0) // key2 for train no.

again1:

if(key3==0)

transm(0x06);

transm(0x07);

transm(0x08);

transm(0x01);

goto end;

else if(key4==0)

transm(0x06);

transm(0x07);

transm(0x08);

transm(0x02);

goto end;

else goto again1;

else if(key3==0)

transm(0x09);

end:;

```

```

void delay(unsigned int b) //delay fn.

do b=1;

while (b!=0);

void transm(unsigned char da)

{

P1=da;

delay(20000);

P1=0xff;

delay(20000);

}

2.7.3.RECEIVER:

#include<reg51.h>

void disp_all();

void htd(unsigned int);

void display();

void read(unsigned char);

void write(unsigned char);

void lcd_init(void);

void lcd_dis(unsigned char *,unsigned char);

void delay(unsigned int);

= P1^4; // ack bit assigned to port 1

sbit ack

= P2^0; // rs bit assigned to pin 0 of port2

sbit rs

= P2^1; //rw bit assigned to pin1 of port2

sbit rw

```

```

= P2^2; // en bit assigned to pin 2 of port2

sbit en

unsigned char thous, hund, ten, one, hund_r;

unsigned int thous_r;

unsigned char u,address=0x89,dat;

main()

lcd_init(); // LCD variables initialised

disp_all();

delay(65000); // delay fn. called

delay(65000);

read(0x01); // display at appropriate location

// display at first line

read(0x80);

",16);

lcd_dis("TRAIN NO:

//display at second line

read(0xc0);

lcd_dis("TRACK NO:

",16);

while(1)

{

if((ack==0)&&(u==0)) u=1;

if((ack==1)&&(u==1))

u=0;

{

dat=P1&0x0f;

if(dat!=0x0f && dat!=0x09)

read(address);

write(dat+0x30);

address++;

if(address==0x8c) address=0xc9;

if(address==0xca) address=0x89;

```

```

}

else if(dat==0x09)

{

read(0x01);

// display at first line

read(0x80);

",16);

lcd_dis("TRAIN NO:

// display at second line

read(0xc0);

",16);

lcd_dis("TRACK NO:

address=0x89;

}

} }

void delay(unsigned int b)// the only delay routine, which is user variable &

is decided by the values given in the brackets

\{ do b=1;

while (b!=0);

void lcd_init()

read(0x38);

read(0x01);

read(0x06);

read(0x0c);

}

void read(unsigned char add)

{

P0=add;

rs=rw=0; // low the rs and rw bits

```

```

en=1; // en bit high

// call delay

delay(125);

en=0; // low the en bit

delay(125);

}

void write(unsigned char dat)

{ P0=dat;

rs=en=1; // rs and en bit made high

rw=0; // rw bit made low

delay(125);

en=0; // en bit made low

delay(125); // call delay

}

void lcd_dis(unsigned char *mess,unsigned char n)

{ unsigned char i;

for(i=0;i \le n;i++) // n - no. of characters to be displayed

{

write(mess[i]); // i - character to be diaplayed

delay(125);

}}

void disp_all()

{

read(0x01);

read(0x80); // display at first line

lcd dis(" Railway gate ",16);

read(0xc0); //display at second line

lcd_dis(" Controller ",16)

}

```

## 2.7.4.FLOWCHART

Fig 2.14

## CHAPTER 3

## **CONCLUSION:**

In our project we implemented an automatic gate control system that includes appropriate warning signals at the gate, thus avoiding danger to life and property of the public by eliminating manual operation. In collision prevention system we took measures to prevent direct collision between the trains which is becoming a serious problem to the economy of the country.

## **FUTURE ENHANCEMENTS:**

- Provision of sensors at the gate to sense if anyone is crossing the gate at the time of its closing so that appropriate measures could be taken to prevent their damage.

- To avoid the human involvement in entering the data such as train no. and its track no. for transmission.

- Real time simulation can be done.

**APPENDICES**

## APPENDIX 1

| Serial | Components                | Price  |

|--------|---------------------------|--------|

| number | •                         | In Rs. |

| 1.     | IC ULN2003                | 40     |

| 2.     | IC 7805                   | 15     |

| 3.     | IC 7812                   | 15     |

| 4.     | IC 7912                   | 15     |

| 5.     | AT 89C51                  | 90     |

| 6.     | Crystal Oscillator-12 MHz | 18     |

| 7.     | 10μF Capacitor            | 2      |

| 8.     | 1000μF Capacitor          | 8      |

| 9.     | Key                       | 12     |

| 10.    | LCD Display               | 650    |

| 11.    | ON/OFF Relay              | 60     |

| 12.    | Resistor 3K               | 0.15   |

| 13.    | Servo motor               | 950    |

| 14.    | Gate Model                | 1600   |

| 15.    | Resistor 33k              | 0.50   |

| 16.    | Resistor 10k              | 0.25   |

| 17.    | RF Transmitter            | 250    |

| 18.    | RF Receiver               | 250    |

| 19.    | HT648L and HT640          | 400    |

| 20.    | Diodes                    | 0.50   |

| 21.    | Transformer               | 190    |

| 22.    | PCB per Square cm.        | 2      |

## Microcontroller Instruction Set

For interrupt response time information, refer to the hardware description chapter.

Instructions that Affect Flag Settings (1)

| Instruction |   | Flag |                                        | instruction | Flag |    |          |  |  |

|-------------|---|------|----------------------------------------|-------------|------|----|----------|--|--|

|             | C | ٥٧   | AC                                     |             | ¢    | ٥v | AC       |  |  |

| ADD         | × | х    | Х                                      | CLRIC       | U_   |    |          |  |  |

| ADDC        | × | х    | Х                                      | CPL C       | ×    |    |          |  |  |

| SUBB        | X | X.   | X                                      | ANL C.bit   | ×    |    |          |  |  |

| MUL         | 0 | X    |                                        | ANL C. bit  | ×    |    |          |  |  |

| DIV         | 0 | ×    |                                        | ORL C.5#    | ×    |    |          |  |  |

| DA          | × |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ORL Cabit   | ×    |    |          |  |  |

| RRC         | х |      |                                        | MOV C38I    | ×    |    |          |  |  |

| Rt C        | × |      | <u> </u>                               | C.INE       | х    |    |          |  |  |

| SETB C      | 1 |      |                                        |             |      |    | <u> </u> |  |  |

The Instruction Set and Addressing Modes

| R <sub>0</sub> | Register R7-R0 of the autrently selected Register Bank.                                                                                                                   |  |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| direct         | 8-bit internal data location's address. This could be an internal Data RAM facation (0-127) or a SFR (i.e., I/O port, control register, status register, etc. (128-255)). |  |  |  |  |  |  |

| ्रंR,          | 8-bit internal data RAM Socation (0-25%) addressed indirectly through register R1or R0.                                                                                   |  |  |  |  |  |  |

| #data          | 8-bit constant included in instruction.                                                                                                                                   |  |  |  |  |  |  |

| #data 16       | 16-bit constant included in instruction.                                                                                                                                  |  |  |  |  |  |  |

| addr 16        | 16-bit destination address. Used by LCALL and LJMP. A branch can be anywhere within the 64K byte Program Memory address space.                                            |  |  |  |  |  |  |

| addr 11        | 11-bit destination address. Used by ACALL and AIMP. The branch will be within the same 2K byte page of program memory as the first byte of the tollowing instruction.     |  |  |  |  |  |  |

| rol            | Signed (twos complement) 8-bit offset byte. Used by SJMP and all conditional jumps. Range s128 to +127 twies relative to first byte of the following instruction.         |  |  |  |  |  |  |

| bit            | Direct Addressed bit in Internal Data RAM or Special Function Register                                                                                                    |  |  |  |  |  |  |

Instruction Set

Instruction Set Summary

| T | 0                         | 1                           | 2                          | 3                           | 4                             | 5                             | 6                            | 7                            |

|---|---------------------------|-----------------------------|----------------------------|-----------------------------|-------------------------------|-------------------------------|------------------------------|------------------------------|

| 0 | NOP                       | JBC<br>bit,rel<br>[38, 20]  | JB<br>bit, rel<br>[3B, 2C] | JNB<br>bit. rel<br>[3B, 2C] | JC<br>rel<br>[2B, 2C]         | JNC<br>rel<br>[2B, 2C]        | JZ<br>rel<br>[28, 20]        | JNZ<br>rel<br>[2B, 2C]       |

| 1 | AJMP<br>(P0)<br>[28, 20]  | ACALL<br>(P0)<br>[28, 2C]   | AJMP<br>(P1)<br>[2B, 2C]   | ACALL<br>(P1)<br>[2B, 2C]   | AJMP<br>(P2)<br>[2B, 2C]      | ACALL<br>(P2)<br>[2B, 2C]     | AJMP<br>(P3)<br>[28, 20]     | ACALL<br>(P3)<br>[2B, 2C]    |

| 2 | ⊔MP<br>addr16<br>[3B, 2C] | LCALL<br>addr16<br>[38, 2C] | RET<br>[2C]                | RETI<br>[20]                | ORL<br>dir. A<br>[28]         | ANL<br>dir, A<br>[28]         | XRL<br>dir, a<br>[28]        | ORL<br>C, bit<br>[28, 20]    |

| 3 | RR<br>A                   | RRC<br>A                    | RL<br>A                    | RLC<br>A                    | ORL<br>dir. #dats<br>[38, 20] | ANL<br>dir. #data<br>[38, 20] | XRL<br>dir.#data<br>[3B, 2C] | JMP<br>@A + DPT!<br>[2C]     |

| 4 | INC<br>A                  | DEC<br>A                    | ADD<br>A. #data<br>[28]    | ADDC<br>A, #data<br>[28]    | ORL<br>A. #data<br>[28]       | ANL<br>A, #data<br>[2B]       | XRL<br>A, #data<br>[2B]      | MOV<br>A, #data<br>[2B]      |

| 5 | INC<br>dir<br>[2B]        | DEC<br>dir<br>[2B]          | ADD<br>A, dir<br>[2B]      | ADDC<br>A, dir<br>[28]      | ORL<br>A, dir<br>[28]         | ANL<br>A, dir<br>[2B]         | XRL<br>A, dir<br>[26]        | MCV<br>dir.#data<br>[3B. 2C] |

| 6 | INC<br>@R0                | DEC<br>@RO                  | ADD<br>A. @R0              | ADDC<br>A, @R0              | ORL<br>A. @R0                 | ANL<br>A, @R0                 | XRL<br>A. @R0                | MOV<br>@R0, @ds<br>[2B]      |

| 7 | INC<br>@R1                | DEC<br>@R1                  | ADD<br>A. @R1              | ADDC<br>A. @R1              | ORL<br>A. @R1                 | ANL<br>A. @R1                 | XRL<br>A. @R1                | MOV<br>@R1_#da<br>[2B]       |

| 8 | INC<br>R0                 | DEC<br>RO                   | ADD<br>A, R0               | ADDC<br>A, R0               | ORL<br>A, R0                  | ANL<br>A, Rű                  | XRL<br>A, R0                 | MOV<br>R0, #dat<br>[28]      |

| 9 | INC<br>R1                 | DEC<br>R1                   | ADD<br>A. R1               | ABBC<br>A, R1               | ORL<br>A, R1                  | ANL<br>A, R1                  | XRL<br>A, R1                 | MOV<br>R1, ≇dat<br>[2B]      |

| A | INC<br>R2                 | DEC<br>R2                   | ADD<br>A, R2               | ADDC<br>A, R2               | ORL<br>A. R2                  | ANL<br>A. R2                  | XRL<br>A, R2                 | MCV<br>R2,#dal<br>[2B]       |

| В | INC<br>R3                 | DEC<br>R3                   | ADD<br>A. R3               | ADDC<br>A, R3               | ORL<br>A, R3                  | ANL<br>A, R3                  | XRL<br>A, R3                 | MOV<br>R3, #da<br>[2B]       |

| С | INC<br>R4                 | DEC<br>R4                   | ADD<br>A, R4               | ADDC<br>A, R4               | ORL<br>A, R4                  | ANL<br>A, R4                  | XRL<br>A. R4                 | MOV<br>R4 , #da<br>[2B]      |

| D | INC<br>R5                 | DEC<br>R5                   | ADD<br>A. R5               | ADDC<br>A, R5               | ORL<br>A, R5                  | ANL<br>A, R5                  | XRL<br>A. R5                 | MOV<br>R5.#ds<br>[2B]        |

| E | INC<br>R6                 | DEC<br>R6                   | ADD<br>A, R6               | ADDC<br>A, R6               | ORL<br>A, R6                  | ANL<br>A, R6                  | XRL<br>A, R6                 | MOV<br>R6, #ds<br>[2B]       |

| F | INC<br>R7                 | DEC<br>R7                   | ADD<br>A. R7               | ADDC<br>A, R7               | ORL<br>A, R7                  | ANL<br>A, R7                  | XRL<br>A, R7                 | MOV<br>R7 . #ds<br>[28]      |

Note: Key: [2B] = 2 Byte, [3B] = 3 Byte, [2C] = 2 Cycle, [4C] = 4 Cycle, Blank = 1 byte/1 cycle

# Instruction Set

| ructio | n Set Sum                   | mary (Con                     | (IIIdea)                   |                                    | С                        |                            | E                | F                        |

|--------|-----------------------------|-------------------------------|----------------------------|------------------------------------|--------------------------|----------------------------|------------------|--------------------------|

|        | 8<br>SJMP                   | 9<br>MOV                      | ORL                        | ANL                                | PUSH<br>dir              | POP<br>dir                 | MOVX A.<br>@DPTR | MOVX<br>@DPTR. A<br>[2C] |

| ° \    | REL<br>[28, 20]             | DPTR.#<br>data 16<br>[38, 20] | C. /bit<br>[2B, 2C]        | ©, /bit<br>[28, 20]                | [28, 20]                 | [2B, 2C]                   | [2C]             | ACALL                    |

|        | AJMP<br>(P4)                | ACALL<br>(P4)                 | AJMP<br>(P5)               | ACALL<br>(P5)<br>[28, 2C]          | AJMP<br>(P6)<br>[2B. 2C] | (P6)<br>[2B, 2C]           | (P7)<br>[2B, 2C] | (P7)<br>[2B, 2C]         |

|        | [2B, 2C]                    | [28, 2C]<br>MOV               | [2B, 2C]<br>MOV            | CPL                                | CLR<br>bit               | SETB<br>bit                | MOVX<br>A. @R0   | MOVX<br>wR0, A<br>[20]   |

| 2      | ANL<br>C. bit<br>[28, 20]   | ыі, С<br>[2В. 2С]             | C. bit<br>[26]             | bit<br>(2B)                        | [2B]<br>CLR              | [28]<br>SETB               | [2C]<br>MCVX     | MOVX<br>@RLA             |

| 3      | MOVC A.<br>@A + PC          | MOVC A.<br>@A + DPTR          | INC<br>DPTR<br>[2C]        | CPL<br>C                           | G                        | С                          | A. @RI<br>[2C]   | [20]<br>CPL              |

| 4      | [2C]                        | (2C)<br>SUBB                  | MUL<br>AB                  | CJNE A.<br>#data, rel              | SWAP<br>A                | DA<br>A                    | CLR<br>A         | A                        |

|        | AB<br>[28, 40]              | A, #data<br>[28]              | [4C]                       | [3B, 2C]<br>CJNE                   | XCH                      | DJNZ<br>dir, rel           | MOV<br>Audir     | MOV<br>dir. A            |

| 5      | MOV<br>dir, dir             | SUBB<br>A, dir<br>[2B]        |                            | A, dir. rel<br>[38, 20]            | A. dir<br>[28]           | [3B, 2C]                   | [2B]<br>MOV      | [28]<br>MOV              |

|        | [3B, 2C]<br>MOV             | SUBB<br>A, @R0                | MOV<br>@R0_dir             | CJNE<br>@R0,#data.rel              | XCH<br>A. @Rú            | XCHD<br>A. @R0             | A. @R0           | @R0, A                   |

|        | dir. @R0<br>[28, 20]        | SUBB                          | [2B, 2C]<br>MOV            | [3B, 2C]<br>CJNE                   | XCH<br>A, @R1            | XCHD<br>A. @R1             | MOV<br>A. @R1    | MOV<br>@R1. A            |

| 7      | MOV<br>dir. @R1<br>[2B, 2C] | A @R1                         | @R1, dir<br>[28, 20]       | @R1,#data, rel<br>[3B, 2C]         | XCH                      | DJNZ                       | MOV              | MOV                      |

| 8      | MOV<br>dir, R0              | SUBB<br>A. RO                 | MÖV<br>R0. dir             | CJNE<br>R0, #data, rel<br>(38, 20) | A. RO                    | R0, rel<br>[2B, 2C]        | A, R0            | R0, A                    |

|        | [28, 20]<br>MOV             | SUBB                          | [28, 20]<br>MOV            | CJNE<br>R1, #data, rel             | XCH<br>A, R1             | DJNZ<br>R1, rel            | MOV<br>A, R1     | MOV<br>R1. A             |

|        | dir, R1<br>[28, 20]         | A, R1                         | R1, dir<br>[2B, 2C]        | [38, 20]<br>CJNE                   | хсн                      | [2B, 2C]                   | MOV<br>A, R2     | MOV<br>R2, A             |

| A      | MOV<br>dir. R2              | SUBB<br>A, R2                 | MOV<br>R2. dir<br>[28, 20] | R2, #data, rel<br>[3B, 2C]         | A. R2                    | R2, rel<br>[2B, 2C]        |                  | MOV                      |

| В      | [28, 20]<br>MOV             | SUBB                          | MOV<br>R3, dir             | CJNE<br>R3, #data, rel             | XCH<br>A. R3             | DJNZ<br>R3, rei<br>[28, 20 | MOV<br>A, R3     | R3. A                    |

|        | dir. R3<br>[28, 20          | 1                             | [28, 20]                   | [3B, 2C]<br>CJNE                   | хсн                      | DJNZ<br>R4, rel            | MOV              | MOV<br>R4. A             |

|        | MCV<br>dir. R4<br>[28, 20   |                               | R4, dir<br>[28, 20]        | R4,#data. re<br>[38, 20]           |                          | [2B, 20                    | 1                | MOV                      |

|        | <del></del>                 | SUBE                          | R5. dir                    | CJNE<br>R5, #data, re<br>[38, 20]  | XCH<br>A. R5             | ·                          | A.R.             | R5. A                    |

|        | [2B, 2                      | CI                            | [2B, 2C]<br>3 MOV          | CJNE<br>Do Edglo F                 | XCH<br>al A. Re          | 5   R6. r                  | <sub>el</sub>    |                          |

|        | E MOV<br>dir, F<br>[28, 2   | 6 A.R                         |                            | 1 (20, 20)                         | XCH                      | [2B, 2                     | z MO             | 0.7                      |

|        | ' die F                     | F MCV SUBB<br>dir, R7 A, R7   |                            | R7.#data, [38, 20]                 | rel A.R                  | 7 R7. r<br>[2B. 2          | . 1              | 100                      |

Note: Key: [2B] = 2 Byte, [3B] = 3 Byte, [2C] = 2 Cycle, [4C] = 4 Cycle, Blank = 1 byte/1 cycle

| inemor      | ic           |                        | Des                         | cription                                                                                                                          | Byt             | e C | )scillat<br>Period |    |

|-------------|--------------|------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|--------------------|----|

| <del></del> |              |                        | 1                           | colute Subroutine Call                                                                                                            | 2               |     | 24                 |    |

| ACALL       |              |                        | 1                           | ng Subroutine Call                                                                                                                | 3               |     | 24                 |    |

| LCALL       | ad           | gr16                   |                             | turn from Subroutine                                                                                                              | 1               | 1   | 24                 |    |

| RET<br>RETI | -            |                        | Re                          | turn from                                                                                                                         | 1               |     | 24                 | 24 |

|             | -            |                        |                             | en up.                                                                                                                            |                 | 2   | 24                 |    |

| AJMP        | +            |                        | +-                          | ong Jump                                                                                                                          | Ţ               | 3   | 24                 |    |

| SJMP        | JMP   addr16 |                        | s                           | hort Jump (relative<br>Edr)                                                                                                       |                 | 2   | 24                 |    |

| JMP         | 1            | A+DPTR                 | ٦,                          | ump indirect relative to<br>ne DPTR                                                                                               |                 | 1   | 2                  | 4  |

| JZ          | +            | rel                    | Jump if Accumulator is Zero |                                                                                                                                   |                 | 2   | 2                  | 4  |

| JNZ         | +            |                        | -                           | Jump if Accumulator is Not Zero  Compare direct byte to Acc and Jump if Not Equal  Compare immediate to Acc and Jump if Not Equal |                 | 2   | 2                  | 24 |

| CJN         | Ē            | A, direct, rel         | -+                          |                                                                                                                                   |                 | 3   |                    | 24 |

| CUN         | E            | A,#data,ral            |                             |                                                                                                                                   |                 | 3   |                    | 24 |

| cui         | NE.          | R <sub>m</sub> #data.r | el                          |                                                                                                                                   |                 | 3   |                    | 24 |

| a           | NE.          | @R <sub>u</sub> #data  | a, rel                      | Compare immediate indirect and Jump if Equal                                                                                      | to<br>Not       | 3   |                    | 24 |

| ۵           | JNZ.         | R <sub>n</sub> , rel   |                             | Decrement register<br>Jump if Not Zero                                                                                            | and             | _   | 2                  | 24 |

| D           | JNZ          | direct,rel             |                             | Decrement direct by<br>and Jump if Not Zer                                                                                        | /te<br>ro<br>—— | -   | 3                  | 24 |

| <u> </u>    | OP           |                        |                             | No Operation                                                                                                                      |                 |     | <u> </u>           | 12 |

Table 1. AT89 Instruction Set Summary $^{(1)}$

| in em or | nic      |                  | De                                    | scription                                               | Ву        | te |         | illator<br>eriod |    |

|----------|----------|------------------|---------------------------------------|---------------------------------------------------------|-----------|----|---------|------------------|----|

| ARITHM   | IET      | IC OPERAT        | ION                                   | S                                                       |           |    |         |                  |    |

| ADD      | A,i      |                  | Ad                                    | dd register to<br>comulator                             | 1         |    |         | 12               |    |

| ADD      | A.       | direct           | firect Add direct byte to Accumulator |                                                         |           | 2  |         | 12               |    |

| ADD      | Å.       | @R;              |                                       | dd indirect RAM to<br>ccumulator                        |           | 1  | L       | 12               |    |

| ADD      | A.       | #data            |                                       | dd immediale data to<br>œumulator                       | <br> <br> | 2  |         | 12               |    |

| ADDC     | A        | .R <sub>n</sub>  | A                                     | dd register to<br>locumulator with Carry                |           | 1  |         | 12<br>           |    |

| ADDC     | A        | , direct         | A                                     | kdd direct byte to<br>kocumulator with Carry            |           | 2  | _       | 12               |    |

| ADDC     | A        | 4.@R; A          |                                       | Add indirect RAM to<br>Accumulator with Carry           |           | 1  |         | 12               |    |

| ADDC     | 1        |                  |                                       | A,#data Add immediate data to Acc with Carry            |           |    | 2       |                  | 12 |

| SUBB     | +        | s.R <sub>n</sub> |                                       | A.R <sub>n</sub> Subtract Register from Acc with borrow |           |    | 1       |                  | 12 |

| SUBE     | +        | A, direct        | _                                     | Subtract direct byte from<br>Acc with borrow            | ,         | 2  |         | 12               |    |

| SUBE     | 3        | A,@Ri            | 1                                     | Subtract indirect RAM from ACC with borrow              |           | 1  |         | 12               |    |

| SUBE     | В        | A,#data          |                                       | Subtract immediate data<br>from Acc with borrow         | 3         | 2  |         | 12               |    |