### CRT CONTROLLED CHARACTER DISPLAY

PROJECT REPORT

SUBMITTED BY

**AJOMON JOSEPH**

**BINU ZACHARIAH**

UNDER THE GUIDANCE OF

PROF. K. PALANISWAMI, M.E., MIEE, MIE. MISTE, MCSI, FIETE.

IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF BACHELOR OF ENGINEERING IN ELECTRONICS & COMMUNICATION ENGINEERING OF THE BHARATHIAR UNIVERSITY

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

# KUMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE - 641 006

1991 - 1992

## **CERTIFICATE**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## KUMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE - 641 006

| PR       | O.   | TOT   | WORK |

|----------|------|-------|------|

| $\Gamma$ | ∖Jt. | ハンしょし | WUNK |

| Register Number                                                    |  |  |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|--|--|

| This is to certify that the Project entitled                       |  |  |  |  |  |  |

| CRT CONTROLLED CHARACTER DISPLAY                                   |  |  |  |  |  |  |

| has been submitted by                                              |  |  |  |  |  |  |

| Mr/Ms AJOMON JOSEPH, BING ZACHARIGH, MANOS PACES                   |  |  |  |  |  |  |

| In partial fulfilment of the requirements for the award of the     |  |  |  |  |  |  |

| degree of Bachelor of Engineering in Electronics And Communication |  |  |  |  |  |  |

| Engineering of the Bharathiar University - 641 046                 |  |  |  |  |  |  |

| During the Academic Year 1991 - 92                                 |  |  |  |  |  |  |

| Guide Head of the Department                                       |  |  |  |  |  |  |

| Submitted for the Viva-Voce examination held on                    |  |  |  |  |  |  |

| Internal Examiner External Examiner                                |  |  |  |  |  |  |

DEDICATED TO MY

BELOVED PARENTS

**ACKNOWLEDGEMENT**

### ACKNOWLEDGEMENT

Our sincere thanks to our Principal Prof.T.S.RAMAMURTHI, B.E., MISTE and to the Department of Electronics and Communication Engineering for the ample facilities provided to us for carrying out our project.

We are indebted to the Head of the Department of Electronics and Communication Engineering and our guide Prof.K.PALANISWAMI, M.E., MIEEE, MIE, MISTE, MCSI, FIETE who has been an inspriation to us through out our project work.

Our sincere thanks goes to Mr.JACOB MATHEWS, B.E., for the idea and encouragement given to us and we are also greatful to Mr.PALANIVEL, B.E., for his timely help during the course of this project.

Our special thanks to all teaching and non-teaching staff those who helped us in making this project a success.

#### SYNOPSIS

The unit proposed here is a micro processor based CRT display terminal capable of supplying RS 232 or inverted TTL ASCII data. Designing such a terminal is possible with SSI chips but require a large number of IC's and system becomes bulky and difficult to trouble shoot. This can be over come by Micro Processor based terminal.

In this, data to be displayed are to be stored in the EPROM chip. With the help of Buffer and ROM, Micro Processor will process the data and send it to the CRT controller which is used in interface the system to the monitor. The width of dot and character are determined by the dot clock frequency. The 8 bit data from the character generator in the parallel form is convered to serial form by parallel input serial output shift register. The shift register is clocked at the dot clock rate and its output constitute the video input to the CRT.

The unit can be used as a teaching aid. It may be of interest to the deaf and hard of hearing. It is used in advertising purpose.

It is more flexible for future expansion and modification. It can be easily interfaced with any host computer. It can display the characters in TV screen with slight modification at the output.

CONTENTS

### CONTENT

|            |        |                                        | PAGE NO.     |

|------------|--------|----------------------------------------|--------------|

|            |        | RODUCTION                              | <b>\$</b> .  |

| Chapter ]  | II SYS | TEM DESCRIPTION                        | 3            |

|            | 2.1    | CRT BASICS                             |              |

|            | 2.2    | 8275 DESCRIPTION                       |              |

|            |        | 2.2.1 CRT DISPLAY REFRESHING           |              |

|            |        | 2.2.2 CRT TIMING                       |              |

|            |        | 2.2.3 USING THE 8275 WITHOUT DMA       |              |

|            |        | 2.2.4 8275-PROGRAMMABLE CRT CONTROLLER |              |

|            | 2.3    | PROM (82S123) DECODING                 |              |

|            | 2.4    | CHARACTER GENERATOR                    |              |

|            | 2.5    | DESCRIPTION OF 8085                    |              |

|            | 2.6    | DISPLAY RAM (6116)                     |              |

|            | 2.7    | ADDRESS BUFFER (8212)                  |              |

|            | 2.8    | SHIFT REGISTER                         |              |

|            | 2.9    | COUNTER (74163)                        |              |

|            | 2.10   | HARD WARE DESCRIPTION                  |              |

| Chapter II | I SYS  | TEM OPERATION                          | 3 <b>4</b> - |

|            | 3.1    | SYSTEM FUNCTIONING                     | 01           |

|            | 3.2    | SYSTEM TIMING                          |              |

| Chapter IV | DESIG  | GN OF DOT CLOCK                        | 36           |

| Chapter V  | SYSTE  | EM SOFTWARE                            | <b>Q</b>     |

| Chapter VI | CONC   | LUSION                                 |              |

|            | 6.1    | COMPOSITE VIDEO                        |              |

|            | 6.2    | KEYBOARD INTERFACE                     |              |

|            | BIBLI  | OGRAPHY                                |              |

|            | APPE   | NDIX                                   |              |

INTRODUCTION

#### CHAPTER-I

#### INTRODUCTION

Display of information will be required in a variety of applications involving calculating machines, computer systems, data retrieval systems, data communications systems and many other areas.

## There are many types of display systems :

(i) CRT Displays (ii) LED Displays (iii) LCD Displays and so on. A CRT alphanumeric display is a recent development in display technique. Light emitting didode (LED) and Liquid Crystal Diode (LCD) displays are not used much commonly because the cost of LED is highand in the case of LCD, we need an external light and the ambient temperature of operation is limited. So CRT display is chosen almost always for large area displays owing to its merits of brightness, uniformity, low cost and high reliability.

Sometimes, in off-the-air television pictures, we see rows of alphanumeric message on tables-usually before news on forecast programmes. These message lines are obtained with a video chamera which is aimed upon messages that are written on paper on placards. But, when a microcomputer uses a TV as a peripheral display to write messages on the screen, the method of generating the video is entirely different (because no camera is

involved here), though the final video signal from the camera and that obtaine din the micro computer would be similar. The message words in the latter case are stored codes in digital memory chips corresponding to the alphanumeric characters it displays on the screen. Thus, the requirement is that of placing the 'digital words' in the form of several rows on the screen each row containing several characters.

In this project, we have developed a microprocessor based CRT display terminal. Normally designing a terminal with Integrated Circuits (MSI) will require large number of IC's and the system becomes complex and difficult to troubleshoot. But this can be overcome by a microprocessor based Terminal. Moreover, this type of system is more flexible for future expansion and modification. Also the system becomes more versatile and it can be easily interfaced with any host computer.

In our present work, the complete details for making an Add-on board which is interfaced to the microprocessor kit are given describing the elements of techniques, circuitry and application details so as to get a 20-line display of alphanumeric informatin on a T.V monitor on a solid state TV set with a modulator.

SYSTEM DESCRIPTION

### CHAPTER - II

### SYSTEM DESCRIPTION

### 2.1 CRT Basics

The image displayed on the CRT is built up by generating a series of lines across the face of the CRT. Usually the beam starts in the upper left hand corner of the display and simultaneously moves from left to right and from top to bottom to put a series of Zig Zag lines on the screen.

The simultaneously operating independent circuits control the vertical and horizontal movement of the beam. When the beam reaches the end of the line it is brought back to the beginning of the next line which is done much faster during which the electron beam is usually shut off. This action is referred to as "retrace".

When the beam finally reaches the bottom right hand of the screen it retraces vertically back to the top left hand corner. The time it takes for the beam to move from the top of the screen to the bottom and back again to the top is referred to as a "Frame".

The CRT itself can track a horizontal frequency between 15250 Hz and 16250 Hz or in other words, there can be 256  $\,$

to 270 horizontal lines per vertical frame. The vertical frequency should be 50 Hz to ensure stability.

#### Scanning

In an interlaced system the line sets are not generated simultaneously. In a 50 Hz system first all the odd numbered lines are scanned (i.e) 1,3 ...625 then all the even numbered lines are scabbed (i.e) 0,2,4...624. Each set of lines usually contain different data. Interlacing provides data resolution. It also has some distinct disadvantages.

First of all, the circuitry needed to generate the extra half horizontal line per frame is quite complex when compared to a non interlaced design. Next the overall vertical refresh is half as that of a non interlaced display. As a result flicker may result when the CRT uses high speed Phosphors. The characters that are viewed on the screen are found by a series of dots that are shifted out of the controller where the electron beam moves across the face of the CRT. The circuit that creates this timing are referred to as the dot clock and character clock.

The character clock is equal to the dot clock divided by the number of dots used to form a character along the horizontal axis.

### 2.2 8275 Description

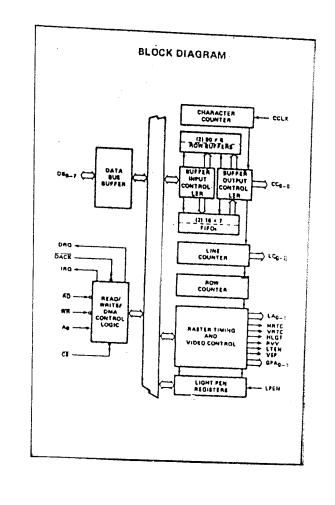

# 2.2.1 CRT Display Refreshing

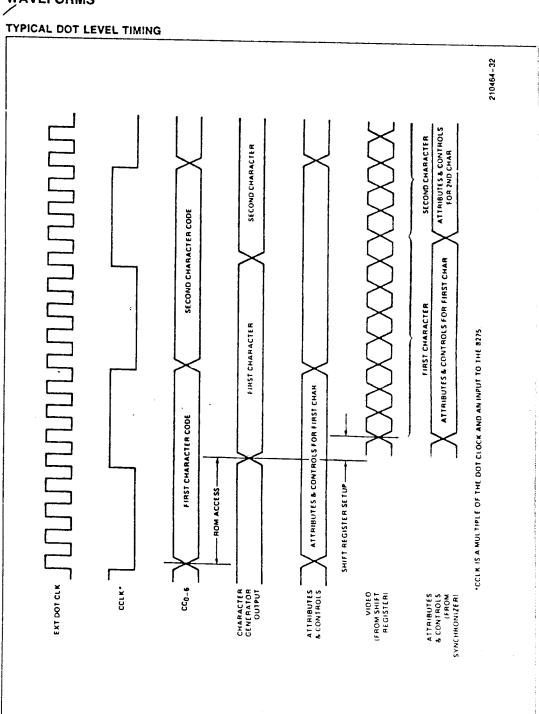

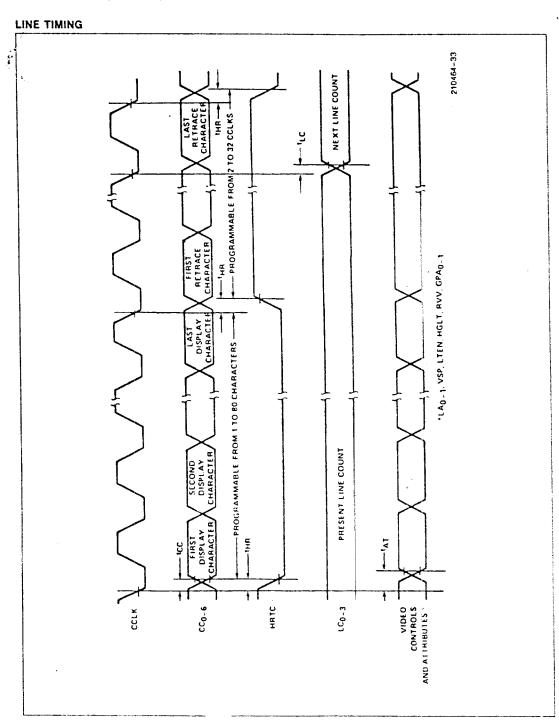

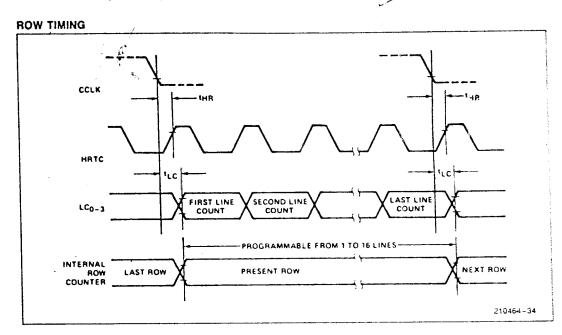

The 8275 having been programmed for a specific screen format generates a series of DMA request signals, resulting in the transfer of a row of characters from display memory to the 8275 row buffers. The 8275 presents the character codes to an external character generator ROM by using outputs CCO-CC6. External dot timing logic is then used to transfer the parallel output data from the character generator ROM serially to the video input of the CRT. The character rows are displayed on the CRT one line at a time. Line count outputs LCO-LC3 are applied to the character generator ROM to perform the line selection function.

Proper CRT refreshing requires that certain 8275 parameters be programmed prior to the beginning of the display operation. The 8275 has two types of programming registers. The command registers (CREG) and the parameter registers (PREG). It also has a status register (SREG). The command registers may only be written into and the status registers only be read. The 8275 expects to receive a command followed by a sequence of 0 to 4 parameters depending on the command.

To establish the format of display the 8275 provides a number of user programmable display format parameters. Display formats having 1 to 80 characters per row, 1 to 64 rows per screen and 1 to 16 horizontal lines per row are available.

In addition to transferring from memory to the CRT screen the 8275 features cursor position control. The cursor position may be programmed via x and y cursor position registers to any character position on the display. The user may select from 4 cursor formats. Blinking and non blinking, underline and reverse video block cursors are available

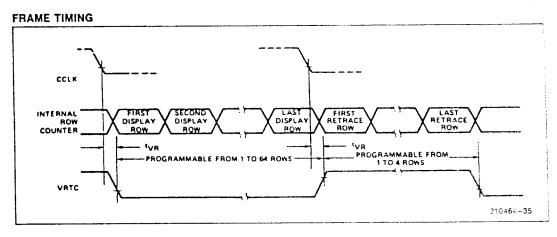

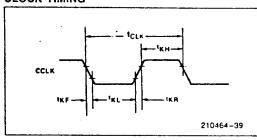

### 2.2.2. CRT Timing

The 8275 provides two timing outputs, HRTC and VRTC which are utilised in synchronising CRT horizontal and vertical oscillators to the 8275 refresher cycle. In addition whenever HRTC or VRTC is active, a third timing output, VSP (vieo supress) is there providing a blinking signal to the dot timing logic. The dot timing logic will normally inhibit a video output to the CRT during the time when VSP signal is true. An additional timing output LTEN is used to provide the ability to produce the video output high regardless of the state of VSP. This feature is used by the 8275 to place a cursor on the screen and control up to date functions.

## 2.2.3 Using the 8275 without DMA

The only real concern with using the 8275 in an interrupt-driven transfer mode is speed. Eighty characters must be loaded into the 8275 every 617 microseconds and the processor must also have time to perform all the other tasks that are required. To minimise overhead associated with loading the characters into the

8275, a special technique was employed. This technique involves setting a special transfer bit and executing a string of POP instructions. The string of POP instructions is used to rapidly move the data from memory into the 8275.

In this design the 8085's SOD line was used as the special transfer bit. In order to perform the transfer properly this special bit must do 2 things - 1) turn processor reads into DACK plus WR for the 8275; and 2) mask processor fetch cycles from the 8275, so that a fetch cycle does not write into the 8275, so that a fetch cycle does not write into the 8275, so that a fetch cycle does not write into the 8275. Conventional logic could have been used to implement this special function, but in this design a small bipolar programmable read only memory was used.

At first, it may seem strange that we are supplying a DACK when no DMA controller exists in the system. But as we know that all intel peripheral devices that have DMA lines actually use DACK as a chip select for the data, so when you want to write a command or read status, we assert CS and WR or RD, but when we want to read or write data we assert DACK and RD or WR. The peripheral divice does not know if a DMA controller is in the circuit or not. DACK and CS should not be asserted on the same time, since this combination yields an undefined result.

The POP technique actually compares quite favourably in terms of time to the DMA technique. One POP instruction transfers two bytes of data to the 8275 and takes 10 CPU clock

cycles to execute at a net transfer rate of 1 byte every five clock cycles. The DMA controller takes 4 clock cycles to transfer 1 bit but sometime is lost in synchronisation so the difference between two techniques is 1 clock cycle per byte maximum.

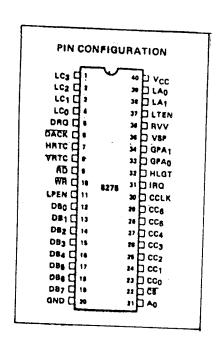

### 2.2.4 8275 - Programmable CRT Controller

### Functional Description :

#### Data Bus Buffer :

This is a 3 state bidirectional 8 bit bufer which is used to interface 8275 to the system data bus. This functional block accepts inputs from the system control bus and generates control signals for overall device operation. it contains the command parameter and status register that stores various control formats for the device functional definition.

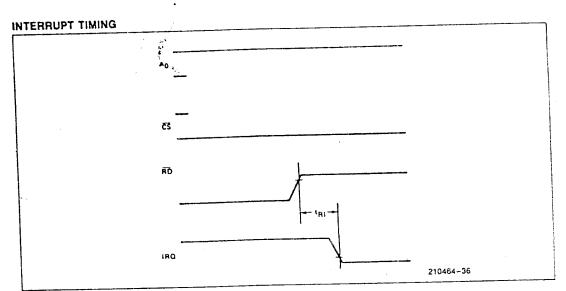

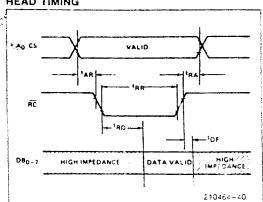

#### RD (READ)

A 'low' on this input informs the 8275 that the CPU is reading data or status information from the 8275.

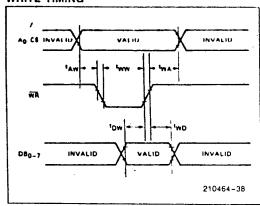

#### WR (WRITE)

A 'low' on this input informs the 8275 that the CPU is writing data or control words to the 8275.

### CS (CHIP SELECT)

A 'low' on this input selects the 8275. No reading or writing will occur unless the device is selected. When the CS is

high, the data  $\mbox{\it Bus}$  is in the float state and  $\mbox{\it RD}$  and  $\mbox{\it WR}$  will have no effect on the chip.

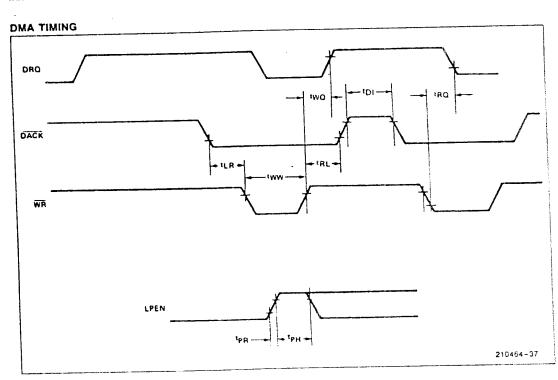

### DRQ (DMA REQUEST)

A 'high' on this output informs the DMA controller that the 8275 desires a DMA transfer.

## DACK (DMA ACKNOWLEDGE)

A 'low' on this input informs the 8275 that a DMA cycle is in progress.

## IRQ (INTERRUPT REQUEST)

A 'high' on this output informs the CPU that the 8275 desires interrupt service.

### CHARACTER COUNTER

A character Counter is programmable counter that is used to determine the number of characters to be displayed per row and the length of the horizontal retrace inteval. It is driven by the CCLK (Character Clock) input which should be a derivative of the external dot clock.

#### FIFO'S

These are two 16 character FIFO'S in the 8275. They are used to provide extra row buffer length in the transparent attribute modes.

### BUFFER INPUTVOUTPUT CONTROLLERS

The Buffer input/output controllers decode the characters being placed in the row buffers. if the character is a character attribute, field attribute or special code, these controllers control the appropriate action.

### SYSTEM OPERATION

The 8275 is programmable to a large number of different display formats. It provides raster timing, display row buffering, visual attribute decoding, cursor timing and light pen detection.

It is designed to interface with the 8257 DMA controller and standard character generator ROM's for dot matrix decoding. Dot level timing must be provided by external circuitry.

## GENERAL SYSTEM'S OPERATIONAL DESCRIPTION

The 8275 provides a "window" into the micro computer system memory.

Display characters are retrieved from memory and displayed on a row by row basis. The 8275 has two row buffers. While one row buffer is being used for display, the other is being filed with the next row of characters to be displayed. The number of display characters per row and the number of character rows per frame are software programmable providing easy interface to most CRT displays.

The 8275 requests DMA to fill the row buffer that is not being used for display. DMA Burst length and spacing are programmable.

The 8275 displays character rows one line at a time.

The 8275 also controls raster timing. This is done by generating horizontal retrace (HRTC) and vertical retrace (VRTC) signals The timing of these signals are programmable.

The 8275 can generte a cursor. Cursor locations and formats are programmable.

The 8275 has a light pen input and registers. The light pen input is used to load the registers. Light pen registers can be read as command.

## DISPLAY FORMAT

### SCREEN FORMAT

The 8275 can be programmed to generate from 1 to 80 characters per row and from 1 to 64 rows per frame. The 8275 can also be programmed to blank alternate rows. In this mode the first row is displayed, the seound blanked the third displayed etc.

#### ROW FORMAT

The 8275 is designed to hold the line count stable while outputting the appropriate character codes during each horizontal sweep. The line count is incremented during horizontal retrace and the whole row of character codes are output again during the next sweep. This is continued until the whole character row is designed.

### DOT FORMAT

Dot width and character width are dependant upon the external timing and control circuitary.

Dot level timing circuitary should be designed to accept the parallel output of the character generators and shift it out serially at the rate required by the CRT display.

Dot width is a function of dot clock frequency.

Character width is a function of character generator width.

Horizontal charcter spacing is a function of shift register length.

#### RASTER TIMING

The character counter is driven by the character clock input. It counts out the characters being displayed. It then causes the line counter to increment and it starts counting the horizontal retrace interval. This is constantly repeated.

The line counter is driven by the character counter. It is used to generate the line address outputs (LCO-3) for the character generator. After it counts all the lines in the character row, it increments the row counter and starts over again.

The row counter is an internal counter driven by the line counter. It controls the function of the row buffers and counts the number of character rows displayed.

After the row counter counts all the rows in a frame, it starts counting out the vertical retrace interval. The video suppression output (VSP) is active during horizontal and vertical retrace intervals. Dot level timing circuitry must synchronise these outputs with the video signal to the CRT display.

# VISUAL ATTRIBUTES AND SPECIAL CODES

The characters processed by 8275 are 8 bit quantities. There are 2 types of visual attribute codes. They are character attributes and field attributes.

## CHARACTER ATTRIBUTE CODES

Character attribute codes are codes that can be used to generate graphic symbols without the use of a character generator. This is accomplished by selectively the line attribute outputs (LAO-1), the video suppression output (VSP) and light

enable output. The dot level timing circuitry can be use these signals to generate the proper symbols.

Chracter attributes can be programmed to blink or be highlighted individually. Blinking is accomplished with the video suppression output (VSP). Blink frequency is equal to the screen refresh frequency divided by 32. Highlighting is accomplished by activating the highlight output (HGL T).

### FIELD ATTRIBUTES

The field attributes are control codes which affect the visual characteristics for a field of characters. There are six field attributes.

### 1) BLINK:

Characters following the code, blink by activating the VSP. The blink frequency is equal to the screen refresh frequency divided by 32.

### 2) HIGHLIGHT:

Characters following the code are highlighted by activating the highlight output (HGL  $extsf{T}$ ).

### 3) REVERSE VIDEO:

Characters following the code appear with reverse video by activating the reverse video output.

### 4) UNDERLINE:

Characters following the code are underlined by activating the LTEN output.

## 5),6) GENERAL PURPOSE:

There are two additional 8275 outputs which act as general independently programmable field attributes. GPAO-1 are active high outputs.

# FIELD FIND CHARACTER ATTRIBUTE INTERACTION

Character attribute symbols are affected by reverse video and general purpose field attribute. They are not affected by unerline, blink or highlingt.

### CURSOR TIMING:

The cursor location is determined by a cursor row register and a character position register which are located by commands to the controller. The cursor can be programmed to appear on the display as:

- 1) a blinking underline

- 2) a blinking reverse video block

- 3) a non blinking underline

- 4) a non blinking reverse video block

The cursor blinking frequency is equal to the screen refresh frequency divided by 16.

### 2.3. Prom (82S123) Decoding

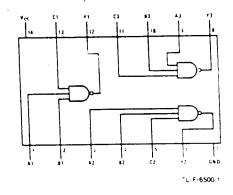

The logic necessary to convert the 8275 into a non-DMA type of device was performed by a single small bipolar PROM. Besides turning certain processor READS into DACKS and WRITES forthe 8275. this 32 by 8 PROM decodes addresses for the system RAM, ROM as well as for the 8255 parallel 1/0 port.

Any bipolar PROM that has a by eight configuration could function in this application. This particular device was chosen simply because it is the only "by eight" PROM available in a 16 pin package. The connection of the PROM is shown in detail in the figure and its truth table is also shown. Note that when a fetch cycle (M1) is not being performed, the state of the SOD line is the only thing that determines if memory needs will be written into the 8275's row buffer. This is done by pulling both DACK and WRITE low on the 8275.

### Futures

Address accers time

Power dessipation

Fully TTL compatible.

### = 35 sec max.

= 1.3 mW/bit.

### <u>Applications</u>

- 1. Sequential controller.

- 2. Random logic.

# TRUTH TABLE FOR 82S123

| A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |       |   |   |   |    |                |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|---|---|---|----|----------------|-------------|

| A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0  0 0 0 0 1 1 1 1 1 1 1 1 1 1 0  0 0 0 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                | 0     |   | ļ | 0 |    | IV             |             |

| A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0  0 0 0 1 1 1 1 1 1 1 1 1 0 0  0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                          |       |   |   | 0 |    | A12            | <del></del> |

| A1 A0 D7 D6 D5 D4 D3 D2 D1 D0  0 0 1 1 1 1 1 1 1 1 1 0 0 0 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0           | 1     |   |   | 0 |    | A11            |             |

| A0 D7 D6 D5 D4 D3 D2 D1 D0  0 1 1 1 1 1 1 1 1 1 0  1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0                | 1     |   |   | 0 |    | A10            |             |

| D7 D6 D5 D4 D3 D2 D1 D0  1 1 1 1 1 1 1 1 1 0  1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                     | 1     | 1 |   | 1 |    | SOD            |             |

| D6         D5         D4         D3         D2         D1         D0           1         1         1         1         1         1         0         1         1         0         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         0         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1           | 1     | 1 |   | 1 | D7 |                |             |

| D5 D4 D3 D2 D1 D0  1 1 1 1 1 1 0 1 0 1 1 0 1 1 1 0 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1      | £1-12 | 1 |   | 1 | D6 |                |             |

| D4 D3 D2 D1 D0  1 1 1 1 0 1 0 0 1 1 0 0 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1     | 1 | 1 | 1 | D5 | 8275 <u>RD</u> |             |

| D3 D2 D1 D0  1 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0      | 1     | 1 | 1 | 1 | D4 | 8275 CS        |             |

| D2 D1 D0  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1<br>1<br>1<br>1<br>1<br>1<br>0<br>1<br>0<br>1<br>0                                    | 1     |   | 1 | 1 | D3 | 8275 DACK      |             |

| D1 D0  1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        | Î     |   | î | 1 | D2 | 8275WR         |             |

| DO  O O O O O O O O O O O O O O O O O O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1      | 0     |   | 1 | 1 | D1 | 6116           |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1           | 1     |   |   | 0 | DO | 2716           |             |

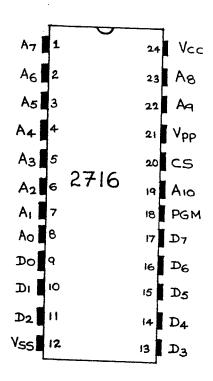

## 2.4. Chracter Generator

The character generator used in this terminal is a 2716 EPROM. The three low-order line count outputs (LCO-LC2) from the 8275 are connected to the three low order address lines of the character generator and the seven character generator outputs (CCO-CC6) are connected to the A3-A9 of the character generator. The output from the character generator is loaded into a shift register and the serial output from the shift register is the video output of the termial.

Now let us assume that the letter E is to be displayed. The ASCII code for E is 45H. So 45H is presented to address lines A2-A9 of the character generator. The scan lines will now count each line from 0 to 7 to form the character. This same procedure is used to form all 128 possible characters.

It should be obvious tht "custom" character fonts could be made by just changing the bit pattern in the character generator PROM.

45H = 01000101

Address to PROM

= 01000101 SL 2 SL1 SL0

= 228H - 22FH

CHARACTER GENERATOR OUTPUT

| ROM ADDRESS | ROM HEX<br>OUTPUT | - 0 | 1 | B)<br>2 | IT ( |   | PUT<br>5 | 7 |                   |

|-------------|-------------------|-----|---|---------|------|---|----------|---|-------------------|

| 228Н        | 3E                |     | * | *       | *    | * | *        |   |                   |

| 229Н        | 02                |     | * |         |      |   |          |   |                   |

| 22AH        | 02                |     | * |         |      |   |          |   |                   |

| 22BH        | 0E                |     | * | *       | *    |   |          |   |                   |

| 22CH        | 02                |     | * |         |      |   |          |   |                   |

| 22DH        | 3E                |     | * |         |      |   |          |   | W. Change Company |

| 22EH        | 0C                |     | * | *       | *    | * | *        |   | arron markundans  |

|             |                   |     |   |         |      |   |          |   |                   |

|             |                   |     |   |         |      |   |          |   |                   |

|             |                   |     |   |         |      |   |          |   |                   |

|             |                   |     |   |         |      |   |          |   |                   |

Bits 0, 6 and 7 are not used.

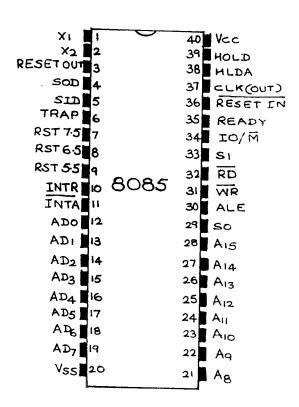

### 2.5. Description of 8085

The 8085 is the heart of the circuit. It is the LSI microprocessor chip. It needs only a single +5V supply for its working. It has a built in timing oscillator and works by connecting a crystal between its pin Numbers 1 and 2. The frequency upto which it can be worked is generally 6mHz, but we are making use of 3.127 MHz crystal.

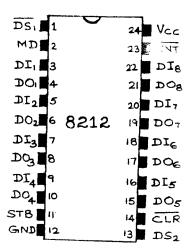

In the 8085 chip, the low order byte of address bus is multiplexed with the data byte.

Therefore the lower order address byte has to separate from the data byte to obtain the 16 line address bus and 8 line data bus. The 8212, latch 12 used for this purpose. The 8085 generates a positive pulse at pin 30 known as ALE (Address Latch Enable). Using this pulse, we latch the low order address lines in 8212.

Next the standard control bus consists of

- a) Memory Read (bar) MR.

- b) Memory write (bar) Mw.

- c) Input part (bar) IN.

- d) Output part (bar) OUT.

- e) IN terrupt Acknowledge (bar) INTA.

Memory Read (bar) means that memory's Read when this line goes low.

INTA is available from the 8085 chip itself. But MR, Mw, IN and OUT are not directly available. Instead there are only 3 lines from the 8085 chip namely 10/M, RD and WR. By using one 7400 and one 7404, we can seperate the 4 control lines MR, Mw, IN and OUT.

The 8085 chip has 40 pins, it is esential to clearly understand each pin is to be connected. Let us first account for the 40 pins.

High order address lines (OUT) - 8 pins Low order address and data (OUT) - 8 pins Address latch enable out - 1 pin +5V and ground line (IN) - 2 pin Crystal for oscillator (IN) - 2 pin INTERRUPT input pins (IN) - 5 pins Interrupt acknowledge pins (IN) - 1 pin HOld (DMA) IN - 1 pin Hold acknowledge (DMA OUT) - 1 pin Reset (input) - 1 pin Reset out - 1 pin Clock out - 1 pin 10/M, RD and MR (OUT) - 3 pin

| Status lines (out) | - 2 pins |

|--------------------|----------|

| Ready (in)         | - 1 pin  |

| Serial date (IN)   | - 1 pin  |

| Serial data (OUT)  | - 1 pin  |

## Detail of 8085 :

$\rm S_0$  and  $\rm S_1$  are status lines, which along with 10/M provides information regarding the nature of the Job, that the Cpu is executing.

| 0 | 0 | 1 | - Memory write                            |

|---|---|---|-------------------------------------------|

| 0 | 1 | 0 | - Memory read                             |

| 1 | 0 | 1 | - 1.0 write (OUT)                         |

| 1 | 1 | 0 | - 1.0 Read (IN)                           |

| 0 | 1 | 1 | - OP - code fetch                         |

| 1 | 1 | 1 | <ul> <li>interrupt acknowledge</li> </ul> |

| * | X | Х | - Hold                                    |

| * | X | x | - Reset                                   |

| * | 0 | 0 | - Halt                                    |

<sup>\* • 3</sup> state (high impedance)

x = Unspecified

READ (INPUT) : Should be high for normal memory Read/write opertion. If taken low, the Cpu will wait (normally tied to +5V).

RESET (INPUT) : Should be normally high. When taken low, the

Cpu is Reset.

RESET (OUT) : Can be used as system reset.

CLOCK OUT : Has half the crystal frequency and can be

used as the system clock.

SID : The data on this line is loaded into the

(SERIAL INPUT accumulator  $^{\mathrm{D}}7$  whenever RIM (Reset interrupt

**DATA)** mask) instructinis executed.

SOD : This is set or reset as specified by the SIM

(SERIAL OUTPUT instruction

DATA)

All Reset and interrupt lines are normally at 0 and when taken high, interrupt occurs.

### Interrupt Priority Table

TRAP

RST 7.5

RST 6.5

RST 5.5

INTR.

(INTR INPUT) interrupt request is used as a general purpose interrupt. It is disabled by RESET and immediately after a interrupt is accepted. It is also enabled and disabled by software.

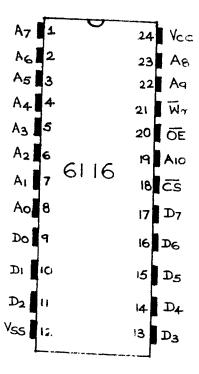

#### 2.6 Display RAM: 6116

This [6116 - a 2K x 8 RAM memory] is used to store two set of 1024 words. This must be loaded with required messages using a microprocessor chip 8085. This form part of the total microprocessor memory and is addressable both by the microprocessor as well as the CRT controller. Only when one reads or writes a message word into this memory does the microprocessor select this RAM. At all other times the CRT controller only repeatedly reads its words sequentially to form rows with characters on the screen.

### 2.7 Address Buffer (8212)

In the 8085 chip the low & order byte of address bus is multiplexed with the date byte.

Therefore the low order address byte has to be seperated from the data byte to obtain the 16 line address bus and 8 line data bus. The 8212 address buffer is used for this purpose. The 8085 genertes a positive pulse at pin 30 known as ALE (Address Latch Enable) using this pulse. We latch the low order address lines in 8212.

Since the data lines can be either in Read or Write mode a address buffer is needed for the data bus. Its direction control selects the direction according to Reading or Writing mode, while the enable line enables the buffer, if the microprocessor wants to Read/Write into the RAM.

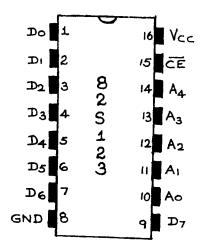

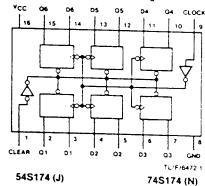

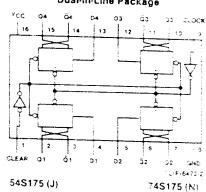

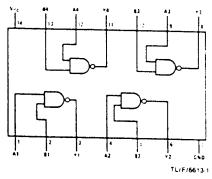

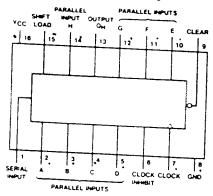

#### 2.8 Shift Register

This shift register shifts the data sent from the character generator in 8 bit parallel form into a sertal form. ie one bit after another so, this is called as parallel input serial output (PISO) shift register. The dot pattern comes out of the shift register one by one. This IC has in addition to the 8 bit parallel input and pair of output lines (Q and  $\overline{Q}$ ) a load pin which loads the parallel data into the 8 bit shift register and a clock input pin which is the serial dot clock.

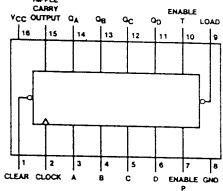

#### 2.9 Counter: 74163

Like shift registers. Counters are composed primarily of flip flops with a samll amount of added combinational logic. The main control input of the counter is the count in line. When the counter is enabled, a pulse on count in line causes the transformation.

Since the count in line triggers a single state change in the counter, it is also called the clock signal. A sequence of pulses on count in line makes the counter pass through a sequence of states and hence the counter effectively counts the number of pulses applied to its count in line. 74163 a synchronous counter is wired to divide the clock by eight. So that each character slot occupies 8 dots. Its output is given to the CRT Controller Chip to tell it that the next character is on the way.

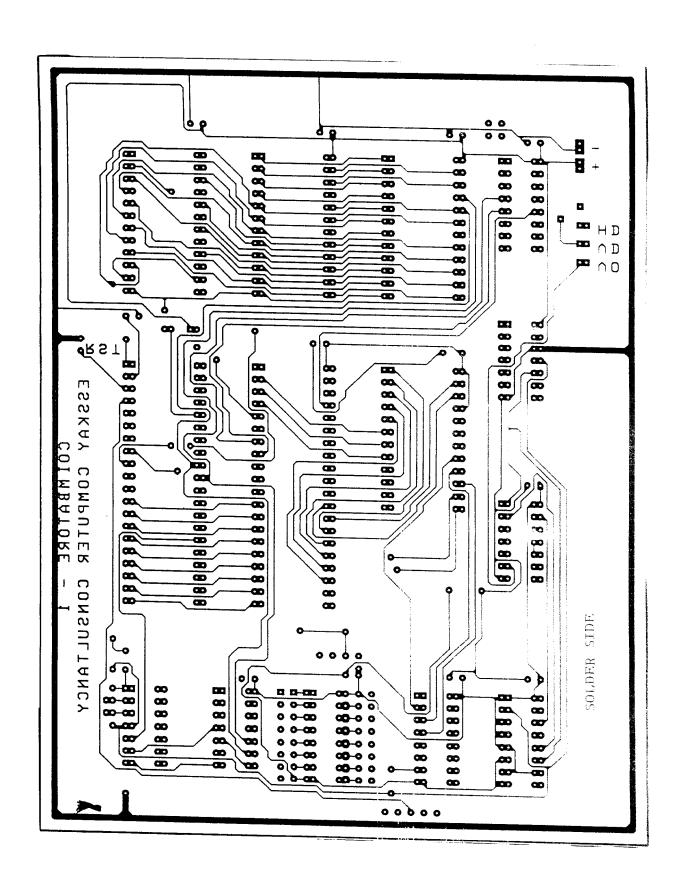

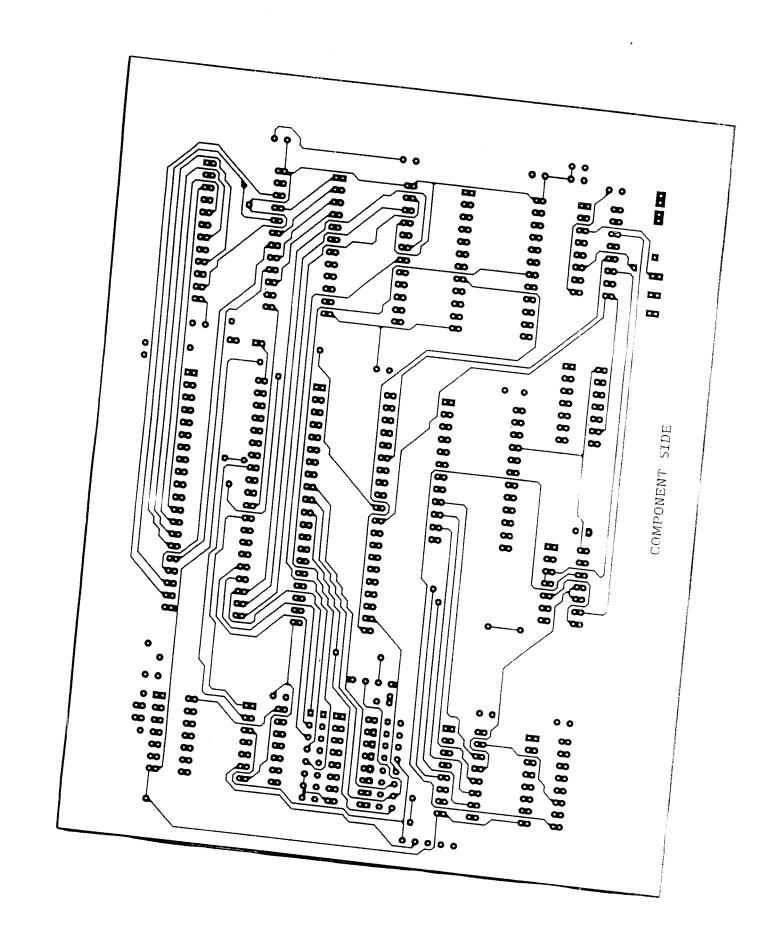

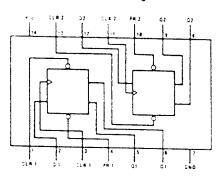

## 2.10 Hardware Description

The "heart" the CRT terminal is the of 8085 microprocessor. The 8084 initialises all devices in the system, the CRT controller, assembles the characters to be transmitted, decodes the incoming characters and determines where the character is to be placed on the screen.

The 8275 is used as the CRT controller in the system, and a 2716 is used as the character generator. To handle the high speed portion of the terminal the 8275 is surrounded by a small handful of TTL gates. The programme memory is contained in one 2716 EPROM and the data and screen memory use 6116 type RAM.

All decices in this system are memory mapped. A bipolar PROM is used to decode all of the addresses for the RAM, ROM and the 8275. The bipolar PROM also turns  $\overline{\text{READS}}$  into  $\overline{\text{DACKS}}$  and  $\overline{\text{WRITES}}$  for the 8275. If this same terminal were designed using MCS-85 family of integrated chips additional port savings could have been realised.

Video RAM (6116) address lines are connected to microprocessor and CRT controller address lines via buffer, except when required by the micro-processor video RAM continuously being addressed by the address lines AO-A9 of CRT controller. This words emerge one by one from memory chip and get latched by 74175.

The parallel input data from the EPROM is converted to serial data by parallel input serial output synchronous shift register. The Dot clock determines the width of dot and character and the output from the PISO gives the required video informatin for CRT.

SYSTEM OPERATION

#### CHAPTER - III

#### SYSTEM OPERTION

## 3.1 System Functioning

The 8085 CPU initialises each peripheral to the appropriate mode of opertion following system reset. When a character has been received, the 8085 decodes the character and takes appropriate action. While the 8085 is executing the above "foreground" programs it is being interrupted once every 617 microseconds by the 8275. This "background" program is used to load the row buffers on the 8275 is also interrupted once every frame time to read the status of 8275.

A special POP technique is used to rapidly move the contents of the display RAM into the 8275's row buffers. The characters are then synchronously transferred to the character code outputs CCO - CC6. Connected to the character generator are address lines A3-A9. Line count outputs LCo-LC2 from the 8275 is applied to the character generator address lines A0-As. The 8275 displays character rows one line at a time. The line count outputs are used to determine which line of character selected by A3-A8 will be displayed. Following the transfer of the first line to the dot timing logic the line count is incremented and the second line of the charcter row is selected. The process continues until the last line of the row is transferred to the dot timing logic.

The dot timing logic latches the output of the character genertor ROM into a parallel in serial out synchronous shift register. The shift register is clocked at the dot clock rate (12.48 MHz) and its output constitutes the video input to the CRT.

#### ROUTINE TO LOAD 8275's ROW BUFFERS

| Clock      | Seq. | Source       |                                   |

|------------|------|--------------|-----------------------------------|

| Cycles     |      | Statement    |                                   |

|            |      |              |                                   |

| 10         | 1    | PUSH PSW     | Save A and Flags                  |

| 10         | 2    | PUSH H       | Save H and L                      |

| 10         | 3    | PUSH D       | Save D and E                      |

| 10         | 4    | •            | Load Zero into H and L            |

| 10         | 5    | DAD SP       | Put stack pointer in H and L      |

| 4          | 6    | XCHG         | Put stack in D and E              |

| <b>1</b> 6 | 7    | LHLD         | Get pointer                       |

| 6          | 8    | SPHL         | Put current line into SP          |

| 7          | 9    | MVI A,0000H  | Set mask for SIM                  |

| 4          | 10   | SIN          | Set special transfer bit          |

| 400        | 11   | POP H        | Do 40 POPS                        |

| 4          | 12   | RRC          | Set up A                          |

| 4          | 13   | SIM          | Go back 10 normal mode            |

| 10         | 14   | LXI H,0000H  | Zero H,L                          |

| 10         | 15   | DAD SP       | Stack                             |

| 4          | 16   | XCHG         | Put stack in H and L              |

| 6          | 17   | SPHL         | Restore Stack                     |

| 10         | 18   | LXI H,LAST   | Put bottom in H and $\mathbb L$   |

| 4          | 19   | XCHG         | Swap registers                    |

| 4          | 20   | MOV A,D      | Put high of DEP in A              |

| 4          | 21   | CMP H        | See it same as H                  |

| 7/10       | 22   | JNZ KPTK     | If not leave                      |

| 4          | 23   | MOV A.E      | Put low order in A                |

| 4          | 24   | CMP L        | See it same as L                  |

| 7/10       | 25   | JNZ KPTK     | If not leave                      |

| 10         | 26   | LXI H, TPDIS | H and L with top of screen return |

| 16         | 27   | KPTK:SHLD    | Put back current address          |

| 7          | 28   | MVI A,18H    | Get mask Byte                     |

| 4          | 29   | SIM          | Set interrupt mask                |

| 10         | 30   | POP D        | Get D and E                       |

| 10         | 31   | POP H        | Get H and L                       |

| 10         | 32   | POP PSW      | Get A and Flags                   |

| 4          | 33   | EI           | Enable interrupts                 |

| 10         | 34   | RET          | Go back                           |

| •          | •    |              |                                   |

Total number of clock cycles = 650 (Worst case) with a 6.144 crystal total time to fill Row Buffer on 8275 = 650 x .325 = 211.25 microseconds.

#### 3.2 System Timing

Each character is displayed on a 8  $\times$  8 field and is formed by a 5  $\times$  7 dot matrix. The 8275 allows the vertical retrace time to be only an integer multiple of the horizontal charcter line. This means that the total number of horizontal line in a frame equals 12 times the number of character lines plus the vertical retrace time, which is programmed to be either 1, 2, 3 or 4 character lines. Twentyfive display lines require 300 horizontal So, if we wish to have a horizontal frequency in the lines. neighbourhood of 15750 Hz we must choose two character lines for vertical retrace. This choice yields a net 300+ 24 = 324 horizontal lines per frame. So assuming a 50Hz frame the horizontal frequency must be = 50Hz x 324 = 16200 Hz. This value falls within our target specification of 15750 Hz with  $\pm$  500Hz variation (i.e) between 15250 Hz and 16250 Hz.

It is now known that the terminal is using 300 lines to display data and 24 horizontal lines to allow for vertical retrace and the horizontal frequency is 16200Hz. In this design 80 charcter can be displayed on a horizontal line and was empirically found that allowing 20 horizontal character lines for retrace gave the best results. So in reality there are 100 character lines. It should be noted that if too many character lines are used for retrace less time will be left to diaplay the character and the display will not "fill out" the screen. Conversely, if not enough character lines are allowed for retrace the display may "run off" the screen.

#### CHAPTER - IV

## DESIGN OF DOT CLOCK

#### Method: 1

The number of lines per frame can be determined by the following equation.

$$L = (H \times Z) + V$$

H - number of horizontal lines per character = 12

Z - number of rows to be displayed = 25

V - number of horizontal lines during vertical retrace = 24

Therefore L = (25x12) + 24

L = 324 lines per frame

The DOT CLOCK is calculated from the equation given below.

DOT CLOCK (Hz) = (N+R) X D X L X F

N - number of displayed charactes per row = 80

R - number of retrace character time increments = 20

D - number of dots per character = 8

L - number of horizontal lines per frame = 324

F - the frame rate in Hz = 50

Therefore DOT CLOCK (Hz) =  $(80+20) \times 8 \times 324 \times 50$ DOT CLOCK = 12.96 mHz.

#### Method: II

The horizontal frequency is calculated as given below.

Horizontal frequency = frame rate mHz x Number of horizontal lines per frame

= 50 Hz  $\times$  324

= 16200 Hz.

Total time for one horizontal line

= 1/16,200 Hz

= 61.7 micro seconds

Vertical retrace time = 61.7 micro seconds X 24 horizontal synch times

1.48 milliseconds.

One hundred Character times per complete horizontal line means that each charcter requires.

61.7 micro-seconds/100 character times = 617 nanoseconds.

Therefore horizontal retrace time =  $617 \text{ nsec } \times 20 \text{ retrace times}$

= 12.34 microseconds.

Now, the 617 nanosecond character clock period is known and the dot clock period is easy to calculate. Here each character is formed by placing 8 dots along the horizontal line.

Dot clock period

Character clock/8 dots

617 nsec/8

77.125 nanosec.

Therefore dot clock frequency

= 1/77.125 nanosec.

DOT CLOCK FREQUENCY

= 12.96 mHz.

SYSTEM SOFTWARE

## PROGRAM TO BLANK DISPLAY RAM

| 0000 | LXIH, 0800H  | 21,00,08 |

|------|--------------|----------|

| 0003 | MVI B,OFH    | 06,OF    |

| 0005 | MVI C,FFH    | OE,FF    |

| 0007 | XYZ: LDA 20H | 3A,20    |

| 0009 | MOV M,A      | 77       |

| 000A | INX 4        | 23       |

| 000B | MOV A,B      | 78       |

| 000C | CMP H        | ВС       |

| 000D | JNZ XYZ      | C2,07,00 |

| 0010 | MOV A,C      | 79       |

| 0011 | CMP L        | BD       |

| 0012 | JNZ XYZ      | C2,07,00 |

# PROGRAM TO MOVE ONE BLOCK OF MEMORY FROM 2716 TO DISPLAY RAM

| 0015<br>0018<br>001B | LXID OBE6H<br>LXIH 0500H<br>MVI C,15H | 11,E6,OB<br>21,00,05 |

|----------------------|---------------------------------------|----------------------|

| 001D                 | PQR: MOV A,M                          | 0E,15<br>7E          |

| 001E                 | STAX D                                | 12                   |

| 001F                 | DCR C                                 | OD                   |

| 0020                 | INX H                                 | 23                   |

| 0021                 | INX D                                 | 13                   |

| 0022                 | JNZ : PQR                             | C2, 1D,00            |

## 8275 INITIALIZATION

| 0025 | LXI H,1001H | 21,01,10 |

|------|-------------|----------|

| 0028 | MVI,M OOH   | 36,00    |

| 002A | DCX H       | 2B       |

| 002B | MVI M,4FH   | 36,4F    |

| 002D | MVI M,99H   | 36,99    |

| 002F | MVI M, FCH  | 36,FC    |

| 0031 | MVI M, 39H  | 36,39    |

| 0033 | INX H       | 23       |

| 0034 | MVIM, 23    | 36,23    |

|      |             |          |

## PROGRAM TO DISPLAY

| 0036 | CALL:EI         | FB       |

|------|-----------------|----------|

| 0037 | LXI SP, OFD6H   | 31,D6,OF |

| 003A | PUSH PSW        | F5       |

| 003B | PUSH H          | E5       |

| 003C | PUSH D          | D5       |

| 003D | LXI H, 0000H    | 21,00,00 |

| 0040 | DAD SP          | 39       |

| 0041 | XCHG            | EB       |

| 0042 | LHLD,0800H      | 2A,00,08 |

| 0045 | SPHL            | F9       |

| 0046 | ABC: MVI A, COH | 3E, 00   |

| 0048 | SIM             | 30       |

| 0049 | POP H           | E1       |

|      | POP H           | E1       |

|      |                 |          |

. 40 times

POP H

| 0071 | RRC         | OF                      |

|------|-------------|-------------------------|

| 0072 | SIM         | 30                      |

| 0073 | LXI,H,0000H | 21,00,00                |

| 0074 | DAD SP      | 39                      |

| 0075 | MOV A,D     | 7A                      |

| 0076 | CMP H       | BC                      |

| 0077 | JNZ:ABC     | C2,46,00                |

| 0078 | MOV A,E     | <b>7</b> B              |

| 0079 | CMP L       | BD                      |

| 007A | JNZ:ABC     | C2,46,00                |

| 007B | JMP:CALL    | C3,36,00                |

| 007C | HALT        | 76                      |

| 04FE | BLANK       | 20                      |

| 04FF | BLANK       | 20                      |

| 0500 | W           | 57                      |

| 0501 | E           | 45                      |

| 0502 | L           | 4C                      |

| 0503 | С           | 43                      |

| 0504 | 0           | 4F                      |

| 0505 | M           | 4D                      |

| 0506 | E           | 45                      |

| 0507 | BLANK       | 20                      |

| 0508 | T           | 54                      |

| 0509 | 0           | 4F                      |

| 050A | BLANK       | 20                      |

| 050B | E           | 45                      |

| 050C | BLANK       | 20                      |

| 050D | С           | 43                      |

| 050E | BLANK       | 20                      |

| 050F | E           | 45                      |

| 0510 | BLANK       | 20                      |

| 0511 | D           | <b>4 L</b> <sub>t</sub> |

|      |             |                         |

| 0512 | E     | 45 |

|------|-------|----|

| 0513 | P     | 50 |

| 0514 | T     | 54 |

| 0515 | BLANK | 20 |

| 0516 | BLANK | 20 |

| 0517 | BLANK | 20 |

|      |       |    |

CONCLUSION

## CHAPTER - VI

#### CONCLUSION

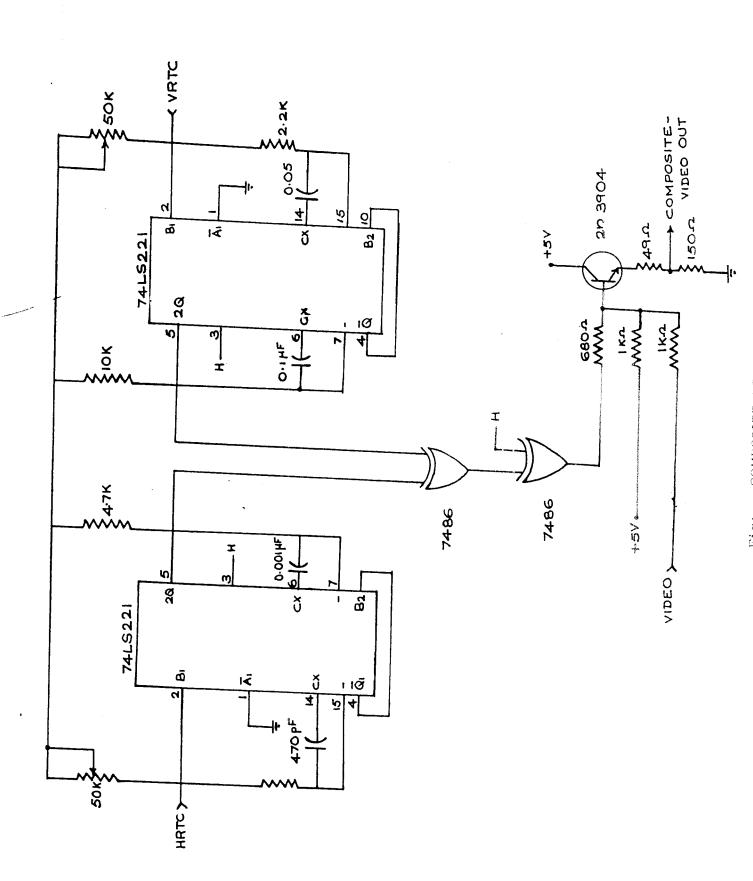

### 6.1 Composite Video

In this it was assumed that the monitor required a separate horizontal drive, vertical drive and video input. However many monitors require a Composite Video signal. The schematic shown in Fig.5.1 illustrates how to generate a Composite Video signal from the output of the 8275.

The dual shots are used to provide a small delay and proper horizontl and vertical pulse to the composite video monitor. The delay introduced in the vertical and horizontal timing is used to "center" the display. VR1 and VR2 control the amount of delay. 1C3 is used to mix the vertical and horizontal retrace and 01 along with R1, R2 and R3 mix the video and the retrace signal and provide the DC levels.

## 6.2 Keyboard Interface

This design can be made more veasatile and dynamic by making use of a keyboard. The keyboard can be interfaced by using two parts of 8255 parallel 1/0 device.

When the system is initialized the contents of the keyboard RAM locations are set to zero. Once every frame which is 16.67 milliseconds the contents of the keyboard RAM is read and then rewritten with the contents of the current switch matrix. If a non zero value of one of the keyboard RAM locations is found to be the same as the corresponding current switch matrix, a valid key push is registered and action is taken. By operating the keyboard in this manner an automatic debounce time of 16.67 milliseconds is provided.

## BIBLIOGRAPHY

| 1. | Microprocessor architecture, programming and applications. |

|----|------------------------------------------------------------|

|    | - GAONKAR.                                                 |

| 2. | Microprocessors and Interfacing.                           |

|    | - DOUGLIS V.HALL                                           |

| 3. | Trouble shooting microprocessor - Based system.            |

|    | - ALLAN.H.ROBBINS/                                         |

|    | BRIAN LUNDEEN                                              |

| 4. | Logic data book, Volume-II.                                |

|    | - NATIONAL SEMI- CONDUCTOR CORPORATION                     |

| 5. | Learn to use microprocessors.                              |

|    | - EFY PUBLICATIONS.                                        |

**APPENDIX**

# PROGRAMMABLE CRT CONTROLLER

- Programmable Screen and Character

Format

- s 6 incopendent Visual Field Attributes

- ា 11 Visual Character Attributes ខ្លី (Graphic Capability)

- Cursor Control (4 Types)

- a Light Pen Detection and Registers

- Fully MCS-80<sup>TM</sup> and MCS-88<sup>TM</sup> Compatible