# PC COMMUNICATION THROUGH AC POWER LINES

#### PROJECT REPORT

SUBMITTED BY

P-213

K. Ganesh K. Kalai Selvi P. Kamalakkannan

UNDER THE GUIDANCE OF MISS. P. SUPRIYA, B.E., M.I.S.T.E.,

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR AWARD OF THE DEGREE OF

#### BACHELOR OF ENGINEERING

IN ELECTRICAL AND ELECTRONICS ENGINEERING OF THE BHARATHIAR UNIVERSITY, COIMBATORE

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

#### KUMARAGURU COLLEGE OF TECHNOLOGY

# DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

# JMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE - 641 006

# CERTIFICATE )

This is to Certify that the Report Entitled

# PC COMMUNICATION THROUGH AC POWER LINES

HAS BEEN SUBMITTED BY

| Mr. / Miss.                                          | 1 Realizator al                       |

|------------------------------------------------------|---------------------------------------|

| in partial fullilment for the award of the Degree of | y Bacheror of                         |

| Suginoprina in Electrical and Electronics Eng        | uneeury                               |

| Branch of the Bharathiar University, Coimbator       | ne - 641 046<br>Dr. K. A. DALANII - 1 |

| during the academic year 1994 - 9                    | 95<br>2000 - 1000 - 1000              |

| ,                                                    | Dapariment of Electricum and in-      |

|                                                      | ម្រីមាននៅនទួលបាន 🐪 👙                  |

|                                                      | Colombat Color                        |

HEAD OF THE DEPT

| Certified that the candidate was examined by us in the | ? |

|--------------------------------------------------------|---|

| Project work Viva-Voce examination held on             | _ |

| and the University Register Number was                 |   |

#### CONTENTS

| ACKNOWLEDGEMENT | Δ | CK | ΝJ | TWIT | EL | GE | M | EN | T |

|-----------------|---|----|----|------|----|----|---|----|---|

|-----------------|---|----|----|------|----|----|---|----|---|

#### SYNOPSIS

- 1. INTRODUCTION

- 2. SYSTEM DESCRIPTION

- 2.1. AC POWER LINE

- 2.2. CHIP ARCHITECTOR

- 2.3. TYPICAL PERFORMANCE

- 2.4. FEATURES OF IC LM 1893

- 3. CIRCUIT DESCRIPTION

- 3.1. INTRODUCTION

- 3.2. HOW TO USE LM 1893

- 3.3. WAVE FORMS

- 4. DESIGN

- 5. FUNCTIONAL DESCRIPTION

- 5. . INTRODUCTION

- 5.2. DINE CONTROL REGISTED

- 5.3. BIT DESCRIPTION

- 5.4. PROGRAMMABLE BAUD RATE GENERATOR

- 5.5. LINE STATUS REGISTER

- 5.6. INTERRUPT IDENTIFICATION REGISTER

- 5.7. INTERRUPT ENABLE REGISTER

- 6. SOFTWARE DESCRIPTION

- 7. SOFTWARE LISTING

- 8. CONCLUSION

PEFERENCES

APPENHIX I

PERSONAL X 33

APIEMDIX III

#### ACKNOWLEDGEMENT

We are profoundly grateful to our guide Miss. P.SUPRIYA, B.E., MISTE., Associate Lecturer in EEE department, for her valuable guidance and encouragement for the successful completion of this project.

We express our gratitude to our Head of the the Department Dr. K.A. PALANISWAMY M.Sc (Engg), Ph.D., MISTE.

C.Engg(I)., FIE for his suggestions and ideas to pursue the project work without delay.

We take this opportunity to thank our princpal Dr. S.SUBRAMANIAN Ph.D., for providing facilities to carry out the project in the College.

We would like to thank Thiru. S. KOLANDAIVELU B.E., Ms.S.K. Engineering and controls, Erode and Thiru RAJA, M.E., LECTURER, I.R.T.T. ERODE for their help to do this project.

We express our sincere thanks to all staff members of the EEE and CSE departments for their kind co-perations.

# PC COMMUNICATION THROUGH AC POWER LINES

#### **CONTENTS**

Page No. **SYNOPSIS** CHAPTER I INTRODUCTION CHAPTER 2 SYSTEM DESCRIPTION CHAPTER 3 CIRCUIT DESCRIPTION CHAPTER 4 DESIGN CHAPTER 5 FUNCTIONAL DESCRIPTION CHAPTER 6 SOFTWARE DESCRIPTION AND FLOW CHARTS CHAPTER 7 SOFTWARE LISTING CONCLUSION REFERENCES

APPENDIX I

APPENDIX II

#### SYNOPSIS

Computers, the miraculous machines, have bright future for the decades to come. To increase their power and intelligence, they should have proper channels to communicate between them and the world. The communication of computer are sure to shrink the world to its smallest extent.

Our project PERSONAL COMPUTER COMMUNICATION THROUGH A.C. POWER LINES is one way of giving the computer an effective communicating power.

The Basis of carrier current communication is the transmission and reception of a carrier, modulated by data over the A.C lines. The carrier current chip utilises FSK modulation not only for its excelent impulse noise rejection but also for the simplicity of implementation in both the transmitter and receiver sections.

The carrier current communication of computers has its own versatility for their higher communication power with low cost. Due to complexity and noise interference it is not normally implied for their greater advantages.

We have succeeded in doing this PC communication through AC power lines, with higher accuracy and less complexity.

With good future developments our system might have greater impact in the forth coming years of our country.

A good software support is also with our project for making this more effective. It is certain that our project PC communication through AC power lines will gain a lighting attraction with future expansion.

#### CHAPTER I

#### INTRODUCTION

being exchanged Everywhere around us information is between two or more points. Several methods are commonly used to convey this information, including optical, RF, ultrasonic and hardwired links. Anyone who has made use of one of these techniques will certainly remember its limitations : optical links operate only by line of sight, RF links are restricted by numerous regulations, ultrosonic links are interrupted by require the links hardwired and walls, installation of signal-carrying lines. Another alternative, a close relative of the harwired link, is carrier current communication the exchange of data via pre-existing AC lines.

The AC line makes a great data link. No after market installation is required most buildings are already wired. The link can be established anywhere there is an AC socket by simply plugging in a line cord one then wonders why such a wounderful communication link is seldom used? The answer lies in the basis of the link itself: The AC line contains not only 230V RMS of unwanted signal, but also kilo-volt spikes,

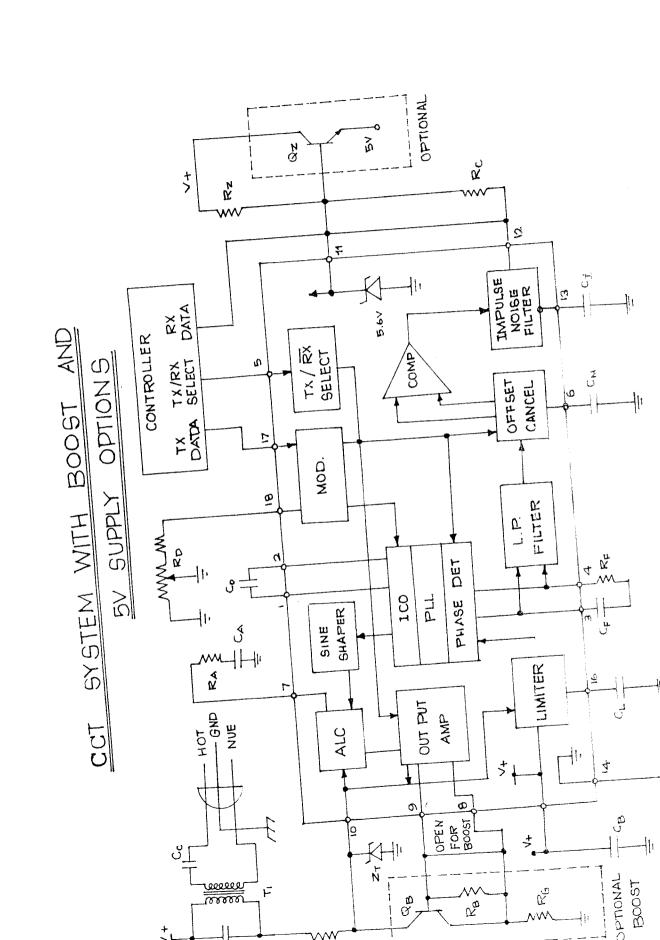

carrier current circuits. Meeting these challenges necessarily leads to complex and costly discrete circuit designs. The concept of a carrier current link should not be abandoned, however, as a recently introduced integrated circuit now offers the solution for carrier current links. This new carrier current tranceiver IC forms the heart of a sophisticated single-chip half duplex AC line links.

#### CHAPTER 2

#### SYSTEM DESCRIPTION

#### .1 THE AC POWER LINE:

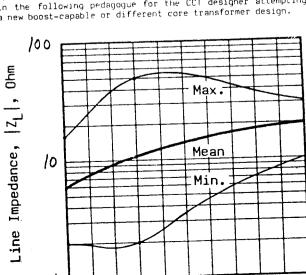

The noise on the line can be loosely put into two categories: borad band and impulse. Broad-band noise come from many sources, with universal motors being one notorious example. The level varies from a few to hundreds of millivolts. Impulse noise also varies widely in a level ranging from millivolts to tens of volts and sometimes much more. The impulses are more often than not sychronized to the power line frequency and ring with the natural frequency of the line (another widely varying parameter). The prime culprits here are switching thyristers. In general, noise is worst in factories, moderate in offices, and least in private dwellings.

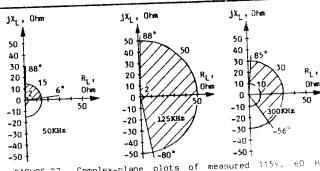

The impedance of the line is likewise ill-defined. It may be resistive, inductive or capacitive. Above 50KHz, the impedance rises to a sufficiently high value to be driven as a load (at low frequencies, it approximates a voltage source). Frequencies below 50KHz also have considerable difficulty - capacitively coupling across the windings of power distribution transformer. This is some times an asset,

but often a curse. Frequencies above 300 KHz experience greater attenuation due to the distributed LC nature of power cabling and are more adversely affected by capacitive loads in the form of line bypass capacitors that are finding increasing use in an RFI.

a range of operation the reasons stated, - 300 KHz was deemed adquate for most For 50 encompasses KHz in an office environment, an At 125 applications. considered typical. might be (5+j10)Ω impedance of home wiring may be over  $50~\Omega$ , while factory Impedances in capacitors impedances may be less than 1  $\Omega$ . Line bypass 1  $\mu f$  or more will short the carrier in most enviorments unless isolated with chokes or driven with several watts of carrier power.

Line attenuation is very difficult to estimate because it extremely load dependent. A high power load significantly reduce the impedance of the line at the point of connection and thus dominate attenuation for all points of communication that occur beyond the offending load unless load is isolated with chokes. Capacitive loads can be equally troublesome and are not necessarily with high Care must be taken to ensure that once power loads. is passed to turn on such a low carrier current command load, the command to turn it back off again will impedance

likewise be received. Another large component of the net incurred loss be the signal attenuation can coupling across the multiple windings of a power distribution. amount to 20 to This alone can transformer. depending upon the carrier frequency and transformer construction. External capacitors are effective in bridging signals across windings in areas where this is desired. The power cabling itself has little opportunity to behave like a transmission line at such low frequecies, although the distributed LC losses can become significant for extreme cases of attenuation, frequency In runs. translating repeaters can be used to boost signal levels or brute force signal power can be exployed.

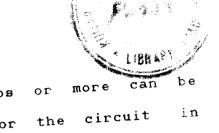

# 2.2 THE CHIP ARCHITECTURE :

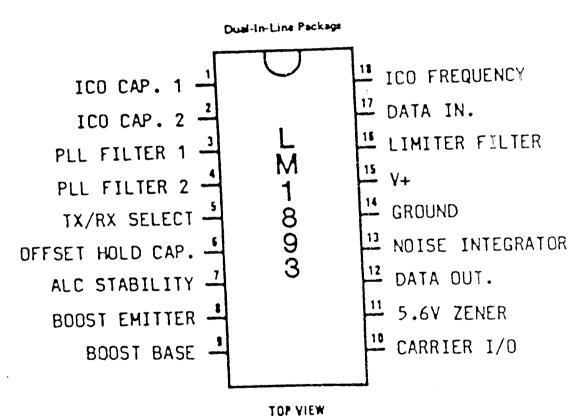

The chip architecture is shown in fig 1. The important blocks and its functions are given below,

#### 2.21 MODULATOR :

Modulator modulates the data signal with high frequency carrier signal. This process is called modulation. Here the transmitter utilizes the modulator which uses FSK modulation. The modulator must generate three currents representing F low, F high and F centre.

# 2.22 THE CURRENT CONTROLLED OSCILLATOR :

The ICO is shared by the RX and TX modes and thus runs continuously. It has two wide band, low TC, and linearly controllable for analog signals. Its output must be a square wave to drive PLL and good quality triangle wave to drive the sine shaper.

# 2.23 THE SINE SHAPER :

The output of the sine shaper drives the Automatic Level Controller (ALC). The triangle wave is first attenuated to the optimum amplitude and then used to switch a differential pair degenerated at the optimum level. The tuned output transformer reduces the distortion to typically below 0.1 percent before it is fed to the line.

# 2.24 OUTPUT AMPLIFIER :

The constraints imposed by the power line interface were felt most severly by the output stage; These constraints, coupled with several other circuit requirements meant that the output stage had to meet the following formidable list of criteria,

1. Ability to withstand and protect the whole chip from high energy line transient.

- 2. High current gain equal to 200.

- 3. Gain boostable with external device to greater than 2000.

- 4. Sufficient gain-bandwidth product to pass a large signal at 300 KHz

- 5. Ability to be easily put into a high impedance state.

- 6. Ability to withstand an indefinite short circuit.

- 7. Ability to maintain waveform purity with loads that range from near shorts to near open circuits.

- 8. Ability to maintain closed-loop stability for any value of complex load impedance.

- 9. Ability to swing to nearly twice the supply voltage.

- 10. Ability to tolerate large supply ripple.

#### 2.25 THE LIMITER :

The limiter provides some needed amplification (33dB) for the PLL. It also removes some amplitude noise, as well as band limiting the input to lie between 50 and 300 KHz. The signal from the line passes through the tuned transformer where it is stepped up and filtered of extraneous signals, noise and 50 Hz.

line voltage importance of the rejection of the 50 Hz The 120 Hz supply ripple should not be underestimated. and acheieve 1 mv sensitivity, 50 Hz must be rejected by dB and 120 Hz by at least 63 dB. The high pass 107 characteristics at the input to the transformer, the stage and the balance of the input itself. frequency selective feedback amplifier all combine to acheieve these numbers.

#### 2.26 PHASE LOCKED LOOP :

The PLL is essentially a frequency feedback system comprising a phase comparator, a low pass filter, an error amplifier in the forward signal path and a voltage controlled oscillator (VCO) in the feedback path. The operation of the PLL as follows,

When there is no input signal to the PLL, error voltage V The VCO operates at a set frequency fo known as the free running frequency. If an input signal ) is applied to the PLL, the phase comparator compares phase and frequency of the input signal with the ACO and generates an error voltage Ve(t) that is related to the phase and the frequency difference between filtered, then Ve(t) is The signals. the amplified and applied as input to the VCO. effect The

Vd(t) is to force the VCO frequency to vary in a direction that reduces the frequency difference between the VCO output and the input signal. If fs is sufficiently close to fo , the feedback nature of the PLL causes the VCO to synchronize with the incoming signal. Once synchronized, fo is identical to fs , except for a finite phase difference (Ø). This is necessary to generate the corrective error voltage Vd to shift the VCO frequency from its free running value of fs , thereby maintaining the PLL in lock.

# 2.27 THE OFFSET CANCEL CIRCUIT :

Due to the high gain in the signal path, some provision has to be made for cancelling offset voltage prior to accurate data slicing in the comparator. Straight forward capacitive coupling will eliminate offset, but has a lower frequency limit problem (if the capacitor is sized small enough for rapid changing in a TX to RX switch over) and will charge to the net dc value of the data, thus restricting users to keeping the signal duty cycle near 50 percent.

DC feedback loops also cannot separate dc inherent in the data from dc offset. The offset cancelling circuit will eliminate dc offsets from the data path without responding to

itself. Strings of 100 ones or zeros or more can be accommmodated and the setup time for the circuit in switching from TX to RX is only two bit times.

# 2.28 THE TIME DOMAIN FILTER :

Impulse noise creates severe problems for carrier current systems. Fortunately, the impulses do not usually last very long provided no tuned circuits in the system can store substantial energy. By keeping data rates low (less than 1K baud is recommended), the noise pulses will usually be significantly shorter than data pulses. This means a filter that discriminates against noise based upon its time duration rather than its frequency spectrum can be quite useful. The time domain filter used here is very simple, yet very effective in removing impulse noise. The external capacitor it uses can be selected to set the time cut off; the minimum pulse width that the filter allow to pass.

# 2.3 TYPICAL PERFORMANCE :

#### <u>GENERAL</u>

| Supply voltage |         |                   |         |     |     |       |     |

|----------------|---------|-------------------|---------|-----|-----|-------|-----|

| Programmable   | •       | fneguenc <b>v</b> | Fo      | .50 | to  | 300   | KHZ |

| Programmable   | carrier | II eque           | - · · · | +   | 100 | \ mag | ° C |

| Occillator TC  | of Fo   |                   |         |     | 200 |       |     |

#### TRANSMITTER

|                                              | ± 2.5%       |

|----------------------------------------------|--------------|

| FSK deviation                                | 60mA p-p     |

|                                              |              |

| 100}                                         |              |

|                                              |              |

| 100)                                         |              |

| +imA.                                        |              |

| RX to TX Switch over time                    |              |

| RECEIVER                                     |              |

|                                              | 1mV rms      |

| Sensitivity  Data rate                       | 0 to 4K Baud |

| Data rate                                    | 2 bits       |

| Data rate  TX to RX switch over time         | 13 mA        |

| TX to RX switch over transfer Supply Current | 11 4         |

For Pin Details of LM 1893 TRANSCEIVER IC Refer APPENDIX 1

# 2.4 FEATURES OF LM 1893 IC :

- \* Noise resistant FSK modulation.

- \* User selected impulse noise filtering.

- $\star$  Up to 4.8 Kbaud data transmission rate.

- $\star$  Strings of 0's and 1's in data allowed.

- \* Sinsoidal line drive for low RFI.

recally boosted 10-fold.

- \* 50 to 300 KHZ carrier frequency choice.

- \* TTL and MOS compatible digital levels.

- \* Regulated voltage to power logic.

- \* Drives all conventional power lines.

# CIRCUIT

# CIRCUIT DESCRIPTION

# 3.1 INTRODUCTION; -

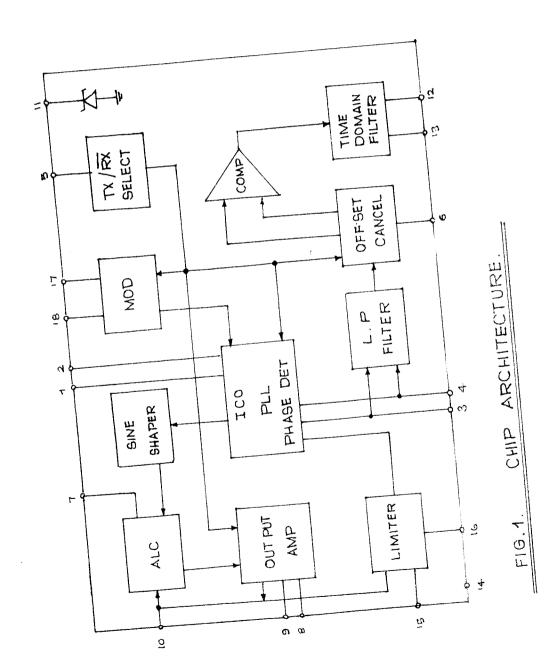

Each line interface requires one chip along with a handful of inexpensive passive components. A simple unregulated supply with up to 2V p-p of ripple can be used. Three logic compatible ports DATA IN, DATA OUT and TX/RX Three logic compatible ports DATA in, DATA out and TX/RX SELECT, interface to the digital circuitry, while the fourth line from the 5.6 V Zener diode can be buffered with an n.p.n emitter follower and used to power the digital circuitary.

When in the transmit mode, the incoming serial data stream switches the modulator which drives the low TC current controlled osicllator (ICO) to produce a triangle wave with a 12.5 percent frequency deviation. The triangle wave is then attenuated and fed to a sine shaper which delivers a current sinusoid through an automatic level control (ALC) circuit to the power current amplifier. The tuned transformer converts the 60mA p-p current sinusoid to a voltage that depends upon line impedance, steps the voltage down, and then drives the line through a coupling capacitor. Should line impedance be high, the ALC circuit diverts signal current away from the output amplifier to maintain waveform purity by preventing

saturation of the amplifier.

the receive mode, the DATA IN PORT is inhibited, transmitter output is put into a high impedance state and the is set to run at the carrier center frenceny. ICO coupling capacitor and tuned transformer pass the desired large degree and a signal while attenuating 50 to Ηz filtering out some noise. A rugged Norton-input limiter noise certain and Hzfurther attenuates 50 amplifier components before passing the signal to the PLL detector. The demodulated output from the second order loop passed through a three stage differential low pass filter and on the offset cancelling circuit. After Vos has been removed, the data are then accurately separated into ones and zeros (sliced) by one comparator. At this point, the data often still riddled with impulse noise, pass through a time domain filter before driving the open-collector output stage.

# 3.2 HOW TO USE THE LM 1893 TRANSCEIVER :-

#### 3.21 PURPOSE :-

The purpose of this kit is to provide the designer with a complete LM 1893 circuit which can be easily adapted to an existing digital system for evaluation. To this end the enclosed printed circuit board has been designed to be as compact as possible. All of the special components required for operation are included in this kit. The assembled board require an 18V, 100ma power supply, 3 connection to the

associated digital circuitry, and two connections to the power line.

#### 3.22 PRECAUTIONS :-

The power line is a potential source for diaster, and several precautions are recommended: First, a line cord with a polarized plug must be used. Neutral (N) is to be connected to the coil side of the input and live (L) to the 220nF line coupling capacitor. The capacitor must have a breakdown rating of at least 1.5 times the RMS line voltage. Failure to use a capacitor with adequate voltage rating will result in a shock and fire hazard. In addition, capacitors of lower voltage ratings may explode when connected to the line. When the power line portion of the board has been assembled it is wise to place a strip of PVC electrical tape over the copper side to reduce the chance of an accidental short circuit. Two small mounting holes have been included and should be used to secure the board (copper side down) to a solid surface.

Energy at the power line frequency is greatly attenuated by the input coupling network. Large energy surges can still occur at or near the band pass frequency of this network. While the LM 1893 is designed to absorb a 30W pulse, much higher power levels are often experienced. To handle these

and 5.1  $\Omega$  resistor are connected to the chip side of the coupling network, and the Zener diode is included in this kit.

#### 3.23 TUNING

This kit is intended to operate at a carrier frequency of 125 KHz and a data rate of 360 baud. Before the boards are used this tuning procedure must be followed,

- Attach a frequency counter to the prongs of the power cord

Note that the power cord must NOT be plugged into the line

- Temporarily tie pins 5 and 17 to pin 15.

- 3. Connect an 18V power supply and adjust the trim pot for indicated frequency of 122.25KHz.

- 4. Remove the power supply and the connections made in step 2. the input coupling network tuning is affected by the impedance of the power line. Therefore, tuning must be adjusted with the power cord connected to the line, or to an impedance simulation network. If one power line is involved, extreme caution must be exercised during this procedure.

- 5. Temporarily connect pin5 to pin15 (v+)

- 6. Temporarily connect a 390  $\Omega$  resistor from pin 10 to 15,

- Input a data stream (360 baud) or 5V square wave (180 7. Hz) to pin17.

- Connect an 18V power supply. 8.

- Plug power cord into line and adjust T1 for equal 9. amplitude signal envelopes as carrier follows modulation.

- Disconnect power cord from line. 10.

- Disconnect supply, signal, 390  $\Omega$  resistor and pin 5 11. jumper.

LM 1893 has been disigned with digital interface in The The digital input (pin17) and the transmit/receiver switch (pin5) are designed to accept all standard 5V logic levels. The digital output (pin12) is an open collector. Holes are provided on the board to optionally pull this pin up to 5.6V. In this instance, Rz must be sized accordingly to carry the current of pin 12.

# 3.24 LINE COUPLING TRANSFORMER :

Essential to the transformer is its loaded Q. Loaded Q is function of frequency, parallel load resistance, and The coil supplied has a primary inductance of inductance. 49 $\mu H$  and gives a loaded Q of approximately 10 at 125 KHz. A tapped secondary provides matching into 2.5, 5 and 5

10

# 3.25 LINE COUPLING CAPACITOR :-

Since this component is connected to the power line, its breakdown voltage rating is important. The part supplied is rated at 400V and is adequate for up to 250V power lines.

#### 3.26 COUPLING COIL:-

The coupling coil plays an important role in transmitting and receiving signals on the A.C line. To fully understand the design of this coil, one must consider the characteristics of the A.C line. Generally the A.C.line, measured at a frequency of 100 KHz, can be modelled as a resistor and an inductor connected in series. Typical line parameters are shown in fig (4)

The inductance parameter varies widely regardless of environment, resistance shows a much stronger dependence. Industrial environments present a resistance of 2 to  $5\Omega$  and residential environments shows a resistance of 5 to  $30\Omega$ . Impedance also varies with changes in the loading of the AC line.

With such unpredictable line impedance, coupling the output amplifier is difficult. The coupling will couples signal to one line via a step down secondary.

When operating in receive mode, the coupling line performs several important functions. These include

- 1. 50Hz Rejection

- 2. Signal Bandpassing

- 3. Ohmic Isolation from the AC line.

In addition the coupling coil is connected in such a way so as to step up the received signal by a factor of the turns ratio.

The general electrical characterisics, transmitter electrical characterisics and receiver electrical characterisics are shown appendix II

#### 3.3 WAVE FORMS :-

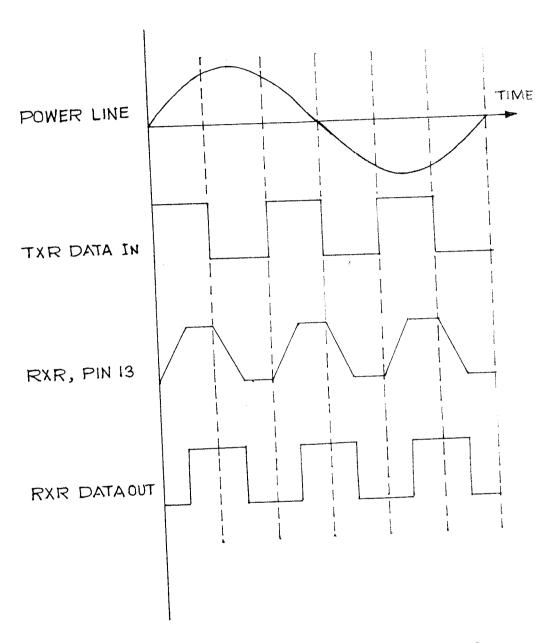

Operating wave forms of a line synchronized tranceiver pair are shown. The diagram shown how the transmitted data transitions may be used as received data sampling points. The wave forms are shown in fig (3)

FIG. 3. OPERATING WAVE FORMS

# DESIGN

#### CHAPTER 4

#### DESIGN

The circuit consists of the following components

R , R , Q , R and C . The design is carried out T B B B G

by referring APPENDIX 2.

Typical value of all the components for  $V^{+}=18v^{-}$ , Fo = 125 KHz, F = 360 Baud using 230V , 50Hz power line DATA

are given below,

# 4.1 Co and Ro :

: Together, Co and Ro set ICO Fo. Co: Purpose

: Increases Fo Smaller

: Decreases Fo Larger

Recommended Value: 560 pF

Ro:

: Together, Co and Ro set ICO Fo. Purpose

: Increases Fo Smaller

: Decreases Fo Larger

4 Value : 6.2 KOhm

```

4.2 C and R :

: PLL Loop Filter pole.

Purpose

: Less noise immune, higher E DATA

Smaller

more PLL stability

: More noise immune, lower F

Larger

less PLL stability

Recommended Value : 0.047~\mu F

R

F

: PLL Loop Filter zero

Purpose

: PLL less stable, allows less C .

Smaller

Less ringing.

: PLL more stable, allows more C .

Larger

More ringing.

Recommended Value: 3.3 KOhm

Сc

4.3

Сc

Couple Fo to line, Cc and T1

```

Purpose

Smaller : Low TX line amplitude. Less 50

low-pass attenuates 50 Hz.

: Drives Lower line Z. More 50 Hz Ti Larger

current. More stored charge

Recommended Value :  $0.22~\mu F$

: Tank matches line Z, bandpass Purpose

filters, isolates from line and

attenuates transients

: Tank Fo up or increase L of Tl for Smaller

constant Fo Smaller L: Higher Fo

or increase Cc; decreased Fo

line pull

: Tank Fo down or decrease L of T1 Larger

for constant Fo Larger L: Lower

Fo or decrease Cc; increased

line pull

Recommended Value :  $0.033~\mu F$

4.4 C and

: Tank matches line Z bandpass filters, isolates from line an Purpose

attenuates transients

: Tank Fo up or increase L of T1 for constant Fo Smaller L: Higher Fo or increase Cc; decreased Fo line pull

: Tank Fo down or decrease L of T1

for constant Fo Larger L: Lower Fo

or decrease Cc; increased Fo line

pull

Recommended Value :  $0.033~\mu F$

T :

Purpose : Tank matches line Z, bandpass filters, isolates from line and attenuates transients

: Tank Fo up or increase L of T1 for constant Fo Smaller L: Higher Fo or increase Cc; decreased Fo line pull

: Tank Fo down or decrease L of T1

for constant Fo Larger L: Lower Fo

or decrease Cc; increased Fo line

pull

Recommended Value: Use recommended XFMR

4.5 C and R :

C A

Purpose : ALC pole

Smaller : Noise spikes turn ALC off.

Larger : Slower ALC response

Recommended Value:  $0.1~\mu F$

K A

Purpose : ALC zero

Smaller : Less stable ALC

larger : More stable ALC

Recommended Value: 10 KOhm

4.6 C :-L

Purpose : Limiter 50 kHz pole, 50 Hz rejection

Smaller : Higher pole F, more 50 Hz reject. Fo attenuation.

: Lower pole F, less 60 Hz reject, more noice BW. Larger

Recommended Value:  $0.1 \mu F$

4.7

: Holds RX path V Purpose

: Less noice immune, shorter V hold faster Smaller

V aquisition, shorter preamble.

V hold , slower : more noice immune, longer os Larger

aquisition, longer preamble. 0S

Recommended Value: 0.47 μF

4.8

Rejects short pulses like impulse Purpose noise.

Less impulse reject, delay Smaller

More impulse reject, delay Larger

Recommended Value :  $0.47~\mu F$

4.9 R :-

Purpose : Open-col. pull up

Smaller : Less available sink I .

Larger : Less available source I .

Recommended Value: 10 KOhm.

4.10 R :-

Purpose : 5.6 V Zener bias

Smaller : Larger shunt current, more chip dissipation

Larger : smaller shunt current, less V+ current draw

Recommended Value: 12 KOhm.

4.11 Z and R :-

Z :

Purpose : Transient clamp

Smaller : Higher R - excess peak V, Zener and chip Z damage.

Larger : Lower R gives enhanced transient clamp,

Z

costly.

- - - - - - - AA V BV

R

: Transient I limit Purpose

: Damage Z , pull up V+ . Smaller

: Excessive TX attenuation . Larger

Recommended Value: 4.7 Ohm.

4.12

R В

> : Base bleed Purpose

: Faster , lower THD  ${\bf I}$  . Smaller

: Inadequate turn-off speed . Larger

Recommended Value: 180 Ohm.

В

: Boost gain device . Purpose

: Excessive I and V SAT Smaller

: More rugged, but costly .

Recommended Value: Power NPN .

R :-

Purpose : Current setting R .

Larger : Less I , lower min. h fe

Recommended Value: 1.1 Ohm.

4.13 C :-B

Purpose : Supply bypass .

Smaller : Transients destroy chip.

Larger : Less supply spike .

Recommended Value:  $\geq$  47  $\mu F$ .

#### CHAPTER 5

## FUNCTIONAL DESCRIPTION

The data is serially transmitted and received through the asynchronous communication port which supports RS-232C standards. In the IBM PC serial ports are configured as COM1 and COM2. The addresses for these ports

COM 1 3F8 - 3FF H

COM 2 2F8 - 2FF H

The communication port utilises INS 8250 for serial transmission and reception. To do this it has a number of accessible registers. These registers can be controlled by programmer through PC.

## LINE CONTROL REGISTER :

The system programmer specifies the format of the asynchronous data communications through the line register. In addition to this we may retrieve the contents of the line control register for inspection. This feature simplifies the system programming.

Bit 7 - Divisor latch access bit.

Bit 6 - Set break.

Bit 5 - Stick parity.

Bit 4 - Even parity select.

Bit 3 - Parity enable.

Bit 2 - No. of Stop bits.

Bit 1 - Word length select bit 1.

Bit 0 - Word length select bit 0.

## 5.3 BIT DESCRIPTION :

#### Bit 0 & 1 :

These two bits specify the number of bits in each transmitted or received serial character. Encoding of bits are as follows.

| n 1   | Bit O | Word length |

|-------|-------|-------------|

| Bit 1 | 0     | 5 bits      |

| 0     | U     | 6 bits      |

| 0     | 1     |             |

| 1     | 0     | 7 bits      |

| 1     | 1     | 8 bits      |

| 1     |       |             |

#### Bit 2 :

This bit specifies the number of stop bits in the transmitted or received serial character. If this is logical '0' one stop bit is generated or checked in the received data. If it is logical '1', when a 5 bit word length is selected, then 1% stop bits are generated or checked.

#### Bit 3:

This is the parity enable bit. When bit3 is logic 1 a parity is generated (transmitted data) or checked (received data).

#### Bit 4:

This is the even parity select bit. If it is logic '1' and bit 3 is logical '1' transmission and checking is done for even number of bits. If it is logical '0' odd parity is established.

#### Bit 5 :

This bit is stick parity bit.

#### Bit 6:

This is set break control. If this is logical '1' the serial output is forced to the spacing state and remains there regardless of the transmitter activity.

#### Bit 7:

Device latch access bit, which is set high to access the devisor latches of the baud rate generator during a read or write operation. It is set slow to access the receiver buffer.

## 5.4 PROGRAMMABLE BAUD RATE GENERATOR :

INS 8250 contains a programmable baud rate generator that is capable of taking the system clock and dividing it by any divisor from 1 to 216. Two 8 bit latches are used to store the divisor. The divisor used for generating various baud rate are

|      | In Hex |

|------|--------|

| 50   | 900    |

| 75   | 600    |

| 110  | 417    |

| 150  | 300    |

| 300  | 180    |

| 1200 | 060    |

| 1800 | 040    |

#### 5.5 LINE STATUS REGISTER :

The status information concerning the data transfer from a processor is provided. The bit indication are given below.

| Hex Address | 3 FD H                    |

|-------------|---------------------------|

| Bit 7       | 0                         |

| Bit 6       | Tx Shift register empty   |

| Bit 5       | Tx Holding register empty |

| Bit 4       | Break interrupt           |

| <b>5</b> 3  | Framing error             |

Bit 2 parity error

Bit 1 over run error

Bit 0 Data ready

## 5.6 INTERRUPT IDENTIFICATION REGISTER :

INS 8250 has an on chip interrupt capability that allows complete flexibility in interfacing it to almost all the microprocessor. It priorities into four levels.

- 1. Receiver line status.

- 2. Received data Ready.

- 3. Transmitter circuit holding register empty.

- 4. Modem status.

respectively.

## 5.7 INTERRUPT ENABLE REGISTER :

It controls the interface with the modem. It is of 8 bit length.

Bit 7,6,5

Bit 4 Loop Back

Bit 3 Out 2

Bit 2 Out 1

Bit 1 Request to send

Bit 0 Data terminal ready

The receiver buffer register which contains the received character which is of 8 bit length.

8 bit transmitter holding register contains the The character to be serially transmitted.

bit modem status register provides the current state of the control lines from the modem to the PC.

## - 232C STANDARD :

This is the universal standard followed for the serial data communication. Here the logical states 0 and 1 represented by +12 and -12 voltage. The logical 1 which represented by -12V is done so in order to reduce the noise interference and to increase the accuracy of reception. Special purpose IC's are available for converting the digital into RS - 232C standards. In this IC communication our serial communication. A 9 pin RS - 232 connector is used in PC communication whose details are enclosed in appendix TII

## 1489 RS - 232 RECEIVER :

the transmitter transmits the data of 5 m V logic, so it is important to convert the RS 232C output of  $12 extsf{V}$  into it is done by 1489-RS232 Receiver Chip. Pin detail 5**V** Appendix III.

# 1488 RS = 232C DRIVER :

To communicate with the PC, the received 5V signal must be converted into 12V which is done by 1488 RS 232 driver. For pin detail see appendix III.

#### CHAPTER 6

## SOFTUARE DESCRIPTION

A proper software support to satisfy the requirements of our system is also provided. The software is developed in 'TURBO C'.

Here the communication between computers takes place through the asynchronous communication port. The speed with which the information gets transmitted (Baud rate) is programmable using the file MODE.COM in DOS.

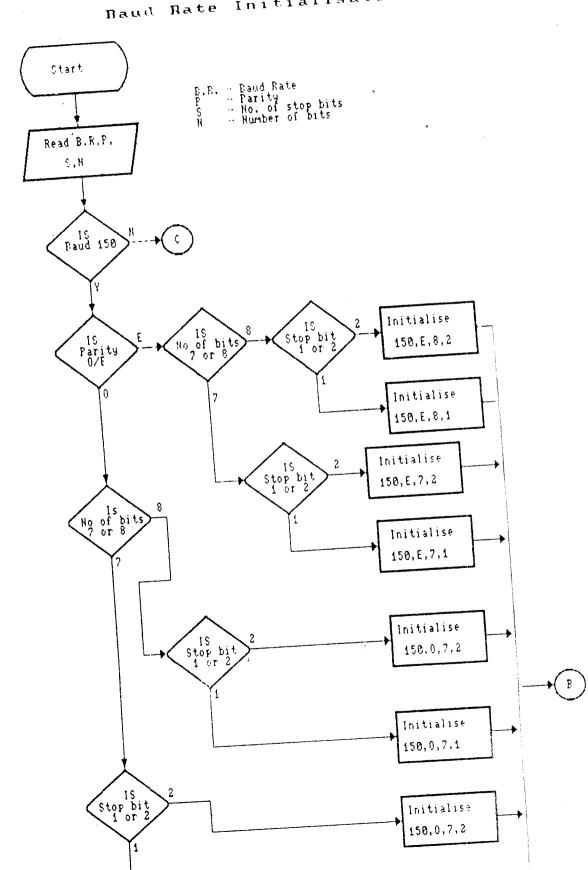

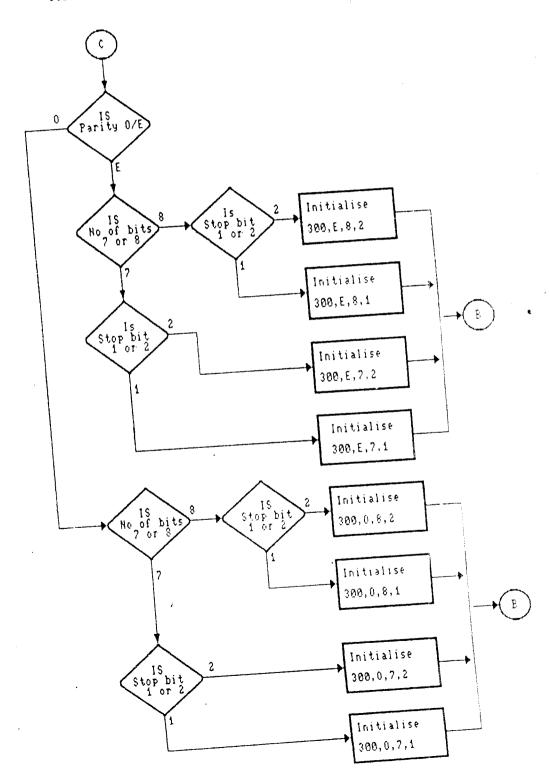

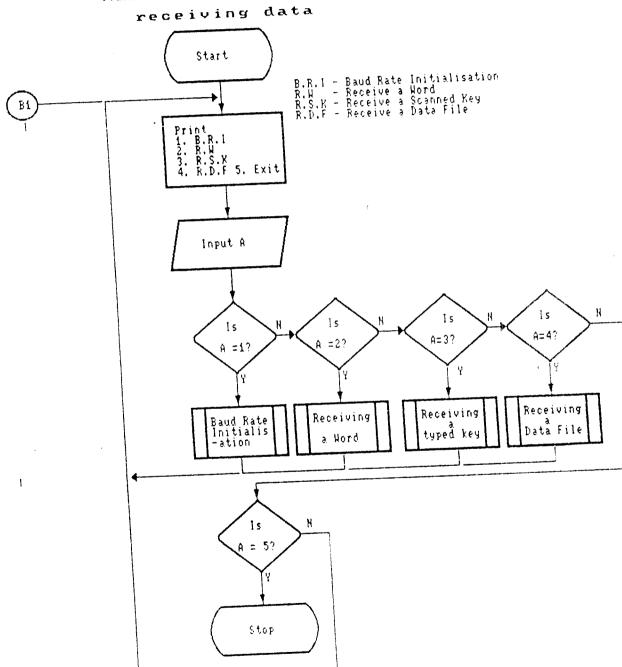

Our system can operate under 150 and 300 baud. The initialisation of baud rate with all necessary options like type of parity, number of stop bits and number of bits etc., can be done from our software itself. As we enter into the software and choose the first option the computer will request for the initialisation operation.

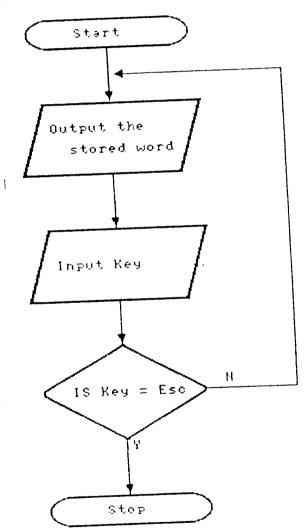

Operations 2,3,4 from the three modes of transmission in our system. Using option 2 we can transmit a set of words continuously aso that a synchonisation can be achived between the transmitter and receiver, provided the initialisation that the systems.

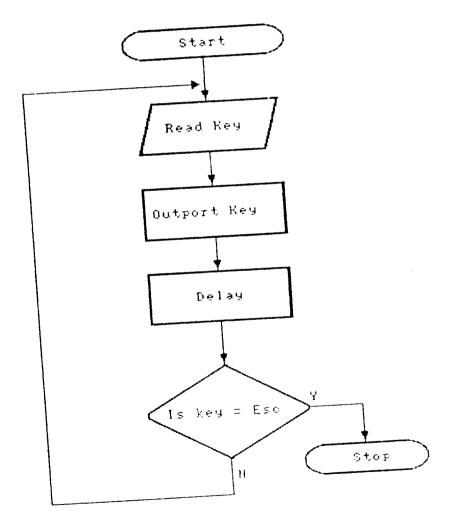

The Next option transmits a scanned Key (ie) any key pressed on the keyboard is converted into the corresponding ASCII and gets transmitted. We have provided facility to return from the option to the main menu which is done by pressing the ENTER KEY.

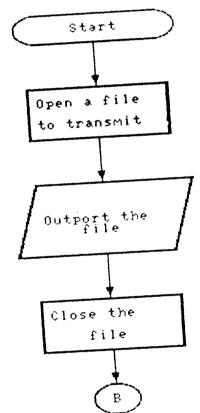

The fourth option is for data file transmission. Any data file can be transmitted through Rs-232 and can be received at the receiver. For the users knowledge the data file while transmission is monitred in the screen. Again at the receiving end the data received is displayed on the computer moniter and gets stored to secondary devices like floppy diskettes.

The last and final option is to quit from out software. When this option is selected the compter comes out of our software saying "GOOD BYE".....! and waits for further usage in the DOS prompt.

The above mentioned options are all provided in receiving computer and should be properly selected for receiving the transmitted signal.

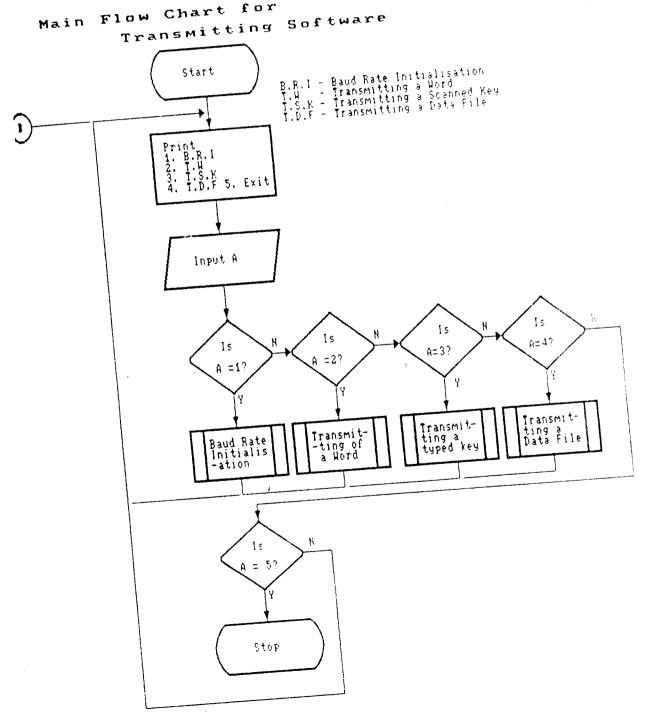

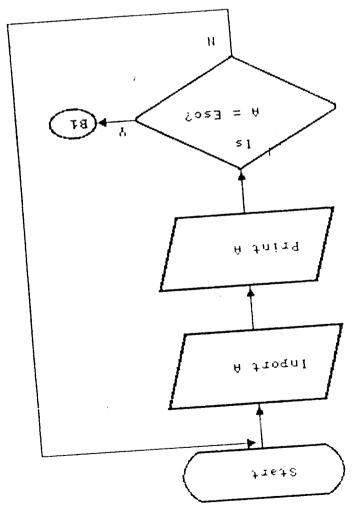

Flow Chart for Software Transmitting

Baud Rate Initialisation

When Baud Rate is 300

## Transmit a Name (Contineously)

# Transmitting A scanned Key

# Transmitting a Data File

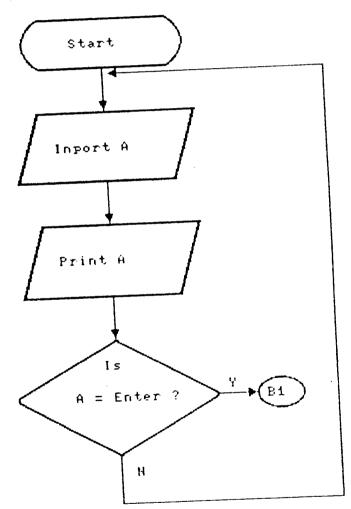

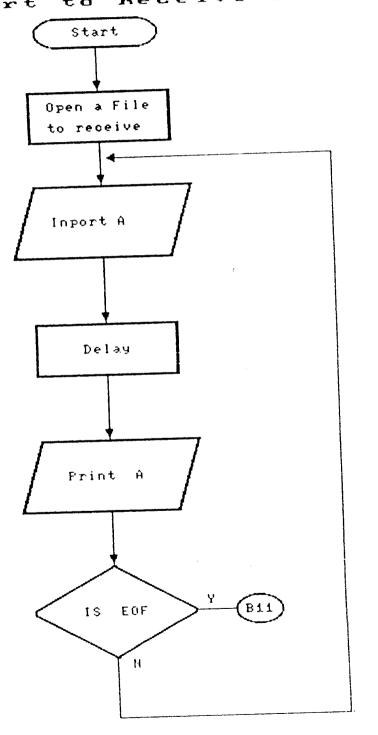

## Main flow chart for receiving data

Plow Chart to receive Plancontanco emen a

Flow chart for receiving a scanned key

Flow Chart to Receive a File

# SOFTWARE

#### CHAPTER 7

#### PROGRAM LISTING

```

The Main Program For Transmission .... transmit.c */

#include <process.h>

#include <dos.h>

#include (stdio.h)

#include <conio.h>

#include <graphics.h>

#include "modemo.h"

#include "MOD3.h"

#include "outname.h"

#include "outtype.h"

#include "filetran.h"

main()

/* definitions */

int i, j;

char c;

podee();

clrscr();

textmode(C80);

textattr(WHITE+(BLACK<<0));

clrscr();

window(2,1,78,24);

textbackground(LIGHTBLUE);

```

```

gotoxy(1,6);

putch(200);

for (i=2;i<77;i++)

{

gotoxy(1,6);

putch(205);

gotoxy(78,6);

putch(188);

for (j=5; j>1;--j)

{

gotoxy(1,j);

putch(186);

}

for(j=5;j>1;--j)

gotoxy(77,j);

putch(186).

}

gotoxy(1,1);

putch(201);

for(i=2;i<77;++i)

{

gotoxy(i,1);

putch(205);

```

```

gotoxy(77,1);

putch(187);

gotoxy(1,7);

putch(218);

gotoxy(77,1);

putch(191);

for(i=8;i<23;++i)

{

gotoxy(1,i);

putch(179);

gotoxy(77,i);

putch(179);

)

gotoxy(1,23);

putch(192);

gotoxy(77,23);

putch(217);

for(i=2;i<77;++i)

gotoxy(i,7);

putch(196);

gotoxy(i,23);

putch(196);

}

gotoxy(23,3);

```

corintf("PC

THROUGH

COMMMUNICATION

```

LINES");

textcolor(CYAN);

gotoxy(25,10);

cprintf("1. BAUD RATE INITIALIZATION

gotoxy(25,13);

cprintf("2. TRANSMITTING A WORD ");

gotoxy(25,16);

cprintf("3. TRANSMITTING SCANNED KEY");

gotoxy(25,19);

cprintf("4. TRANSMITTING A DATA FILE ");

gotoxy(25,22);

cprintf("5. EXIT ");

c=getch();

((c=='1') ||.'(c=='2') || (c=='3') || (c=='4')

II (c=='5'))

switch (c)

case '1': initialize();/* Baud Rate Initialisation

* /

break;

case '2': clrscr();

gotoxy(40,20);

textcolor(WHITE);

cprintf("Transmission is going on . .

/* Transmitting a word */

");

word();

```

```

clrscr();

break;

case '3': textcolor(WHITE);

scan(); /* Transmitting a scanned key */

clrscr();

break;

case '4': clrscr();

textattr(YELLOW+(CYAN<<4));

dataf(); /* Transmission of a Data

File

clrscr();

break;

case '5': textattr(WHITE+(BLACK<<0));

clrscr();

gotoxy(30,20);

cprintf("G 0 0 D B Y E .....!");

sound(650);

sleep(l);

nosound();

exit(0);

}

goto tt;

}

```

\* /

```

podee()

{

int gd=MCGA,gm=0,c;

initgraph(&gd,&gm,"");

cleardevice(:

setbkcolor(RED);

settextstyle(GOTHIC_FONT,0,4);

setcolor(YELLOW);

outtextxy(20,35,"PC COMMUNICATION");

outtextxy(70,65,"THROUGH");

outtextxy(120,95,"AC POWER LINES");

getch();

cleardevice();

setbkcolor(BLUE);

settextstyle(SANS_SERIF_FONT,0,3);

setcolor(BROWN);

outtextxy(5,20,"Guided By :");

settextstyle(TRIPLEX_FONT,0,2);

outtextxy(35,50,"Miss.P. Supriya");

getch();

cleardevice();

setbkcolor(BROWN);

setcolor(BLUE);

settextstyle(GOTHIC_FONT,0,3);

outtextxy(10,10,"Project Done By :");

"++aytyv(60.40," * K.Ganesh");

```

```

outtextxy(50,70,"** K.Kalaiselvi");

outtextxy(40,100,"*** P.Kamalakkannan");

getch();

closegraph();

```

}

```

/*---- PROGRAM FOR BAUD RATE INITIALIZATION

/*---- File Name : MOD3.H

initialize()

{

int i=0, j=0, baud, no, st;

char par[10];

clrscr();

textmode(C80);

textattr(WHITE+(BLACK<<4));

clrscr();

textattr(WHITE+(RED<<4));

window(2,1,78,24);

clrscr();

gotoxy(1,6);

putch(200);

for (i=2;i<> (+4))

(

gotoxy(i,6);

putch(205);

gotoxy(78,6);

putch(188);

for(j=5;j>1;--j)

{

```

```

putch(186);

}

for(j=5;j>1;--j)

(

gotoxy(77,j);

putch(186);

}

gotoxy(1,1);

putch(201);

for (i=2;i<77;++i)

{

gotoxy(i,1);

putch(205);

}

gotoxy(77,1);

putch(187);

gotoxy(1,7);

putch(218);

gotoxy(77,7);

putch(191);

for(i=8;i<23;++i)

{

gotoxy(1,i);

putch(179);

gotoxy(77,i);

. . . . . . . . . . . .

```

```

gotoxy(1,23);

putch(192);

gotoxy(77,23);

putch(217);

for(i=2;i<77;++i)

{

gotoxy(i,7);

putch(196);

gotoxy(i,23);

putch(1983)

}

textcolor(WHITE+BLINK);

gotoxy(23,3);

POWER

AC

THROUGH

cprintf("PC COMMUNICATION

LINES");

textcolor(CYAN);

gotoxy(4,9);

cprintf("Baud Rate Required (150/300)? : ");

cscanf("%d", &baud);

gotoxy(4,12);

: ");

(0/N)?

cprintf(" Type Of Parity

cscanf("%s",par);

gotoxy(4,15);

: ");

cprintf("Number Of Bits

(7/8)

cscanf("%d",&no);

gotoxy(4,18);

```

```

cscanf("%d",&st);

getch();

gotoxy(50,15);

clrscrt,,

textattr(WHITE+(BLACK<<0));

clrscr();

setdisk(0);

if (baud==150)

{

if(par=='0')

switch (no)

{

case 7:

{

if(st==1)

{

system("mode com1:150,0,7,1,p");

setdisk(2);

break;

}

else

{

system("mode

com1:150,0,7,2,p");

setdisk(2);

```

```

break;

}

}

case 8:

{

if(st==1)

system("mode com1:150,0,8,1,p");

setdisk(2);

break;

}

else

{

system("mode

com1:150,0,8,2,p");

setdisk(2);

break;

}

}

else

{

switch (no)

{

```

```

case 7:

{

if(st==1)

{

system("mode com1:150,n,7,1,p");

setdisk(2);

break;

}

else

{

system("mode

com1:150,n,7,2,p");

setdisk(2);

break;

}

}

case 8:

{

if(st==1)

{

system("mode com1:150,n,8,1,p");

setdisk(2);

break;

}

else

{

```

```

system("mode com1:150,n,8,2,p");

setdisk(2);

break;

}

}

}

)

else

{

if(pars o)

switch (no)

{

case 7:

{

11(st==1)

{

system("mode com1:300,0,7,1,p");

setdisk(2);

break;

)

else

{

system("mode

```

```

setdisk(2);

break;

}

}

case 8:

{

if(st==1)

{

system("mode com1:300,0,8,1,p");

setdisk(2);

break;

}

else

{

system("mode

com1:300,0,8,2,p");

setdisk(2);

break;

)

}

}

)

else

{

switch (no)

```

```

case 7:

{

if(st==1)

(

system("mode com1:300,n,7,1,p");

setdisk(2);

break;

}

else

{

system("mode

com1:300,n,7,2,p");

setdisk(2);

break;

}

)

case 8:

(

if(st==1)

{

system("mode com1:300,n,8,1,p");

setdisk(2);

}

}

```

```

)

}

getch();

```

}

```

/*---- PROGRAM TO TRANSMIT A WORD CONTINEOUSLY

/*---- File Name : OUTNAME.H

word ()

{

int i,q;

char a,b,c,d,e,f,g,h,j,k,1,m,n;

void fool();

for (q=1;q<20;q++);

(

a='G';

i=a;

outport(0x3f8,i);

fool();

p='0';

i=b;

outport(0x3f8,i);

fool ();

c='D';

i=c;

outport(0x3f8,i);

fool ();

d=' ';

i=d;

outport(0x3f8,i);

fool ();

e='I';

```

```

outport(0x3f8,i);

fool ();

f='S';

i = f;

outport(0x3f8,i);

fool ();

g=' ';

i=g;

outport(0x3f8,i);

fool ();

h='G';

i=h;

outport(0x3f8,i);

fool ();

j='R';

i=j;

outport(0x3f8,i);

fool ();

k='E';

i=k;

outport(0x3f8,i);

fool ();

1 = ' X ' .

i=1;

outport(0x3f8,i);

fool ();

```

```

i=m.

outport(0xJt8,i);

fool();

n=' ';

i=n;

outport (0x3f8,i);

fool();

}

void fool()

{

delay(1500);

```

}

```

/*---- PROGRAM TO TRANSMIT A TYPED KEY -----*;

/*----*/

scan ()

{

int i,k;

char c;

clrscr ();

do

{

outport (0x3f8,0);

c=getch();

i=c;

outport (0x3f8,i);

putch(c);

delay (500);

outport(0x3f8,0);

for (k=1; k<168; k++);

}

while (i != 13);

```

}

```

/* -----* PROGRAM FOR TRANSMITTING A DATA FILE -----*

FILETRAN.H

dataf()

{

FILE * fpt;

int i=2, a;

char d;

fpt = fopen ("kct.dat", "r");

while (!feof(fpt))

{

d=getc(fpt);

a=d;

outport(0x3f8,a);

printf ("%c",d);

delay (200);

}

for(i=0;i<=2;i++)

outport(0x3f8,0x1a);

fclose (fpt);

}

```

```

/* The main program for receiving transmitted data */

/* Receive.c

* /

#include <process.h>

#include <dos.h>

#include <stdio.h>

#include <comio.h>

#include <graphics.h>

#include "modemo.h"

#include "MOD3.h"

#include "inname.h"

#include "intype.h"

#include "filerece.h"

main()

{

int i, j;

char c;

podee();

clrscr();

textmode(C80);

tt:

textattr(WHITE+(BLACK<<0));

clrscr();

window(2,1,78,24);

textbackground(LIGHTBLUE);

textcolor(WHITE);

```

3 - - - - - - ( ) .

```

putch(200);

for(i=2;i<77;i++)

gotoxy(i,6);

putch(205);

}

gotoxy(78,6);

putch(188);

for (j=5; j>1;--j)

{

gotoxy(1,j);

putch(186);

}

for(j=5;j>1;--j)

{

gotoxy(77, j);

putch(186);

}

gotoxy(1,1);

putch(201);

for(i=2;i<77;++i)

(

gotoxy(i,1);

putch(205);

```

```

putch(187);

gotoxy(1,7);

putch(218);

gotoxy(77,7);

putch(191);

for(i=8;i<23;++i)

{

gotoxy(1,i);

putch(179);

gotoxy(77,i);

putch(179);

}

gotoxy(1,23);

putch(192);

gotoxy(77,23);

putch(217);

for(i=2;i<77;++i)

{

gotoxy(i,7);

putch(196);

gotoxy(i,23);

putch(196);

}

* /

Menu

/*

gotoxy(23,3);

cprintf("PC COMMUNICATION THROUGH AC POWER LINES");

(CVANI).

```

```

cprintf("1. BAUD RATE INITIALIZATION");

gotoxy(25,13);

cprintf("2. RECEIVING A WORD");

gotoxy(25,16);

cprintf("3. RECEIVING THE PRESSED KEY");

gotoxy(25,19);

cprintf("4. RECEIVING A DATA FILE");

gotoxy(25,22);

cprintf("5. EXIT");

if ((c=='1') || (c=='2') || (c=='3') || (c=='4')

c=getch(); '

(c=='5'))

switch (c)

case '1': initialize(); /* Baud Rate Initialisation */

break;

case '2': clrscr();

gotoxy(1,1);

word1(); /* Receiving the transmitted word

clrscr();

* /

break;

case '3': clrscr();

textcolor(WHITE);

scanl(); , Receiving the typed key */

clrscr();

```

```

case '4': clrscr();

textattr(YELLOW+(CYAN<<4));

dataf1(); /* Receiving the trasmitted

data

file */

clrscr();

break;

case '5': textattr(WHITE+(BLACK<<0));</pre>

clrscr();

gotoxy(30,20);

cprintf(" G O O D B Y E ....!");

sound(550);

sleep(1);

nosound();

exit(0);

}

goto tt;

}

```

```

/* ----- PROGRAM FOR RECEIVING A WORD CONTINEOUSLY ---- */

/* ----- File Name : INNAME.H

word1()

{

int i,k;

char c;

for(k=1;k<260;++k)

{

i=inport(0x3f8);

c=i;

printf("%c",c);

delay(1575);

}

}

```

```

File Name : FILERECE.H

dataf1()

(

FILE *frt;

int i,a;

char 1;

frt = fopen("samp.dat","w");/*Opening a file for reception

while((a=inport(0x3f8)) != 0x1a)

{

printf("%c",1);

delay(200);

l=a;

11

putc(1,frt);

fputc(1,frt);

}

fclose(frt);

}

```

#### CONCLUSION

The hardware circuitry has been fabricated, using the transceiver IC and other possible components, RS-232C is the interface link between the hardware and software. The software has been developed in 'C' language.

The pulse transmitted by the transceiver in the transmit mode has been received by the other transceiver which is in the receive mode. The pulse has been observed on the CRO as a test for the hardware functioning. By using the software the data fed as input to one PC is obtained as o/p in the other PC - the two PC's paving the way for communication.

By boosting the carrier signal, communication between PC's can be effected for long distance.

An improvement that can be made in our system is to increase the baud rate of transmission, so that audio signal transmission can be done.

#### REFERENCES

- Gray, Paul R. and Robert G. Meyer;

"Analysis and Design of Integrated Circuits" John Wiley & sons 1977;

- 2. Hayt, William H. Jr. and Jack E. Kemmerly;

"Engineering Circuit analysis" McGraw Hill Books;

1971.

- 3. Monticelli, Dennis M. and Michael E. Wright;

"A Carrier Current Transceiver IC for Data Transmission over the AC power line"; IEEE J. solid-state circuits, December 1882.

- 4. Lee, Mitchell;

- "A New Carrier Current Transceiver IC" IEEE

Transaction on consumer Electronics, August 1982.

- Gottfried,

"Programming in C" - Schaum series.

PIN DETAILS OF LM 1893.

#### Absolute Maximum Ratings

Supply voltage Voltage on pin 12

Lead temperature, soldering, 10 s.

Storage temperature range

(note 2):

2

6

12

13

14

Voltage on pin 10 (note 1) Voltage on pins 5 and 17 5.6 V DC zener current

transmit mode Junction temperature:

receive mode Maximum continuous dissipation, Ta=25°€, plastic DIP N Operating ambient temp. range

41 V 40 V 100 mA 150°C 125°C

1.66 W -25 to 85°C

-65 to 150°C

300°C

30 V

55 V

Transients may reach above  $\epsilon 0$  V; see the transient Note 2:

more detail.

peak voltage characteristic curve.

The maximum power dissipation rating should be

derated for device operation above 25°C to insure that the junction temperature remains below the maximum rating. Use a  $\theta_{\rm JA}$  of 75°C/W for the N package using a socket in still air. Consult the Application Information section for

General Electrical Characteristics (note 3)

The test conditions are: V+=18 V and  $F_0$ =125 KHz, unless otherwise noted.

| - # i | Parameter | Conditions |

|-------|-----------|------------|

|       |           |            |

|       |           |            |

Typical 5.6

Test Limit (note 4)

Limit (note 5)

Design

V min. V max.

Limit

Units

Pin 11, I<sub>Z</sub>=2 mA 1 | 5.6 V Zener voltage, V7

60

Ohm V max.

Pin 11,  $R_7 = (V_7 @ 10 mA - V_7 @ 1 mA) / (10 mA - 1 mA)$ 5.6 V Zener resistance, R7 Pin 10, discharge 1 pF cap, charged to

คก 44

5

50

V min. V max.

0hm

V max.

V min.

uA min.

µA max.

μA min.

μA max.

μs

bit

(+5.8)

Limit

(note 5)

(15) (23)

(2.0)

The transmit center frequency is  $\mathcal{E}_{ij}$ , FSK low

Test

Limit

(note\_4)

24

59

45

4.0

3.8

0.8

2.8

KHz min.

KHz mex. PPM/°C

% max.

Limit

Unite

V min.

V max.

mA max.

mApp min

V min.

V max

% max.

% max.

% min.

% max.

Carrier I/O peak survivable 3 transient voltage, VOI Pin 10, I<sub>OC</sub>=10 mA, RX mode Carrier I/O clamp voltage, VOC

Time to develop 63% of full current drive

1 bit time  $\rm I_B=1/(2F_{DATA})$  Time  $\rm I_{TR}$  is user controlled with  $\rm C_M$  , see Apps. Info.

Conditions

Pin 15. Pin 12 high.  $I_{Q\bar{1}}$  is  $I_{Q}$  through pin 15 and the average current  $I_{QDC}$  of the

Meets Test 17 spec. at T<sub>1</sub>=25°C and: |(F<sub>1</sub>[14Y]-F<sub>1</sub>[18Y])/F<sub>1</sub>[18Y]|<0.01 |(F<sub>1</sub>[24Y]-F<sub>1</sub>[18Y])/F<sub>1</sub>[18Y]|<0.01

TX mode,  $R_0 = 6.7 \text{ KOhm}$ ,  $C_0 = 560 \text{ pF}$

TX mode, (FOMAX-FOMIN)/(TJMAX-TJMIN)

20

1.8

2.2

-2

10-4

10

7

125

(+200)

(+2.0)

Typical

(12)

42

70

4.7

0.6

4.4

1.7

2.1

0.8

2.8

-20

0

n

10

Carrier I/O clamp resistance, RIO

TX/RX high input voltage, VIH

TX/RX low input current, III

RX-TX switch-over time, TRT

TX-RX switch-over time, Tight

ICO initial accuracy of Fo

Temperature drift of Fn

$F_1$ , and FSK high is  $F_2$ .

ICO temperature coefficient of Fn

Parameter

Supply voltage, V+, range

Total supply current, IUT

THD of In (note 6)

FSK deviation, F2-F1

Carrier I/O output current, Io

Data In. low input voltage, VII

Data In. high input voltage, VIH

Carrier I/O lower swing limit, VALC

TX/RX low input voltage, VII

Pin 10, I<sub>OC</sub>=10 mA

Pin 5

Pin 5 (note 9)

Pin 5 at 0.8 V

through pin 10

TX mode, -25<T3<150°C

Pin 5 at 40 V TX/RX high input current, I<sub>IH</sub>

Transmitter Electrical Characteristics (note 3)

The test conditions are: V+=18~V and  $F_{\Pi}=125~kHz$  unless otherwise noted.

19 20

22

15

16

## $(F_2-F_1)/([F_2+F_1]/2)$

Carrier I/O through pin 10

Pin 10. Set internally be ALC

Q of 10 tank driving 10 0hm line

100 Ohm load on pin 10

100 Ohm load, no tank

Pin 17

Pin 17 (note 9)

## eceiver Electrical Characteristics (note 3)

ne test conditions are: V+=18 V, F<sub>O</sub>=125 KHz, 2.2 deviation FSK, F<sub>DATA</sub>=2.4 KHz, v<sub>in</sub>=100 mVpp, in the receive mode, unless

| 13   | e noted. Parameter                                           | Conditions                                                                                                                  | Typical                                 | Test  <br>Limit  <br>(note 4) | Design<br>Limit<br>(note 5) | Limit<br>Units                         |

|------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------|-----------------------------|----------------------------------------|

| 9    | Supply voltage, V+, range                                    | Functional receiver (note 7)                                                                                                | (11)                                    | 13<br>30                      | (13.5)<br>(28)              | V min.<br>V max.                       |

| ,    | Supply current, I <sub>QT</sub>                              | In is pin 15 (V+) plus pin 10 (Carrier I/O) current                                                                         | 13                                      | 5 14                          |                             | mA min.<br>mA max.                     |

| 1    | Carrier I/O input resistance, R <sub>IO</sub>                | Pin 10                                                                                                                      | 19.5                                    | 14  <br>30                    |                             | KOhm ma<br>KOhm ma                     |

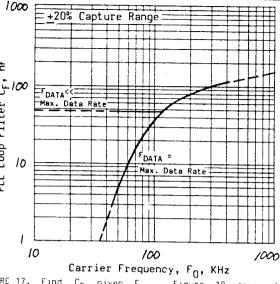

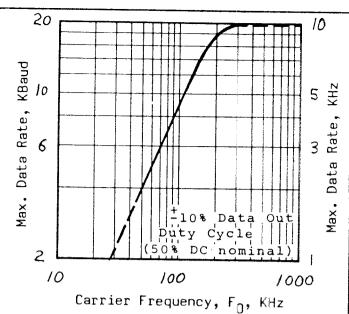

| <br> | Max. data rate, F <sub>MD</sub>                              | Functional receiver (note 7)<br>square-wave data, 2.4 kHz=4.8 kBaud                                                         | 10                                      | 4.8                           | (2-4)                       | kBsud                                  |

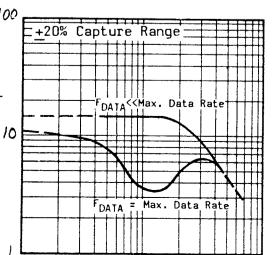

|      | PLL capture range, F <sub>C</sub>                            | C <sub>F</sub> =100 pF, R <sub>F</sub> =0 0hm                                                                               | +40                                     | <u>+</u> 20                   |                             | % min.                                 |

| ١    | PLL lock range, FL                                           | C <sub>F</sub> =100 pF, R <sub>F</sub> =0 0hm                                                                               | <u>+</u> 45                             | <u>+</u> 20                   |                             | a mill.                                |

| 1    | Receiver input sensitivity, S <sub>IN</sub>                  | For a functional receiver (note 8) Referred to chip side (pin 10) of the line-coupling XFMR: F $_0$ =50 kHz F $_0$ =300 kHz | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 10                            |                             | mVRMS<br>mVRMS<br>mVRMS<br>mVRMS       |

| 1    |                                                              | Referred to line side of XFMR: (assuming a 7.07:1 XFMR) $F_0$ =50 kHz $F_0$ =300 kHz                                        | 0.14                                    |                               | 1 1000                      | mV <sub>RMS</sub><br>mV <sub>RMS</sub> |

| 1    | Tolerable input dc voltage offset range, V <sub>TNDC</sub>   | Pin 10 lower than pin 15 by:                                                                                                | 2                                       | 0.1                           |                             | V max.                                 |

| į    | Data Out. breakdown voltage                                  | l<br>  Pin 12, leakage I <u>&lt;</u> 20 µA                                                                                  | 70                                      | 55                            | 1                           | V min                                  |

| į    | Data Out. low output, V <sub>OL</sub>                        | l<br>  Pin 12, sat. voltage at I <sub>OL</sub> =5mA                                                                         | 0.15                                    | 0.4                           | 480                         | V max                                  |

| į    | Time-domain filter current, I                                | <br>  Pin 13 charge and discharge current<br>                                                                               | <u>+</u> 50                             | +35<br>+75                    |                             | µA min<br>µA ma                        |

|      | Offset hold cap. biss voltage, V <sub>CM</sub>               | <br>  Pin 6<br>                                                                                                             | 2.0                                     | 1.3                           |                             | V min<br>V max                         |

| 7    | <br>                                                         | <br>  Pin 6. V(pin 3)-V(pin 4)=+250 mV                                                                                      | +48                                     | +25<br>+80                    |                             | mi Aیر<br>A maر                        |

| 8    | Offset hold bias current, I <sub>OHB</sub>                   | Pin 6, TX mode. Bias pin 6 as it self-<br>  biased during test 32.                                                          | 0.5                                     |                               | (-20)<br>(20)               | กA mi<br>กA ma                         |

| 9    | <br>  Phase comparator current, I <sub>PC</sub>              | Bias pins 3 and 4 at 8.5 V<br>  I <sub>PC</sub> =I(pin 3) + I(pin 4)                                                        | 100                                     | 50<br>150                     |                             | μA ma<br>μA me                         |

| 0    | <br>  Phase detector output resistance,<br>  R <sub>PD</sub> | l Pins 3 and 4.<br>  R <sub>PD</sub> =( <b>V@100</b> μA- <b>V®</b> 50μA)/(50μA)                                             | 10                                      | 6                             |                             | KOhm<br>KOhm                           |

| 1    | 1 '                                                          | Pin 3 to 4, measured after filtering out the 2F <sub>0</sub> component                                                      | 100                                     | 60<br>1 180                   | )<br> <br>                  | m∀pp<br>m∀pp                           |

| 2    | 1                                                            | VPIN3-VPIN4 = +VWINDOW + DC offset<br>Drive for +5 µA pin 6 current                                                         | 0.95                                    | 0.75                          |                             | V/V  <br>  V/V                         |

| 43   | Power supply rejection, PSRR                                 | ار C <sub>L</sub> = 0.1 بال PSRR = CMRR. 120 Hz                                                                             | 80                                      | ļ                             | 1                           | l dBm:                                 |

Note 3: The values inside parenthesis () apply over the full operating temperature range after warmup for the specified supp voltage range. All other numbers apply at  $I_A=I_J=25\,^{\circ}\text{C}$ . Note 4: Guaranteed and 100% production tested. Note 5: Guaranteed (but not 100% production tested) over the temperature and supply voltage ranges. These limits are not use to calculate outgoing quality levels.

Note 6: Total harmonic distortion is measured using IHD=[ $I_{RMS}$ (all components at or above  $2F_0$ )]/[ $I_{RMS}$ (fundamental)].

Note 7: Receiver function is defined as the error-free passage of 2 cycles of 50% duty-cycle 2.4 KHz square-wave data (4 seque tial 208  $\mu$ s bits), with the first bit being a "1." All of the data transitions (edges) must fall within  $\pm 10\%$  ( $\pm 20.6$   $\mu$ s)

that ZUB  $\mu s$  bits), with the first bit being a "1." All of the data transitions (edges) must fall within  $\pm 10\%$  ( $\pm 20.6~\mu s$ ) their noise-free positions. RX time delay is minimized by using no impulse noise filter cap.  $C_1$  for this test. Note B: During the sensitivity check, note 7 requirements are followed with these exceptions: (1) data rate  $F_{DATA}=1.2$  kHz, (all of the data transitions must fall within  $\pm 10\%$  ( $\pm 20.6~\mu s$ ) of their noise-free positions, and (3), a time-domain filt capacitor ( $C_1$ ) is used. The time delay of  $C_1$  is 172 bit, or 208  $\mu s$  ( $C_1$  is approximately 6200 pf). Note 9: For IIL compatibility use a pull-up resistor to increase min.  $V_{OH}$  to above 2.8 V.

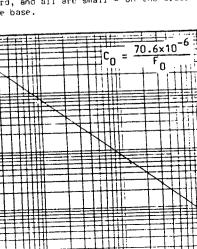

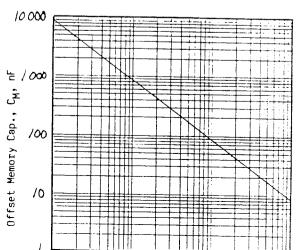

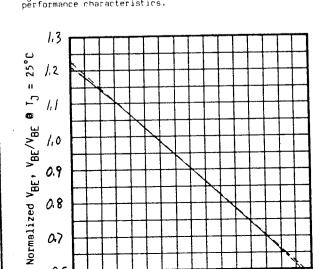

e Transmitter entral to chip operation is the low IC of  $f_0$  emitter-oupled oscillator. With proper  $C_0$ , the  $f_0$  of the VBE amplitude triangle-wave oscillator output may vary from near DC to above 300 KHz. While  $C_0$  may have any value,  $C_0$  should be made above 10 pf so that parasitic capacitance is not dominant. Excessive or unbalanced commun-mode-to-ground capacitance should be avoided. A low temperature coefficient (1C) of capacitance (<100 PPM/°C). temperature coefficient (1C) of capacitance (<100 PPM/°C), such as a monolithic NPO ceramic multilayer type, preserves low TC of  $F_0$ . Figure 6 finds a  $C_0$  value given  $F_0$ . Resistor  $\rm R_{\rm O}$  is used by the IC to generate a  $\rm V_{\rm BF}/R$  related current that is multiplied by 2 to produce the 200 related current

related current that is multiplied by 2 to produce the 200  $\mu A$  ICO centrol current that sets F<sub>0</sub>. The control current IC "bucks" the V<sub>BT</sub> related tri-wave amplitude across C<sub>0</sub> to effect a low IC of F<sub>0</sub>. Vary R<sub>0</sub> to trim F<sub>0</sub>, within limits. Raising F<sub>0</sub> more than 20% above its untrimmed value by means of decreasing R<sub>0</sub> more than 20% is not recommended. Low R<sub>0</sub>, and so high control current, risks ICO saturation and poor IC under worst-case conditions. Raising R<sub>0</sub> reduces the demodulated signal amplitude from the phase detector; raising R<sub>0</sub> by more than a factor of 2 (1 octave) is not recommended. (1 octave) is not recommended.

C<sub>A</sub> and R<sub>A</sub> Components  $C_{A}$  and  $R_{A}$  control the dynamic characteristics of the transmitter output envelope. Their values are not critical. Use the values given in figure 5.  $C_A$  and  $R_A$  are functions of loaded  $I_A$  tank Q,  $F_Q$ ,  $F_{QATA}$ , and line impulse noise. Any changes mode in  $C_A$  and  $C_A$  should be made based on empiracle measurements of a CCI on

Since lower IC pots are relatively costly, it is recommended that  $R_\Omega$  be made up of a 5.6 K fixed (<100 PPM/°C) resistor with a 2 K0hm (<250 PPM/°C) series pot.

the line. Roughly,  $\mathrm{C}_{\mathrm{A}}$  acts as an ALC pole and  $\mathrm{R}_{\mathrm{A}}$  an ALC zero. At this point, the CCI system designer may choose to use one of the recommended transformers or to design  $\rm I_4$  oneself. Consult "The Coupling Transformer" section to help with the design of  $\rm I_4$  if a new or boost-capable transformer is needed. The recommended 125 KHz transformer functions with an  $\rm I_0$  of up to 600 mApp.

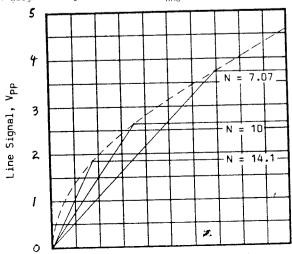

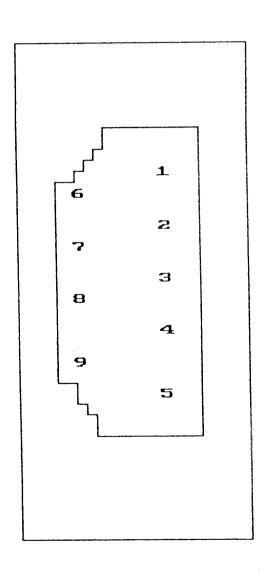

It is recommended that CCT systems use the recommended transformers, described in figure 7, for  $I_1$ . The 3 transformers are optimized for use in the ranges of 50-100 KHz, 100-200 KHz, and 200-400 KHz with unloaded Q's  $(Q_{\parallel})$  of about 35, and loaded Q's  $(Q_{\parallel})$  of about 12. Three secondary taps are supplied with nominal 7.07, 10, and 14.1 turns ratios (N) to drive industrial and residential power line impedances of 3.5, 7, and 14 ohms respectively. All are inexpensive, all have the same pin-outs for easy exchange in a PC board, and all are small - on the order of 10 mm diameter at the base. 100

Oscillator Cap., C<sub>O</sub>, nF

10

al

L = 1' 12  $L' = 20 \times 10^{-9} \left[ \frac{H}{turn} \right]$ (120XA type) 125KHz 707YX-A042YUK  $t = 25 \times 10^{-9} \left[ \frac{H}{T} \right]$ 12VXA type 27 1/2 T 3 4 T, 0.400 µH

18.9 µH

18.9 µH

1 1/2 T, 0.056 µH

5 0.056

707VX-A043YUK

$c_0$

Ըը

3DOKH 2 161XN-A207YUK 10EZ type

FIGURE 7. The recommended T<sub>1</sub> transformers. All are available through Toko America, 5520 W. Touhy Ave., Skokie, IL, 60077, 312-677-3640 (use the part numbers listed above).

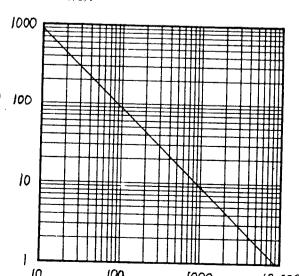

Tank resonant frequency  $F_0$  must be correct to allow passage of transmitter signal to the line. Use figure 8 to find Cg's value. Trimming F0 to equal  $F_0$  is done with  $T_1$ 's trimming slug. The inductance of  $T_1$  has a IC of +150 PPM/°C which may be cancelled by using a -150

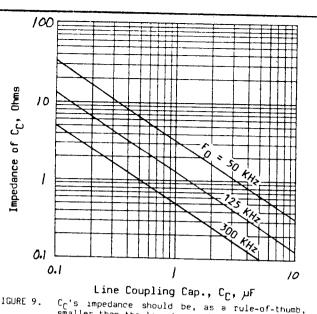

Polypropelene caps. are excellent, "orange drop" mylars are adequate, while many other mylars are inadequate. A 100 V rating is needed for transient protection. Capacitor  $C_C$ 's primary function is to block the power line voltage from  $T_1$ 's line-side winding. Also,  $C_C$  and  $T_1$ 's line-side winding comprise a LC highpass filter. The self-inductance of  $T_1$  is far too low to support a direct line connection.  $C_C$  must have a low enough impedance at  $F_0$  to allow  $T_1$  to drive transmitted energy onto the line. To drive a 14 0hm power line, the impedance of  $C_C$  should be below 14 0hm

PPM/°C cap such as polystyrene. Since circulating current in the tank is 1/4 A<sub>RMS</sub>,  $c_0$  should have a low series resistance (a 1 0hm series resistance is too much).

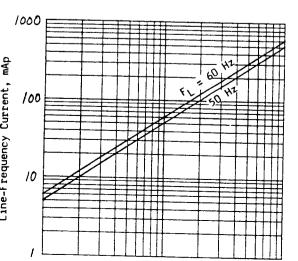

of  $C_{\mathbb{C}}$  should be below 14 0hm. Use figure 9 and 10 to find the reactive impedance of  $\mathbb{C}_{\zeta}$  to check that it is less than the line impedance. Then check to see that the power line current is small enough to keep  $\mathbb{T}_1$  well out of saturation; the recommended transformers can withstand a 10 Amp-turn magnetizing force (1 Ap through the worst-case 10 turn line-side winding). Caution is required when choosing  $\mathbb{C}_{\Gamma}$  to avoid series resonance of the series combination of  $\mathbb{C}_{\Gamma}$ , the transformer inductance, and the reflected tank impedance. The low resistance of the network under series resonance.

will load the line, possibly decreasing range. For you particular line coupling circuit, measure for serie resonance using some expected line impedance load. This base-bleed resistor turns  $Q_B$  off quickly - important since the amplifier output swing is about 200 V/ $\mu s$ . A R<sub>B</sub> below about 24 Dhms will conduct excessive current an overload the chip amplifier and is not recommended.

*50* 000 5000 Resonating Cap., Cg, 500 50 5

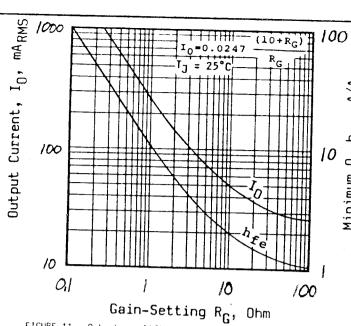

smaller than the lowest expected line impedance. This resistor, in parallel with the internal 10 Ohm

resistor, fixes the current gain of the output amplifier,

output current and minimum AC current gain  $h_{fe}$  for  $Q_{B}$

Figure 11 gives

and so the output current amplitude.

when  $R_{\mathsf{G}}$  is used to boost output current.

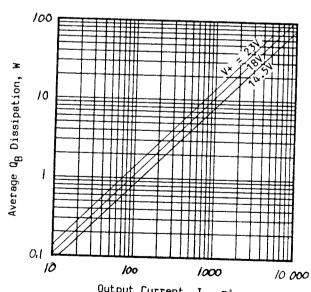

The boost gain transistor  $\Omega_{B}$  must be fast. diffused devices with 50 MHz F $_{T}$ 's work, Doubletransistors (epi-base types) do not preserve a sinusoidal waveform when  $F_0$  is high or oscillate.  $Q_B$  must have a certain minimum  $h_{f_0}$  for given boost levels, as shown in Figure 12 shows the power  $Q_B$  must dissipate  $f_0$  is the power  $f_0$  must dissipate  $f_0$  must dissipate  $f_0$  must dissipate  $f_0$  must dissipate  $f_0$  must  $f_0$  must fcontinuously operating with a shorted output. BV<sub>CER</sub> (R = R) must be 60 V or greater and  $\Omega_{\rm B}$  must have adequate 0.0 A for transient survival.

Unfortunately, potentially damaging transient energy passes through transformer  $I_1$  onto the Carrier I/O pin instantaneous power of greater than 1 KW has been measured using the recommended transformers). For self protection, the Carrier I/O has an internal 44 V voltage clamp with a 20 Ohm series resistance. A parallel low impedance 44 V external transient suppression diode will then conduct the lion's share of any current when transients force the Carrier I/O to a high voltage.

FIGURE 11. Output amplifier current and required min.  $\boldsymbol{\theta}_{B}$  $h_{\mathsf{fe}}$  versus gain-setting resistor  $R_{\mathsf{c}}$  .

$Z_{\mathsf{T}}$  must be used unless some precaution is taken to protect the Carrier 1/0 pin from line transients or transients caused when stored line energy in  $C_{\Gamma}$ discharged by the random phase of power line connection and disconnection. Worst case,  $C_{C}$  may discharge a full peakto-peak line voltage into the tuned circuit. Another way to reduce the need for  $Z_{T}$  is by placing another magnetic circuit in the signal path that relies on a high, but easily saturated, permeability to couple a primary and secondary winding - a toroidal transformer for example Toroids cost more than  $Z_T$ .

Output Current, I<sub>O</sub>, mA<sub>PP</sub> FIGURE 12. Boost transistor power dissipation versus amplifier output current.

Breakdown Voltage Maximum Leakage Capacitance Maximum Clamp Voltage Peak Non-Repetitive Pulse Power (REA Standard Exponential Pulse)

44-49V @ 1mA 1µA @ 40V 300pF & BV 64.5V @ 7.8A 10.2KW for 1us

Use an avalanche diode designed specifically for transient suppression - they have orders of magnitude higher pulse power capability than standard avalanche diodes rated for equal DC dissipation. Metal oxide varistors have not proven useful because of their inferior clamping coefficient. Specifications for an example minimum diode are given in figure 13.

#### The Receiver

The receiver and transmitter share components  $C_{\zeta}$ ,  $T_{1}$ ,  $C_{0}$ ,  $R_{1}$ ,  $Z_{1}$ ,  $C_{0}$ ,  $R_{0}$ , and peripheral supply and bias components that are not in need of change for RX mode Values for the balance of the components are now found

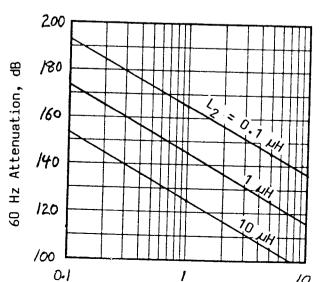

### Line-Frequency Rejection

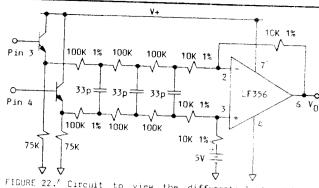

To use the ultimate sensitivity of the device, fully 110 dB of 115 V, 60 Hz attenuation is required between the line and the limiter amplifier output. Using the circuit topology of figure 4, the combined attenuation of the  $C_{\mathbb{C}}/I_1$  highpass, the tuned transformer, and the bandpass filter attenuation of the limiter amplifier give far more

line rejection than the above-stated minimums. However, if some other CCI line coupling circuit is used, line rejection will become important to the system designer. Receiver input power supply rejection (PSRR) and commonmode rejection (CMRR) are one-in-the-same using the supplyreferenced signal input of figure 4. Ripple swings both

differential inputs of the Norton amp. equally, while the single-ended input signal swings only the positive input. Overall PSRR consists of the input CMRR (set by the input stage component matching) attenuation of the input amplifier bandpass response that and the ripple-frequency passes carrier frequency but stops low frequencies. A typical 1% resistor and 1 mV n-p-n mirror offsets give 26 dB of attenuation, the bandpass gives 54 dB 120 Hz attenuation, for an overall 80 dB PSRR to allow tens of volts of ripple before impacting ultimate sensitivity.

$\mathfrak{c}_{\mathbb{C}}$ A value was chosen earlier. Knowing T<sub>1</sub>'s secondary inductance allows a check of LC line attenuation using  $\mathsf{C}^\mathsf{L}$ The Norton input limiter amplifier has a bandpass filter

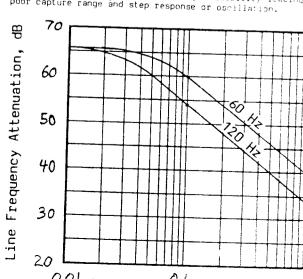

for enhanced receiver selectivity, noise immunity, and line

frequency rejection. The nominal response curve for  $F_0$  = frequency rejection. The nominal response curve for  $r_0$  50 KHz is shown in figure 15. The 300 KHz pole is fixed. The 50 KHz pole is set by  $\mathcal{C}_L$ 's value. After  $\mathcal{C}_L$  is found, the resulting line frequency attenuation is found for the bandpass filter.

Use figure 15 to find a  $\mathbb{C}$ Use figure 15 to find a C value given  $f_{\theta}$ . The approximate line frequency attenuation of the bandpass filter may then be found in figure 16. Figure 15 returns a value for  $\mathcal{C}_{L}$  33% larger than nominal, giving a low frequency pole 33% low to allow for component tolerances.

#### Center Frequency, F<sub>0</sub>, KHz FIGURE 15. Given F<sub>O</sub>, C<sub>t</sub> is found. input amplifier's small Also shown is the signal amplitud-

response.