# Microcontroller Based Analog Signal Tester

#### PROJECT REPORT

Submitted by

E. MALAR

S. SUBATHRA

N. SATHEESH KUMAR

R. BABU

Guided by Mrs. N. KALAIARASI. BE.

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE OF

BACHELOR OF ENGINEERING IN

ELECTRICAL & ELECTRONICS ENGINEERING

OF THE BHARATHIAR UNIVERSITY

DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING

## Kumaraguru College of Technology

COIMBATORE - 641 006.

## DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

## KUMARAGURU COLLEGE OF TECHNOLOGY

**COIMBATORE -641 006**

## **CERTIFICATE**

This is to certify that the report entitled

#### Microcontroller Based Analog Signal Tester

has been submitted by

| 2.25                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mr./Ms. <u> </u>                         | State of the state |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| In partial fulfilment for the            | award of Bachelor of Engineering in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Electrical and Electrical                | onics Engineering Branch of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bharathiar Univers                       | ity, Coimbatore - 641 046. 4/5 (78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| during the ac                            | ademic year 1997/98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\sim$                                   | Dr. K. A. PALANERSMANNE, DEM Solvenger To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 125000                                   | Professor and time:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Guide                                    | Department of Electrical and Decision is togeness of Head of the Department .  Kumaragura College of recomment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | Colembatics 60 (for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Date : > [4] C                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Certified that the candidate was example | mined by us in the project work Viva-Voce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Examination held on                      | and the University Register Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| was                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Internal Examiner                        | External Examiner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **PR-MIER**

#### **CERTIFICATE**

This is to certify that the following students of KUMARAGURU COLLEGE OF TECHNOLOGY, Coimbatore, of Electrical & Electronics Engineering

- E. Malar

- S. Subathra

- N. Satheesh kumar

- R. Babu

had undertaken their project entitled "Microcontroller Based Analog Signal Tester", from September '97 to March '98 at our industry and have successfully completed it.

Their performance during the period was found to be good. We wish them all success.

Place: Coimbatore

Date: 24.03.98

A.G. Raghunath Project Manager

#### **Industry Seal**

Premier Polytronics Limited 304, TRICHY ROAD SINGANALI UR FOST COIMBATORE-641 005.

#### ACKNOWLEDGEMENT

We record our sincere thanks and profound gratitude to our beloved lecturer Mrs.N.KALAIARASI B.E., M.I.S.T.E., who helped and inspired us right from the time of inception to completion of the project.

We are elated to record our heartiest indebtedness to our Professor and Head of the Department of Electrical and Electronics Engineering Dr.K.A.PALANISWAMY M.Sc., (Engg.), Ph.D., M.I.S.T.E., C.Eng.(I), F.I.E., for his valuable help and encouragement during this project.

We have great pleasure in expressing our gratitude to the Principal Dr.S.SUBRAMANIAN M.Sc.,(Engg.), Ph.D., S.M.IEEE...for this valuable encouragement.

We acknowledge with gratitude, M/s PREMIER POLYTRONICS LTD., Coimbatore, for having sponsored our project and providing all the facilities to do the project.

We are thankful to Mr.A.G.RAGHUNATH, PROJECT MANAGER - R&D, Premier Polytronics Ltd., for motivating us to do the project and helping us a lot with constant encouragement.

We are also indebted to Mr.M.DEVENDRAN. ASSITANT ENGINEER - R&D, Premier Polytronics Ltd., for his immense help.

We also wish to acknowledge our sincere thanks to all the **staff members** of the ELECTRICAL AND ELECTRONICS ENGINEERING

DEPARTMENT for their valuable help.

We are very much thankful to our friends for having helped us in many ways during the course of the project.

#### SYNOPSIS

Quality management and market leadership are the primary motto of current industrial scenario. Digital technology has paved way for developing methods to produce elegant products by which quality assurance of products can be guaranteed.

This method of quality assurance is extended to reduce time span and fatigue of workers, as time and energy are two non - renewable resources of mankind.

This project elucidates one such test- jig for the YARN QUALITY MONITOR. Yarn Quality Monitor is a textile machinery which continuously monitors the quality of yarn. This jig is designed and fabricated for L1 module of this Yarn Quality Monitor which collects the data regarding the quality of yarn and test to achieve the required quality.

Our ANALOG SIGNAL TESTER being Microcontroller based uses 80C32 Microcontroller (ROMless Version) and has an efficient software which test this PCB at a high speed.

Thus the commercial Yarn Quality Monitor in large numbers can be easily tested using this Analog Signal Tester.

## **CONTENTS**

PAGE NO.

| CERTIF | ICA | TE                                   |    |

|--------|-----|--------------------------------------|----|

| ACKNO  | WL  | EDGEMENT                             |    |

| SYNOP  | SIS |                                      |    |

| CONTE  | NTS |                                      | ч  |

|        |     |                                      |    |

| CHAPT  | ER- | 1                                    |    |

|        | 1.  | INTRODUCTION                         | ·: |

|        | 1.1 | INTRODUCTION TO YARN QUALITY MONITOR | 2  |

|        | 1.2 | L1 MODULE DESCRIPTION                | 3  |

| CHAPT  | ER- | 2                                    |    |

|        | 2.  | HARDWARE DESCRIPTION                 |    |

|        | 2.1 | 8279 PROGRAMMABLE KEYBOARD DISPLAY   |    |

|        |     | INTERFACE                            |    |

|        | 2.2 | DECODER                              | Ž) |

|        | 2.3 | MICROCONTROLLER                      | 8  |

|        | 2.4 | LATCH                                | ÷. |

|        | 2.5 | EPROM                                | 10 |

|        | 2.6 | STATIC RAM                           | 11 |

|      |      |                               | PAGE NO. |

|------|------|-------------------------------|----------|

|      | 2.7  | VOLTAGE COMPARATOR            | 12       |

|      | 2.8  | WATCH DOG TIMER               | 12       |

|      | 2.9  | DIGITAL CARD                  | 12       |

|      | 2.10 | POWER SUPPLY                  | 13       |

|      | 2.11 | LOGIC DIAGRAM DESCRIPTION     | 13       |

|      | 2.12 | TESTING PROCEDURE             | 14       |

|      |      |                               |          |

| CHAP | TER- | -3                            |          |

|      | 3.   | 8032 DESCRIPTION              | 19       |

|      | 3.1  | INTRODUCTION                  | 19       |

|      | 3.2  | HARDWARE FEATURES OF 8032 CPU | 20       |

|      | 3.3  | INTERRUPTS                    | 24       |

|      | 3.4  | PORT DETAILS                  | 27       |

|      | 3.5  | SERIAL INTERFACE              | 28       |

|      |      |                               |          |

| CHAP | TER- | -4                            |          |

|      | 4.   | DIGITAL CARD DESCRIPTION      | 33       |

|      | 4.1  | INTRODUCTION                  | 33       |

|      | 4.2  | 80C196 DESCRIPTION            | 33       |

|      | 4.3  | SERIAL PORT                   | 37       |

|      | 11   | A/D CONVERTER                 | 38       |

|         |                               | PAGE NO. |

|---------|-------------------------------|----------|

| 4.5     | EXTERNAL MEMORY               | 39       |

| 4.6     | GAIN LATCHES                  | 39       |

| 4.7     | 7 DIGITAL TO ANALOG CONVERTER | 49       |

|         |                               |          |

| CHAPTER | R-5                           |          |

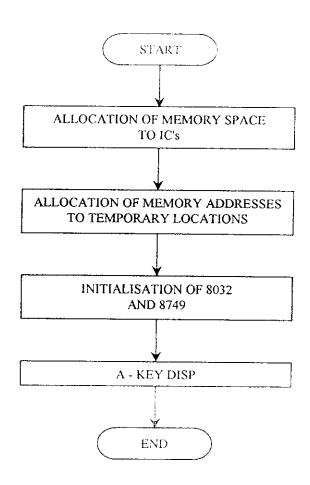

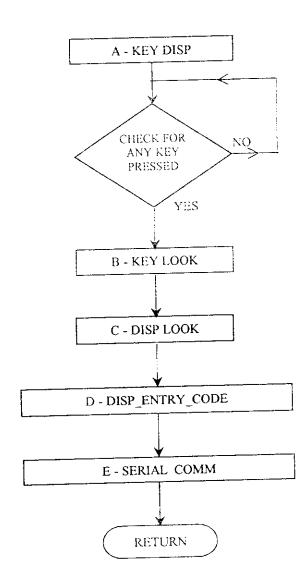

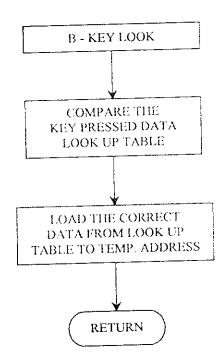

| 5.      | SOFTWARE                      | 42       |

| 5.1     | 1 ALGORITHM                   | 42       |

| 5.2     | 2 FLOW CHART                  | 44       |

| 5.3     | 3 PROGRAM                     | 50       |

|         |                               |          |

| CHAPTE  | R-6                           |          |

| 6.      | CONCLUSION                    | 62       |

|         |                               |          |

| REFERE  | NCES                          |          |

| APPEND  | IX .                          |          |

.

#### **CHAPTER-1**

#### 1.INTRODUCTION

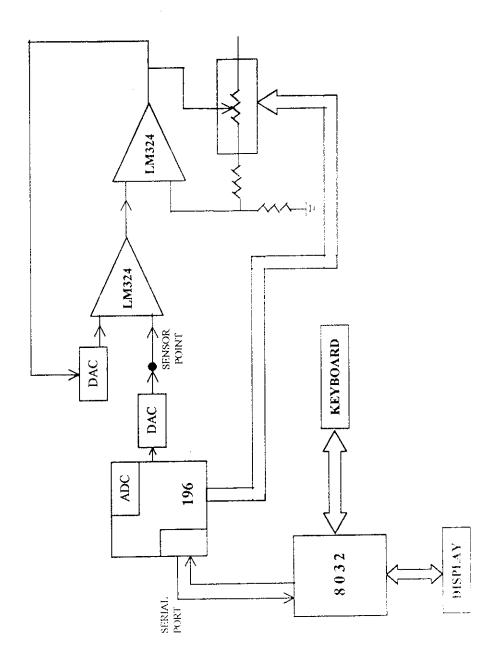

ANALOG SIGNAL TESTER is basically a testing instrument. This is used to test the PCB of the YARN QUALITY MONITOR. The PCB to be tested has eight similar channels. Hence a testing equipment designed for one channel can be used for all eight modules. The modules to be tested is selected using the corresponding latch.

This system consist of electronic circuits like keyboard display interface, decoder, latch etc., microcontroller and a keyboard display card. Through the keyboard the input parameters such as voltage, gain and the channel to be tested are fed in. The keyboard display interface feeds the data to the digital card through 8032 microcontroller.

The digital card which is used for serial communication receives the data, selects the channel to be tested and sets the voltage and gain correspondingly. The output signal from the PCB is verified and the result is displayed accordingly.

## 1.1INTRODUCTION TO YARN QUALITY MONITOR

The process of yarn making consists of converting a stock of fibre into yarn. During conversion forming a long strand of aligned fibres is called as SLIVER. Sliver is twisted to form yarn.

This Yarn Quality Monitor is placed in the stage of conversion of sliver to yarn. This is used to monitor the quality of the yarn.

Yarn Quality Monitor consists of the following four modules.

- 1. L0 Module

- 2. L1 Module

- 3. L2 Module

- 4. L3 Module

#### LO MODULE:

L0 Module is a sensor module. It consists of capacitive sensors to sense the quality of the yarn.

#### L1 MODULE:

L1 Module does the data collection and processing. It collects the output of the L0 Module as data and processes it.

#### L2 MODULE:

L2 Module displays the processed output of L1 Module. The quality of the yarn is displayed at various instants.

#### L3 MODULE:

L3 Module is used to interface the yarn quality monitor to personal computer. A personal computer can control 15 such yarn quality monitors.

Out of this four Modules the complete processing of the data is done by L1 Module. Hence this plays a vital role in determining the quality of the yarn. Failure of any components in this Module leads to drastic errors. To eradicate this problem the performance of this Module has to be tested initially.

#### 1.2 L1 MODULE DESCRIPTION:

This module has eight similar channels of analog circuits. A single channel can be divided in to the following three stages.

- 1. Offset Null Stage

- 2. Gain Stage

- 3. Clipper Stage

#### **OFFSET NULL STAGE:**

It consists of an opamp operating in differential mode. In differential mode the output of opamp is the difference of the two input signals. The inputs to the opamp are from a sensor and a DAC.

In any opamp the output offset voltage is the voltage at the output with no input signals applied. If this is not nullified, this gets added up with the actual output.

To nullify the output offset voltage following procedure is adopted.

- The output of the opamp is read with the input points grounded i.e.,

the input from the sensor and DAC is grounded.

- The DAC is set to the value of the output obtained. By this the accumulation of error voltage is eliminated.

#### **GAIN STAGE:**

This stage amplifies the output signal of the offset null stage. As the input from the sensor is in the range of millivolts, any change in the yarn quality cannot be determined accurately. Therefore this weak signal should be amplified appropriately. Gain for which the signals should be can be varied by the user, through microcontroller and latches.

#### **CLIPPER STAGE:**

Microcontroller can read only the signals of voltage ranging from 0 - 5V. Any signal beyond this limit is excluded. To avoid this, any signal which is below 0V is grounded through diode D1 and the signals above 5V is directed to Vref through diode D2. Thus only the signals from 0 - 5V is allowed to enter microcontroller. The circuit diagram of the L1 module is shown in figure 1.1.

HOLD BLOCK DIACRAM OF LI MODULE

#### CHAPTER - 2

#### HARDWARE DESCRIPTION

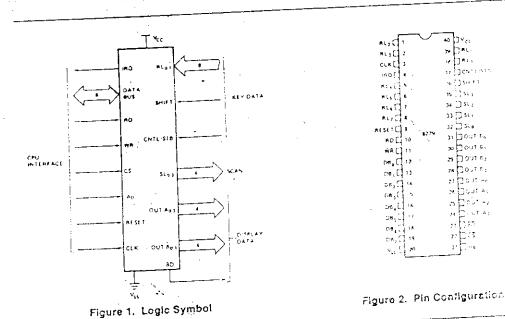

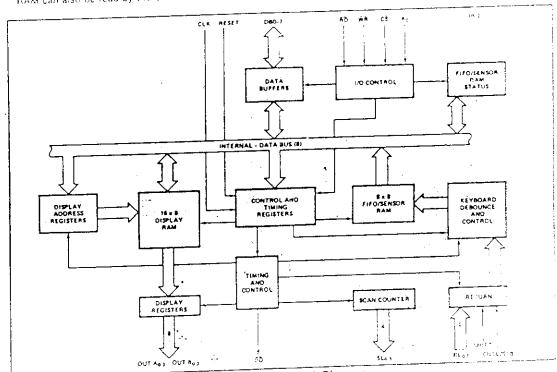

## 2.1 THE 8279 PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE:

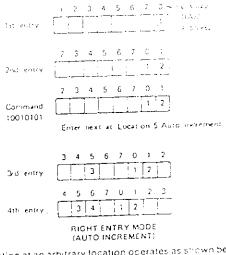

It is a keyboard display interface. It is used to interface the keyboard and seven segment display to 8032. The keyboard segment of 8279 can be connected to a 16-contact key matrix through scan and return lines. The channel to be tested, voltage and the gain are fed in through the keyboard in the following format.

| С | X1 | G | X2 | V | Х3       |

|---|----|---|----|---|----------|

|   |    |   |    |   | <u> </u> |

C : Channel

X1 : Numbers from 0 - 7 (Channel number)

G : Gain

X2 : Numerical value of gain

V : Voltage

X3 : Numerical value of voltage.

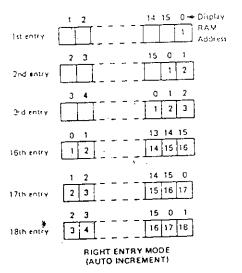

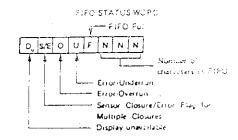

This data is stored in the FIFO RAM of 8279 to be read by 8032. The output data to be displayed from microcontroller is stored in display RAM. This is then displayed in the six character, seven segment display.

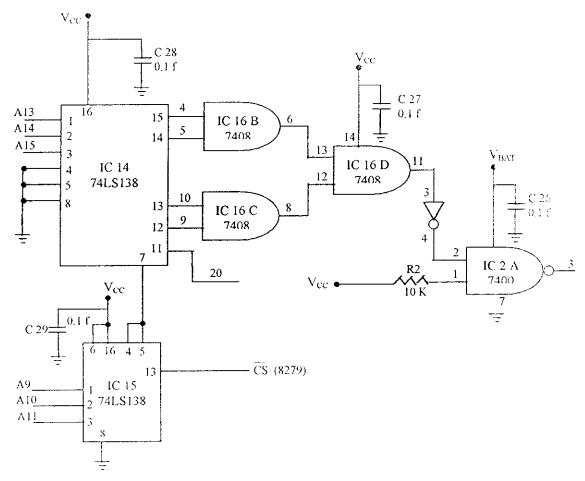

#### 2.2 DECODER [74LS138]:

This is a 3-8 bit decoder. This is employed in interfacing the Keyboard Display interface (8279) with 80C32. The decoder is a logic circuit that identifies each combination of the signals present at its input. The 74LS138 has three input lines and eight active low output lines. It requires three enable inputs. Two are active low and one is active high. All three enable lines should be activated so that the device can function as a decoder. The address lines A13, A14, A15 of the microcontroller are the input lines to the decoder1. The memory map of RAM ranges from 0000H to 7FFFH. For various combinations of A13, A14 and A15 the RAM is selected. The decoder circuit diagram is shown in fig 2.3.

Decoder2 is used to select 8279. The address lines A9, A10, A11 are used as input lines. The memory map of 8279 ranges from E400H to E5FFH. The output of the decoder is connected to the chip select pins of RAM and 8279. When chip select is low, the output lines go into the high impedance state. Then the 8279 or RAM is activated.

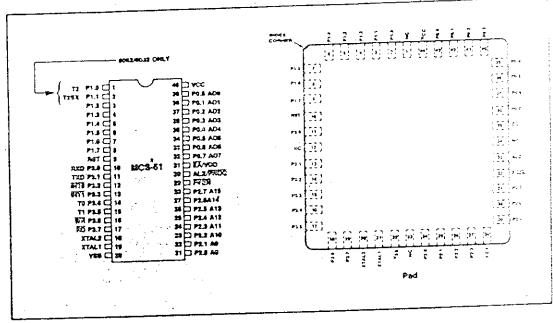

## 2.3 MICROCONTROLLER [ 80C32 ]:

The purpose of this chip is to execute the users program instruction by executing a series of its microinstructions there by controlling data transfer and all functions from computed results.

The microcontroller has two 16 bit timers. The timers are versatile and can be used for A/D conversion, pulse width measurement and frequency counting. They can also act as counters. Signa pulses from transducers like phototransistors could be conventionally counted. The UART in 8032 enables it to transmit and receive serial data from other devices like CRT terminal, computer and printer. Two interrupts are allowed from external sources. There is a free I/O port available in 8032 in addition to three other ports. But 8032 uses these ports for external memory since it has no in-built EPROM or ROM. Nevertheless it saves a lot of hardware. Moreover any bit of a port can be read by the software or toggled or processed.

The microcontroller serves as a bit processor, because it has instructions to deal with a bit and thus can do Boolean logic functions more conveniently. The 8032 has a low power mode in which its internal RAM and registers can be retained with low battery power.

## 2.4 LATCH [ 74LS573 ] :

The latch is employed to demultiplex the address/data iines. During transfer of data from memory to the controller, the higher order address remains on the bus. However the lower order address bits will be lost after the first T-state. Hence the need for address to be latched and used for identifying the memory address. When the ALE goes high, the

latch is transparent i.e., the output changes according to the input. When ALE is low, the lower order address is latched until the next ALE and the output of the latch represents the lower order address bus (A0-A7) after the latching operation.

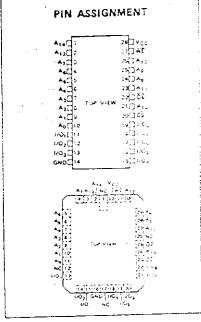

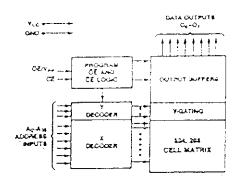

#### 2.5 EPROM [ 27512 ]:

Erasable programmable read only memory is a type of memory which can be reprogrammed again and again simply by erasing it subjecting it to ultraviolet rays.

#### Programming the EPROM:

The programming tool used for loading the EPROM is PC-UPROG.UPROG system is designed with 40 pin socket that supports most devices. PC-UPROG is a convenient programming tool for all kinds of programmable devices. PC-UPROG uses the popular IBM and IBM compatible desk top computer as its host system for data and algorithm storage while actual programming is under control of the hardware pulse generators and D/A converter of the PC-UPROG system. PC-UPROG is very user friendly, no special knowledge of programmable devices are required. All the operations are menu driven and displayed in clear, easy to understand English text.

#### **Erasing the EPROM:**

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelengths shorter than approximately 4000 Angstroms. Since sunlight and fluorescent have wavelengths in this range, exposure to these light sources over an extended time ( about 1 week in sunlight, or 3 years in room level fluorescent light ) could cause inadvertent erasure. If an application subjects the device of this type of exposure, it is suggested that an opaque label be placed over the window.

The recommended erasure procedure is exposure to ultraviolet light (at 2537Angstroms) to an integrated dose of atleast 15WSecs/sq.cm. Exposing the EPROM to an ultraviolet lamp of 12,000 mW/sq.cm rating for 20 to 30mins, at a distance of about 1 inch, should be sufficient. Erasure leaves the array in all 1's state.

## 2.6 STATIC RAM [ MCM 62256 / 63256 ] :

It is a read-write memory i.e., a static RAM. A static RAM is essentially a matrix of flipflops. Therefore one can write a new data word in RAM location at any time by applying the word to the flipflop data inputs. Here the EPROM and RAM are employed as external memory to the controller.

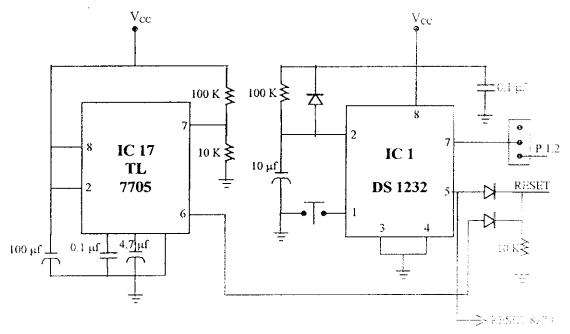

#### 2.7 VOLTAGE COMPARATOR [7705]:

Voltage comparator is used to protect the controller from over voltage and under voltage levels of the supply voltage. The comparator monitors the supply voltage and compares it with a reference. If the voltage drops or rises above  $V_{\text{ref}}$ , then a hardware reset will be initiated.

#### 2.8 WATCH DOG TIMER:

Watch dog timer is a missing pulse detector. It provides a means to recover from a software upset. When the watch dog timer is enabled, it will initiate a hardware reset. So the software should clear it every 64K state times. The clearing pulses are monitored. If the pulses are missed until the gets overflowed, it pulls down the reset pin resetting the 8032 and all other devices tied to the reset line.

#### 2.9 DIGITAL CARD:

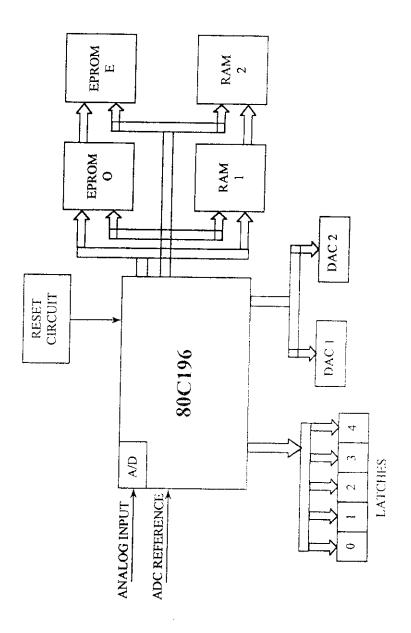

This card consists of 80C196 microcontroller, DACs, latches, RAMs and EPROMs. The latches used here to set gain for the channel to be tested. The DACs are used to convert the digital input from 3032 to analog signal. RAMs and EPROMs are used as external memories for 80C196. 80C196 is operated in mode 1,(i.e) asynchronous mode. This digital card serves as serial communication port between 8032 card and the PCB to be tested.

#### 2.10 POWER SUPPLY:

The power supply for all IC's is given from the +5V of the regulated supply. These IC's can tolerate the fluctuations within certain limits. These limits are fixed by the voltage monitoring IC. The power supply diagram is shown in fig 2.2.

#### 2.11 Logic Diagram Description:

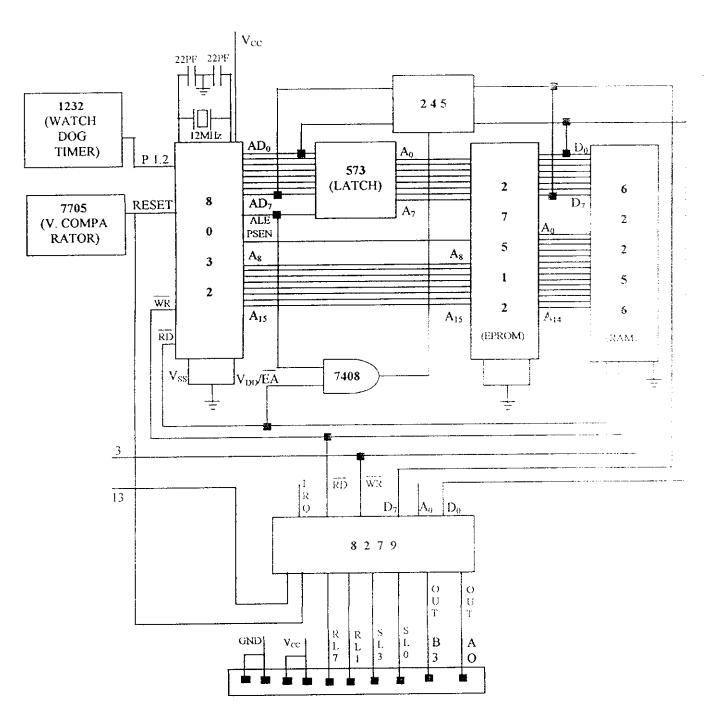

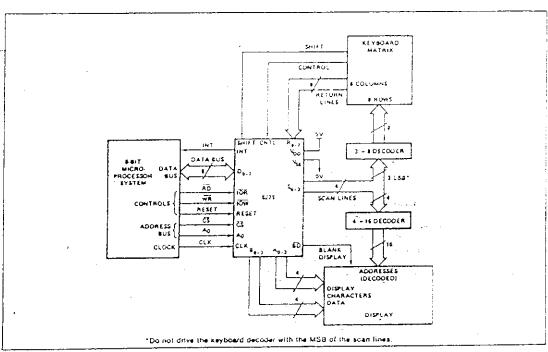

The circuit designed is to interface the keyboard and display unit with that of the digital card. The operation of interfacing is Microcontroller based. 80C32 Microcontroller is used for this purpose.

80C32 has only 128 bytes of data memory on chip and it has no program memory. But 80C32 can address 64 KB of RAM and 34 KB of program memory (EPROM) externally. The program to be executed is loaded in 27512 EPROM, as it has 64 KB of memory. For temperary data storage we need 32 KB of RAM. This is done by 63256 RAM.

8279 keyboard display interface is used to interface keyboard display card with that of 80C32 Microcontroller. 74LS573 3-8 8 bit decoders are used to select 63256 (RAM) and 8279 chips. The active low chip select line to the EPROM is grounded to make it available always.

The data and address lines are shared by different chips. The lower order address lines and data lines are multiplexed. For this purpose a tatch is used. An octal bidirectional transceiver or buffer (74LS245) is used as temporary storage of data. Since bidirectional it can transfer data from Microcontroller to EPROM or RAM or vice versa.

Chip 1232 is used to reset the hardware externally. Supply to all the chips is provided using a 7705 voltage comparator. This provides 5 V of supply. Connector pins are provided to interface this board with keyboard display card and digital card.

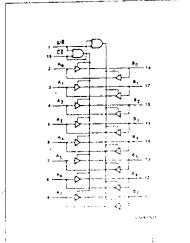

The keyboard used here is 4 X 4 matrix keyboard. Six characters can be displayed using seven segment display. The PCB for this circuit is designed and fabricated. The logic diagram is shown in fig.2.1.

#### 2.12 TESTING PROCEDURE:

The PCB to be tested is interfaced with the digital card and 80C32 microcontroller board. The channel to be selected the testing voltage and the gain are fed as inputs through the keyboard display care which is directly linked to the 80C32 board. The 8279 keyboard display interface scans the keyed in data and stores in FIFO RAM temporarily. This data is transferred to 80C32 microcontroller which then passes this

data to digital card through serial communication port. The entire program to perform this process is loaded in the EPROM. RAM is used for temporary storage of datas during processing.

The digital board receives the input data through the serial I/O port. Then the digital card selects the particular channel and sets the testing voltage and gain. The gain settings are done through the gain latches in the digital board. The DAC feeds the voltage to be set to the non-inverting terminal of the OP-AMP in the PCB which is to be tested.

The output voltage from the PCB is fed to the digital card. This analog signal is converted into digital by the inbuilt analog to digital converter in 80C196 microcontroller. This microcontroller checks whether the output is corresponding to the input. Based on the performance it then transmits the result to the 80C32 microcontroller through serial I/O port. The data received is in the form of ASCII code which is then converted into display code by the microcontroller. The output whether the channel works or not is displayed in the keyboard display card.

Hence a particular channel in the PCB can be tested as per above procedure. The next channel can be selected and tested successively.

The general block diagram is shown in fig.2.4.

FIG 2.1 LOGIC DIAGRAM

FIG 2.2 POWER CIRCUIT DIAGRAM

FIG 2.3 DECODER CIRCUIT DIAGRAM

۴.

#### **CHAPTER - 3**

#### 8032 DESCRIPTION

#### 3.1 INTRODUCTION:

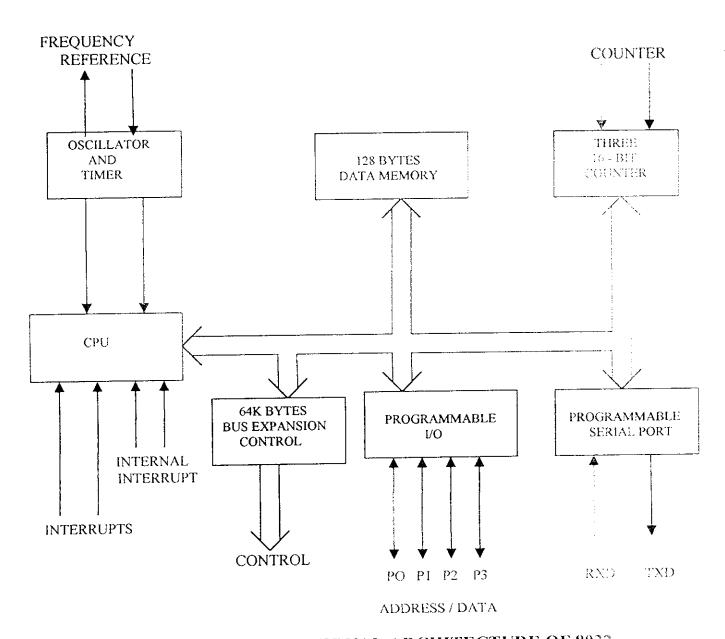

SUPPLY

Single 5V operation with power down mode for

saving internal RAM memory.

INTERNAL MEMORY 128 bytes of register memory on chip, four banks of

eight registers have special functions, two registers

have additional indexing capability in each bank .

MEMORY

64 KB program memory, switchable in 4K banks.

64 KB data memory, fully addressable.

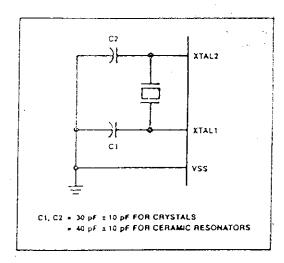

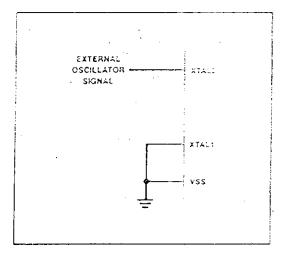

CLOCK TIME

1 microsecond instruction cycle time with 12MHZ

crystal. Two external interrupts, two level priority,

level or edge triggerable, two timer interrupts,

one UART interrupt.

**PORTS**

One 8-bit I/O port, bit addressable, one UART port

high speed programmable, two counter inputs could

be used for gating timers or counters. Two multimode 16bit (8bit) timers/counters.

ALU

Binary or decimal arithmetic, Boolean bit for control logic programs, hardware 8-bit multiply and divide in 4 microsecs, parity computation, overflow detection.

The block diagram is shown in the fig. 3.1

#### 3.2 HARDWARE FEATURES OF 8032 CPU:

#### REGISTERS:

Registers are small memories within the CPU. Registers are one part of control section. Like memory storage units, they consist of sinary cells and have address that distinguish them. The number of registers is very small however, data may be saved in a register until the program requires it. The registers are distinguished as follows:

#### **ACCUMULATOR:**

The accumulator is a eight bit register that is a part of the arithmetic logic unit (ALU). This register is the focus of all accumulator instructions that include arithmetic, logic, store and I/O instructions.

The result of an operation is also stored in the accumulator which is also identified as register A.

#### PROGRAM COUNTER (PC):

The register is a memory pointer. Memory locations have sixteen bit address. The microcontroller uses this register to sequence the execution of instructions. The microcontroller uses this register to sequence the execution of instructions. The function of the program counter is to point to the memory address from which the next byte has to be fetched. When a byte is being fetched the program counter is incremented by one point to the next memory location. The 8032 program counter is 16 - bits wide and can access upto 64KB of program or data memory.

#### FLAG REGISTER:

The processor flags are combined in one status word (PSM)

| CY AC FO RS1 RS0 OV X P | D7 | D6 | D5 | D4  | D3  | D2 | D1 | D0 |  |

|-------------------------|----|----|----|-----|-----|----|----|----|--|

|                         | CY | AC | FO | RS1 | RS0 | OV | Х  | Р  |  |

CY: Carry flag

AC : Auxiliary carry flag

F0: Indicator

RS1 : Register bank

RS0 : Register bank

OV : Overflow flag

X : Don't care

Parity flag

#### STACK POINTER (SP):

The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory location in the R/W memory, called the stack which is defined by loading a sixteen bit address in the stack pointer. The stack is also within the RAM only. The stack pointer points to the location where the stack operations has to be done. Stack fills upward from there. Reset defaults the stack pointer to 08, pushing and popping of register / memory location can be done with one byte of instruction.

#### **SERIAL DATA BUFFER:**

The serial data buffer is actually two separate registers. When data is moved to SBUF, it goes to the transmit buffer where it is held for serial transmission (Moving a byte to SBUF is what initiates transmission). When data is moved from SBUF, it comes from the receive buffer. During serial reception the incoming bits are clocked into a separate shift register. When reception of a frame is complete and if various other conditions are satisfied, received data bits are transferred from the shift register to the receive buffer. The shift register is then ready to commence reception of a second frame, while the frame already received awaits servicing.

#### **CONTROL AND STATUS REGISTERS:**

Special Function Registers IP(Interrupt Priority). IE(Interrupt Enable), TMOD(Timer / Counter Mode), TCON(Timer / Counter Control), SCON(Serial Control) and PCON(Power Control) contain control and status bits for the interrupt system, the timers and the serial port.

#### STACK:

Data is pushed in to the stack or popped out of the stack on the LIFO basis. The stack can be located anywhere in the RAM memory. The stack pointer maintains the address of the last byte entered into the stack and is decremented everytime data is pushed into the stack and incremented each time data is popped out of the stack. The stack pointer is always incremented or decremented by two bytes.

#### **ARITHMETIC LOGIC UNIT:**

The ALU consists of the accumulator, the flag register and some temporary register that are accessible to the user. Arithmetic, logic and rotate operations are performed by the ALU.

#### INTERNAL TIMERS / COUNTERS:

There are two timers, timer1 and timer0. Actually, two 16-bit registers are used, which incremented one by one, either by a tick of the timer clock or by a count pulse at pins T0 and T1. If a 12MHz crystal is

used, each tick is one microsecond. Thus a timer register can fill up to 65536 clock ticks. Longer time delays can be arranged by using the timer repeatedly in a software loop. As a counter, the same could accumulate pulses at frequencies from DC to 500MHz, with 16-bit precision. The timer could be operated in four modes.

#### 3.3 INTERRUPTS:

The 8032 provides five interrupt sources, each of which can be programmed to one of the two priority levels. The five interrupt sources are listed below.

| Source      | Description                                      |

|-------------|--------------------------------------------------|

| INT O       | External request from P3.2 pin.                  |

| Timer 0     | Overflow request Timer 0 activates interrupt     |

|             | request flag TF0                                 |

| INT 1       | External request from P3.3 pin.                  |

| Timer 1     | Overflow from Timer 1 activates interrupt        |

|             | request flag TF1.                                |

| Serial Port | Completion of transmission or reception of       |

|             | one serial frame activates request flag TI or RI |

|             | respectively.                                    |

Each source can be individually enabled or disabled by setting or clearing a bit in special function register IE.

IE:

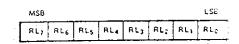

MSB LSB

| EA | Х | Х | ES | ET1 | EX1 | ET0 | EX0 |  |

|----|---|---|----|-----|-----|-----|-----|--|

|    |   |   |    |     |     |     | L   |  |

EA : Enable all.

ES : Enable serial port control bit.

ET0, ET1 : Enable timer 0 and timer 1 control bit

EX0, EX1 : Enable external interrupts 0 or 1

Since there is more than one interrupt, priority is given to them.

Set or clear five bits of the IP register to make the priority high or low respectively.

IP:

MSB LSB

| ſ |      |             | PS | PT1 | PX1 | PT0 | PX0 | 1 |

|---|------|-------------|----|-----|-----|-----|-----|---|

|   | <br> | <del></del> |    |     |     |     |     |   |

PS : Serial port priority control bit.

PT0, PT1 : Timer interrupts

PX0, PX1 : External interrupts

Each interrupt has a vector address to which the program branches. In the monitor program, long jump instructions are given to take the interrupt service routines at the addresses given below:

| Source               | Address |

|----------------------|---------|

| External Interrupt   | 0003H   |

| Timer 0 Overflow     | 000BH   |

| External Interrupt 1 | 0013H   |

| Timer 1 Overflow     | 001BH   |

| Serial Port          | 0023H   |

Execution proceeds from that address until the RET1 instruction is encountered.

#### 3.4 PORT DETAILS:

#### PORT 0:

Port 0 is a 8 bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in that state can be used as night impedance inputs. Port 0 is also the multiplexed low order address and data bus during access to external program and data memory. Port 0 also receives the code bytes during programming the EPROM parts, and outputs the code bytes during program verification of the ROM and EPROM parts. External pull-ups are required during program verification.

#### PORT 1:

Port 1 is an 8-bit bi-directional I/O port with external pull-ups. The port 1 output can sink /source 4 LS TTL inputs. Port 1 pins have 1's written to them are pulled high by the external pull-ups and that state can be used as inputs. As inputs, port 1 pins that are externally being pulled low will source current because of the internal pull-ups.

#### PORT 2:

Port 2 is an 8-bit bi-directional I/O port with internal pull-up. The port 2 output buffers can sink/source 4 LS TTL inputs. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and in that state can be used as inputs. Port 2 also receives the higher order address bits during programming of the EPROM parts and during program verification of the EPROM parts. Port 2 emits the higher order address byte during access to external data memory that use 16-bit address.

#### PORT 3:

Port 3 is a 8-bit bi-directional I/O port with internal pull-up. The port 3 output buffers can sink /source 4 LS TTL inputs. Port 3 pins that have 1's written to them are pulled high by the internal pull-ups, and in that state it can be used as inputs. Port 3 pins that are externally being pulled low will source current because of the pull-ups. Port 3 also serves the functions of various special features of the 8032 as listed below

| PORT PIN | ALTERNATIVE FUNCTION           |

|----------|--------------------------------|

| P 3.0    | RXD (Serial input port)        |

| P 3.1    | TXD (Serial output port)       |

| P 3.2    | INT0 (External interrupt 0)    |

| P 3.3    | INT1 (External interrupt 1)    |

| P 3.4    | T0 (Timer 0 external input)    |

| P 3.5    | T1 (Timer 1 external input)    |

| P 3.6    | WR (External data memory write |

|          | strobe)                        |

| P 3.7    | RD (External data mmeory read  |

|          | strobe)                        |

## 3.5 SERIAL INTERFACE:

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the receive register. The serial port registers are both accessed at Special Function Register serial buffer (SBUF). A write to SBUF loads the transmit register and a read access a physically separate receive register.

The serial port can operate in 4 modes as follows:

- MODE 0: Serial data enters and exits through RXD. TXD outputs the shift clock. 8-bits are transmitted / received : 8 data bits (LSB first).

The baud rate is fixed at 1/12 the oscillator frequency.

- MODE 1: 10 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), and a stop bit(1). On receive, the stop bit goes into RB8 in Special Function Register SCON. The baud rate is variable.

- MODE 2: 11 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (1). On transmit, the 9<sup>th</sup> data bit (TB8) can be assigned the value of 0 or 1. With nominal software overhead, TB8 can be made a parity bit. On receive, the 9<sup>th</sup> data bit goes into RB8 in Special Function Register SCON, and the stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency.

- MODE 3: 11 bits are transmitted (through TXD) or received (through RXD):a start bit (0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (1).

#### **SERIAL PORT CONTROL REGISTER:**

Special Function Register SCON is used to define the operating modes and control certain functions of the serial port. It also receives the 9<sup>th</sup> data bit (RB8), and contains the transmit and receive interrupt flags (Ti and RI). The register is as shown below:

| 7   | 6   | 5   | 4   | 3   | 2   | 1  |    |

|-----|-----|-----|-----|-----|-----|----|----|

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | T1 | R1 |

Where SM0 and SM1 specify the port mode, as follows:

| SM1 | SM1 | Mode | Description    | Baud rate   |

|-----|-----|------|----------------|-------------|

| 0   | 0   | 0    | shift register | f osc. / 12 |

| 0   | 1   | 1    | 8-bit UART     | variable    |

| 1   | 0   | 2    | 9-bit UART     | f osc. / 64 |

|     |     |      |                | 0.7         |

|     |     |      |                | f osc. / 32 |

| 1   | 1   | 3    | 9-bit UART     | variable    |

- SM2 enables the multiprocessor communication feature in modes 2 and 3.

- REN enables serial reception.

- TB8 is the 9<sup>th</sup> data bit that will be transmitted in modes 2 and 3.

- RB8 in modes 2 and 3, is the 9<sup>th</sup> data bit that was received.

- TI is transmit interrupt flag.

- RI is receive interrupt flag.

FIG 3.1 INTERNAL ARCHITECTURE OF 8032

## CHAPTER - 4

## DIGITAL CARD DESCRIPTION

#### 4.1 INTRODUCTION:

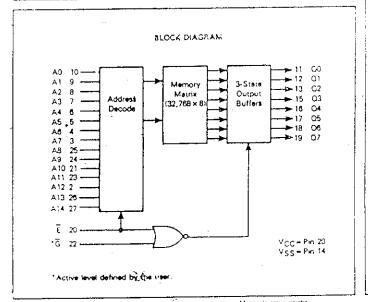

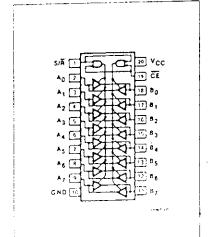

The Digital card used for serial communication is previously used by the industry for the same purpose. The main part of the digital card is a 80C196 microcontroller supported by two EPROMs (odd and even), two RAMs and gain latches.

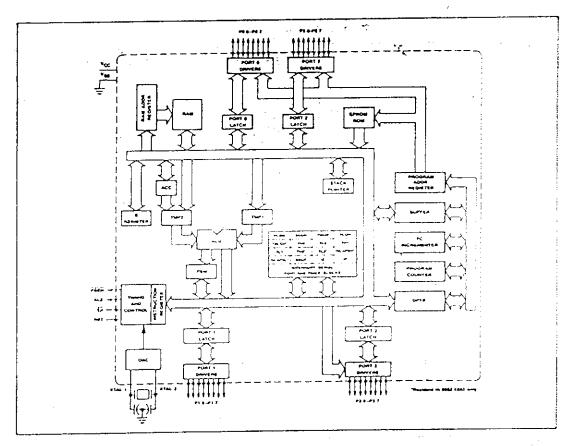

#### 4.2 80C196 DESCRIPTION:

The 80C196 is a 16-bit microcontroller. There are five peripherals on the 80C196KB: The Pulse Width Modulated output (PWM), timers, high speed I/O units, serial port and A/D converter. Out of the five peripherals serial port and A/D converter are used here.

SUPPLY Single 5V operation with power down mode for saving internal RAM memory.

MEMORY SPACE 64K Bytes of memory space is available for program or data memory. Locations 0000H through 90FFH and 1FFFH through 2080H are used for special purposes. All other locations can be used for either

program or data storage or for memory mapped peripherals.

INTERNAL TIMING Internal operation of the 80C196 KB is based on the crystal or external oscillator frequency divided by 2

.Every 2 oscillator periods is referred to as a state time, the basic time measurement for all 80C196 KB.

With a 12MHZ oscillator the state time is 167 ns.

**PORTS**

Five 8-bit I/O ports. Port0 is an input port also used as analog input for A/D convertor. Port1 and Port2 are quasi-bidirectional, input and output ports. Port3 and Port4 are open drain bidirectional ports.

RALU

Most calculations performed by 80C196 takes place in RALU. The RALU contains a 17-bit ALL, the program status word (PSW), the program counter (PC), a loop counter and three temporary registers. All of these registers are 16-bit or 17-bit wide. Some of the registers have the ability to perform simple operations to off-load the ALU.

The internal architecture of 80C196 microcontroller is shown in Fig. 4.1

#### SYSTEM BUS:

There are several modes of system bus operation on the 80C196KB. The standard bus mode uses a 16-bit multiplexed address/data bus. Other bus modes include an 8-bit mode and a mode in which the bus size can dynamically be switched between 8- bits and 16-bits.

#### PROGRAM STATUS WORD:

PSW is a collection of Boolean flag which retain information concerning the state of the user's program. There are 2 bytes in the PSW: the actual status word and the low byte of the interrupt mask. PSW can be saved in the system stack with a single instruction PUSH F and restore in a POP F instruction. Only the interrupt section of the PSW can be accessed directly. There is no SFR for the PSW status bits.

| MSB |   |               |    |   |   |   | LSB |  |  |

|-----|---|---------------|----|---|---|---|-----|--|--|

| Z   | N | V             | VT | С | Х | I | ST  |  |  |

| Z   |   | Zero fla      | g  |   |   |   |     |  |  |

| N   |   | Negative flag |    |   |   |   |     |  |  |

V Overflow flag

VT Overflow trap flag

C Carry flag

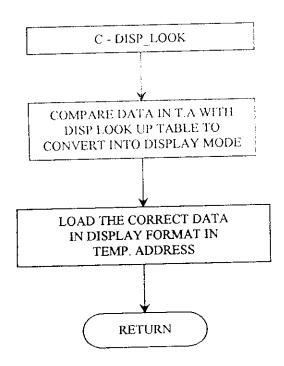

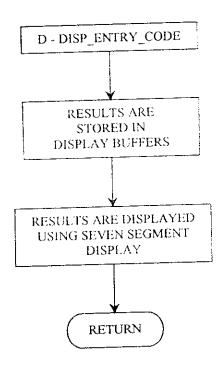

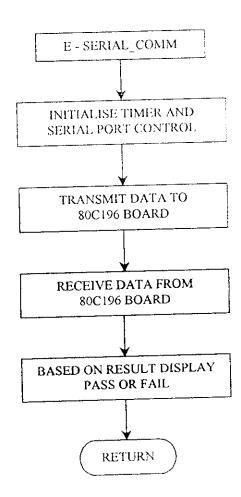

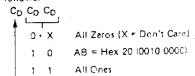

X Reserved