## ANTI-COLLISION SYSTEM IN TRAINS USING RFID

### By

**DANNY GEORGE**

**GAUTAM SUNDER**

M.GOWRI SHANKAR

S.V.YUVARAJ

Reg No: 0710107016

Reg No: 0710107029

Reg No: 0710107305

Reg No: 0710107308

of

## KUMARAGURU COLLEGE OF TECHNOLOGY, COIMBATORE - 641 049.

(An Autonomous Institution affiliated to Anna University of Technology, Coimbatore)

## A PROJECT REPORT

Submitted to the

# FACULTY OF ELECTRONICS AND COMMUNICATION ENGINEERING

In partial fulfillment of the requirements for the award of the degree

of

BACHELOR OF ENGINEERING

in

**ELECTRONICS AND COMMUNICATION ENGINEERING**

## BONAFIDE CERTIFICATE

This is to be certified that this project report "ANTI-COLLISION SYSTEM IN TRAINS USING RFID" is the bonafide work of "DANNY GEORGE, GAUTAM SUNDER, M.GOWRI SHANKAR, and YUVARAJ.S.V" who carried out the project work under my supervision.

Dr.(Mrs).Rajeswari Mariappan

Head of the Department

Department of Electronics and

Communication Engineering,

Kumaraguru College of Technology

Coimbatore.

4 Mutholan **SIGNATURE**

Ms.G.Amirtha Gowri

**Project Guide**

Department of Electronics and

Communication Engineering,

Kumaraguru College of Technology

Coimbatore.

The candidates with University Register numbers 0710107016, 0710107029, 0710107305, 0710107308 were examined by us in the Project Viva voce Examination held on \_\_\_\_\_\_ 19th April, 2011

## **ACKNOWLEDGEMENT**

We extend our heartfelt gratitude towards our revered chairman Arutselvar Dr. N. Mahalingam, Chairman, Dr.B.K.Krishnaraj Vanavarayar, Co-Chairman for having provided us with the necessary infrastructure to undertake this project.

We are extremely grateful to **Dr. J.Shanmugam**, **Director**, Kumaraguru College of Technology for having given us a golden opportunity to embark on this project.

We are extremely grateful to **Dr.Ramachandran**, **Principal**, Kumaraguru College of Technology for having given us a golden opportunity to embark on this project

We are deeply obliged to **Dr.Rajeswari Mariappan**, **M.E.,Ph.D.**, Head of the Department of Electronics& Communication for her concern and implication during the project course.

We extend our heartfelt thanks to our Project Coordinator V.Jeyasri Arokiamary, M.E., Associate Prof, and Prof.K.Ramprakash, M.E., Professor, Department of Electronics and Communication and our respectable Guide Ms.G.Amirtha Gowri, M.E., Ph.D., Associate Prof Department of Electronics and Communication for their helpful guidance and valuable support given to us throughout this project. Our thanks to all Teaching and Non-teaching staffs of our department for providing us the technical support for our project.

We also thank our family and friends who helped us to complete this project with flying colours.

### **ABSTRACT**

The prevalence of accidents happening with concern to trains/ railway networks is quite high these days due to natural occurrences like fog, mist, rain, storms and other unfortunate mishaps like server missignalling, etc.

Due to improper or invalid communication between two approaching trains, the consequences may include the trains derailing off the tracks, or crashing into each other due to lack of prior warning.

Several attempts to raise security concerns regarding this issue have been met with failure-prone methods. The main objective of this project is to prevent accidents caused on railway tracks using the concept of RFID (Radio Frequency Identification) tags. This method is cost-effective and easy to implement wherever required. The working of this design is fool-proof and less susceptible to any type of signal failure problems. These tags are attached to the tracks at regular intervals throughout the length of the distance.

The trains are equipped with a RF reader implemented with a RF transceiver. These RF readers are placed underneath the train, so that it receives information from the RF tags immediately when the train runs over the tracks.

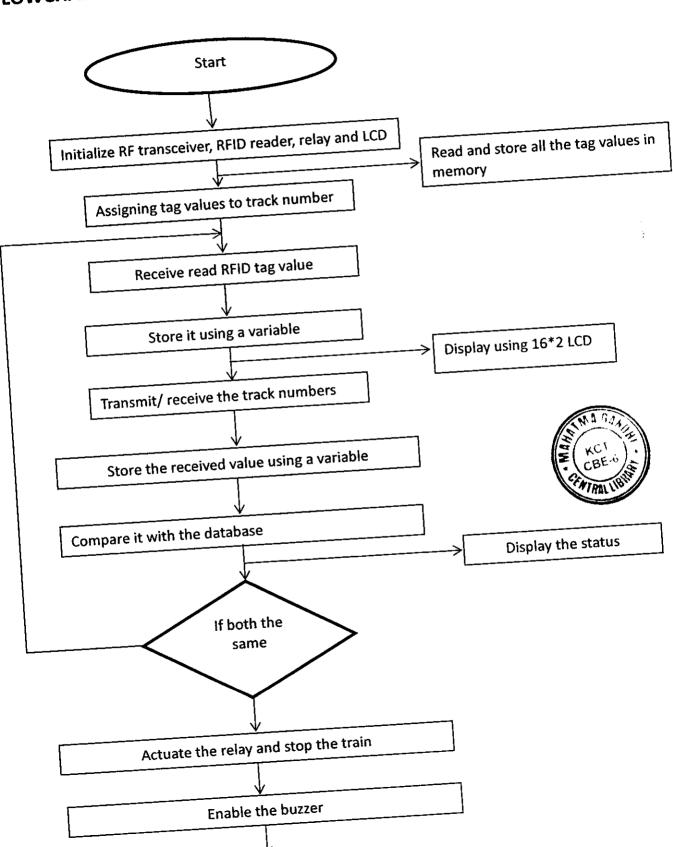

Thus, when the microcontroller in the reader receives information, it is transmitted via the RF transceiver so that the location of the train on the specific track is known to all trains in motion within the span of 5km at that point of time.

So if two trains are found to be in danger of collision on the same track then both the trains will come to halt immediately. A buzzer on the train also automatically alerts the need for such a scenario. Thus, further accidents can be avoided by using this simple mechanism. As a RF tag is complementary to the bar code system, it is fool-proof as well. Also, this project gives scope to expand the horizon of design and create a new technology network in railway departments that will be solely dedicated to ensuring the safety of the passengers and machinery.

|         | TABLE OF CONTENTS TITLE       | PAGE No |

|---------|-------------------------------|---------|

| CHAPTER | ABSTRACT                      | iv      |

|         | LIST OF FIGURES               | ix      |

|         | LIST OF TABLES                | x       |

| 1.      | INTRODUCTION                  | 1       |

|         | 1.1 OVERVIEW                  | 2       |

|         | 1.2 BLOCK DIAGRAM             | 3       |

|         | 1.2.1 OVERVIEW OF RFID BLOCK  | 3       |

|         | 1.2.2 OVIERVIEW OF AT89S52    | 4       |

|         | 1.2.3 OVERVIEW OF IC MAX232   | 4       |

|         | 1.2.4 RF TRANSCEIVER          | 4       |

|         | 1.2.5 RELAY                   | 4       |

|         | 1.2.6 BATTERY                 | 5       |

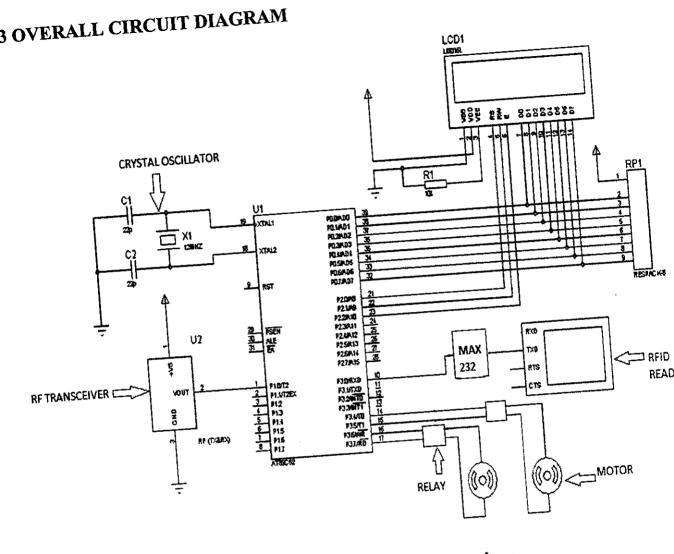

|         | 1.3 OVERALL CIRCUIT DIAGRAM   | 9       |

| 2.      | RFID READER MODULE            | 6       |

|         | 2.1 RFID SYSTEM               | 7       |

|         | 2.2 DEFINITION                | 7       |

|         | 2.3 UNDERSTANDING RF          | 8       |

|         | 2.4 ABOUT RFID                | 8       |

|         | 2.5 WORKING PRINCIPLE OF RFID | 10      |

|         | 2 6 RFID TAGS                 | 10      |

|    | MICROCONTROLLER AT89S52                                                                                                    | 12                         |

|----|----------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3. | 3.1 INTRODUCTION                                                                                                           | 12                         |

|    | 3.2 FEATURES 3.3 INTERNAL ARCHETICTURE                                                                                     | 14                         |

|    | 3.4 MEMORY ORGANIZATION  3.4.1 PROGRAM MEMORY  3.4.2 DATA MEMORY  3.5 UART  3.6 INTERRUPTS  3.7 OSCILLATOR CHARACTERISTICS | 15<br>15<br>15<br>16<br>17 |

|    | 4. SERIAL COMMUNICATION                                                                                                    | 18                         |

|    | 4.1 MAX-232                                                                                                                | 18                         |

|    | 4.2 RS-232 STANDARDS                                                                                                       | 19                         |

|    | 4.3 RS-232 LEVEL CONVERTERS                                                                                                | 20                         |

|    | 4.4 RS-232 INTERFACE                                                                                                       | 21                         |

|    | 4.5 RS-232 PINS<br>4.6 FEATURES OF RS-232                                                                                  | 21                         |

|    | 5 LCD DISPLAY                                                                                                              | 22                         |

|    | 5 1 INTRODUCTION                                                                                                           | 22                         |

|   | <ul><li>5.3 FEATURES</li><li>5.4 MAJOR STEPS IN LCD DISPLAY</li><li>5.5 COMMANDS AND INSTRUCTION SET</li></ul> | 23<br>24<br>24       |

|---|----------------------------------------------------------------------------------------------------------------|----------------------|

| 6 | RF TRANSCEIVER  6.1 INTRODUCTION  6.2 FEATURES  6.3 THEORY OF OPERSTION                                        | 27<br>27<br>27       |

|   | 6.4 RF TRANSMITTER 6.4.1 OVERVIEW 6.4.2 FEATURES 6.4.3 PIN DESCRIPTION 6.4.4 SPECIFICATION                     | 28<br>29<br>29<br>29 |

|   | 6.4.5 OPERATION<br>6.5 RF RECEIVER                                                                             | 29<br>30             |

|   | 6.5.1 OVERVIEW 6.5.2 FEATURES 6.5.3 PIN DESCRIPTION                                                            | 30<br>31<br>31       |

|   | 6.5.4 SPECIFICATION 6.5.5 OPERATION                                                                            | 32                   |

| 7 | DECODER AND ENCODER UNIT 7.1 DECODER                                                                           | 23                   |

- 1 1 DEATIBES

33

|   | 7.1.2 DESCRIPTION       | 34   |

|---|-------------------------|------|

|   | 7.2 ENCODER             |      |

|   | 7.2.1 FEATURES          | 35   |

|   | 7.2.2 DESCRIPTION       | 36   |

| 8 | SOFTWARE                |      |

|   | 10.1 KEIL C             | . 27 |

|   | 10.1.1 FEATURES         | 37   |

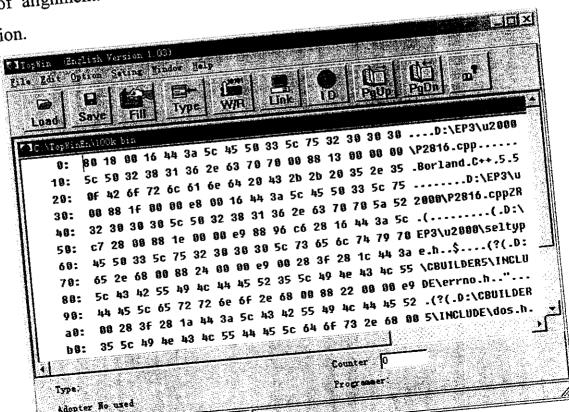

|   | 10.2 TOPWIN             | 38   |

| 9 | CODING AND FLOWCHART    |      |

|   | 11.1 CODING FOR TRAIN A | 39   |

|   | 11.2 CODING FOR TRAIN B | 45   |

|   | 11.3 FLOWCHARTS         | 51   |

|   | CONCLUSION              |      |

|   | FUTURE EXPANSION        |      |

|   | APPENDIX A              |      |

|   | APPENDIX B              |      |

|   | APPENDIX C              |      |

|   | APPENDIX D              |      |

|   | REFERENCES              |      |

# LIST OF FIGURES

|          |                                          | Page no |

|----------|------------------------------------------|---------|

| igure no | Title                                    | 2       |

| .1       | Overall Block diagram                    | 5       |

| 2        | Circuit Diagram                          | 7       |

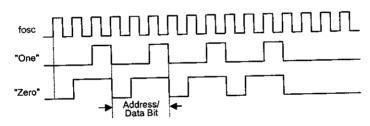

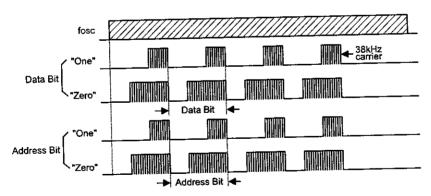

| 2.1      | RFID Frequency                           | 10      |

| 2.2      | RFID Tag                                 |         |

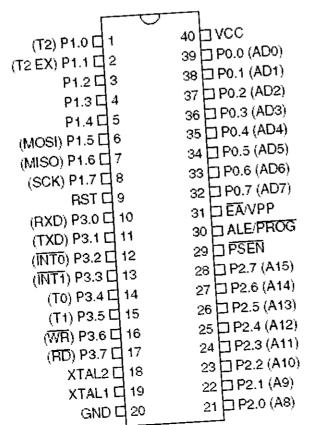

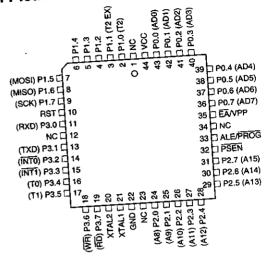

|          | Microcontroller AT89S52 PIN Diagram      | 13      |

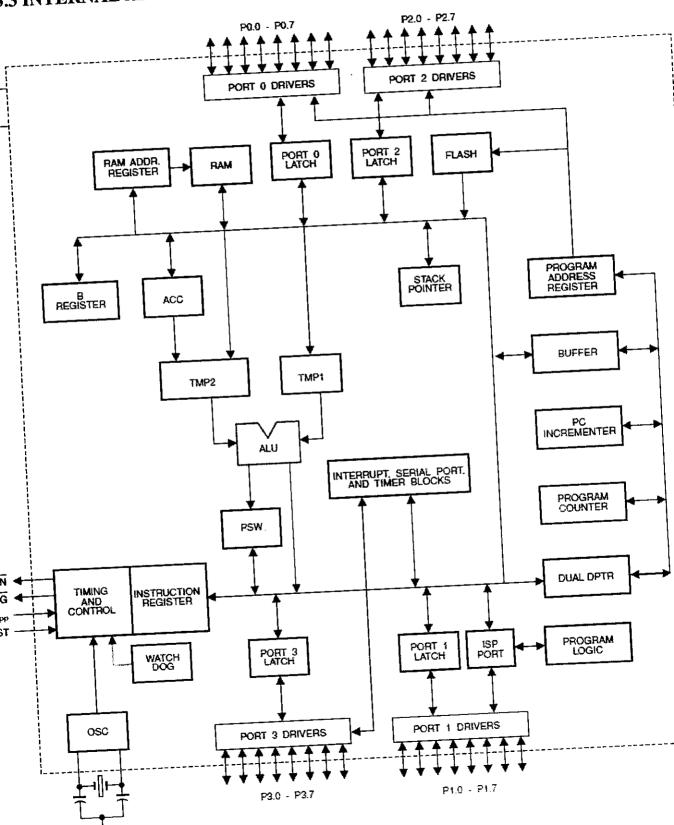

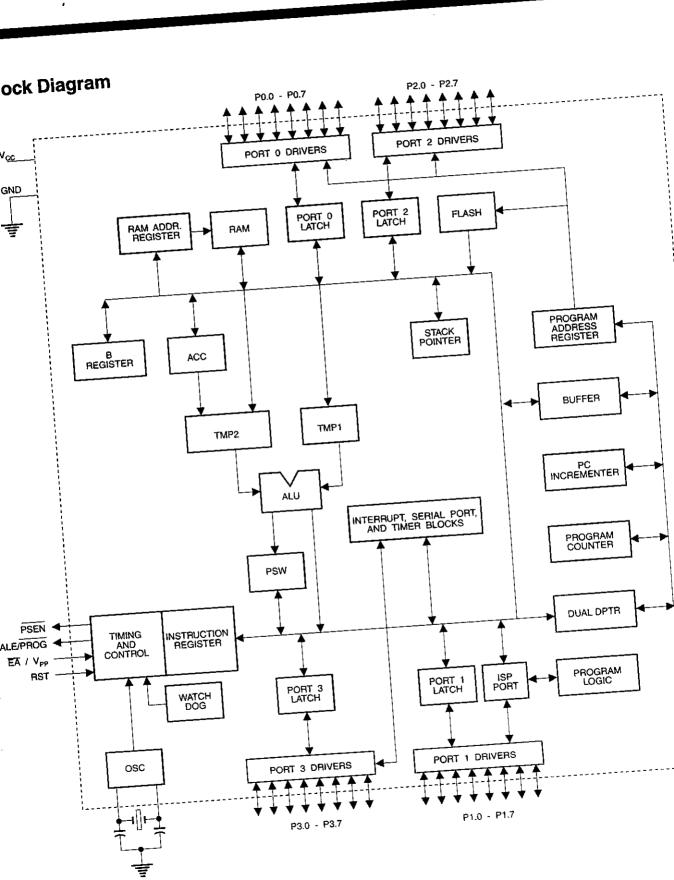

| 3.1      | Internal Architecture of Microcontroller | 14      |

| 3.2      |                                          | 18      |

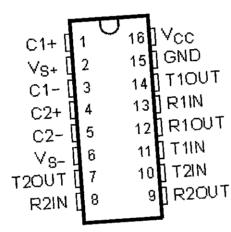

| 4.1      | PIN Diagram of MAX 232                   | 20      |

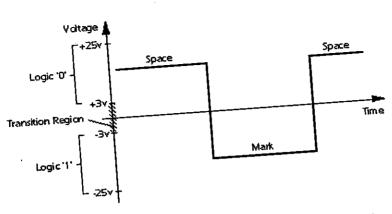

| 4.2      | Voltage levels of RS 232                 | 22      |

| 5.1      | Schematic Diagram of LCD Display         |         |

|          | Schematic View of LCD Display            | 24      |

| 5.2      | PIN Description of RF Transmitter        | 29      |

| 6.1      |                                          | 31      |

| 6.2      | PIN Description of RF Receiver           | 35      |

| 7.1      | Decoder PIN                              | 36      |

| 7.2      | Encoder PIN                              |         |

| 10.1     | TopWin software screenshot               | 38      |

# LIST OF TABLES

| able no | Title                          | Page no.   |

|---------|--------------------------------|------------|

|         | thin of MAX 232                | 18         |

| 4.1     | Pin description of MAX 232     | 25         |

| 5.1     | LCD Commands Table             |            |

| J.1     | RF Transmitter PIN Description | 29         |

| 6.1     |                                | 29         |

| 6.2     | Specification RF Transmitter   | 31         |

| ( )     | RF Receiver PIN Description    | <i>)</i> 1 |

| 6.3     | Specification of RF Receiver   | 31         |

| 6.4     | Specification of Id 1803       |            |

### CHAPTER 1

## INTRODUCTION

## 1.1 OVERVIEW

A significant increase in the number of accidents happening every year due to train collisions has been noticed on a quite regular basis. This is due to unpredictable occurrences such as storms, fogs, mist, etc. which blindside the operators, disrupt signals, as well as cause havoc among the detection systems. Sometimes even the railway tracks are damaged or ruined, and without any prior warning; train accidents are easily prone to happen.

Though a number of initiatives have been taken to prevent such accidents, news of such incidents continue to be heard of often. GPS system, satellite navigation methods, etc. have all been implemented, but none have been fool-proof thus.

Our project is an attempt to rectify the discrepancies in foretelling a collision, and to ensure safe travel on trains. The concept of this project is based on the property and uses of RFID (Radio Frequency Identification). Using the information pre-stored in these RFID tags(Track number) that are placed at strategic location in the tracks, and the consequent data from the RFID readers that are on the moving train, the location of any train at any particular track can be determined. This information is relayed to all trains in motion that are in the nearby vicinity, using a RF Transceiver. If any danger of collision on the same track is determined, then both the trains automatically come to a halt, as well as give out a buzzer warning.

Our project is explained is explained in detail in this report with the contents

and data specifications, etc. We hope this brings out a clear idea of our vision and the capacity for this initiative to be expanded on a wider canvas in the near future.

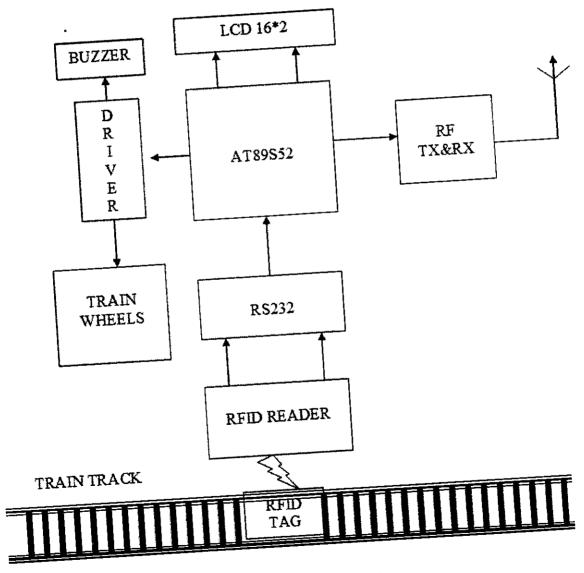

# 1.2 BLOCK DIAGRAM

The block diagram of this project mainly consist of

Fig 1.1 Overall Block Diagram

he block diagram comprises of the overview of Microcontroller

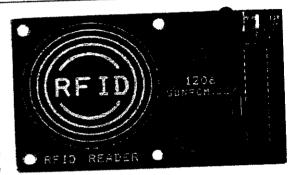

AT89s52),RFID, RF transceiver which are shown in Fig 1.1

# 1.2.1 Overview of RFID Reader block

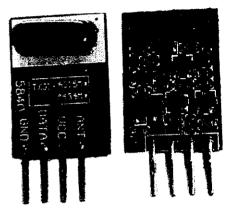

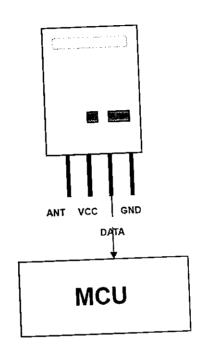

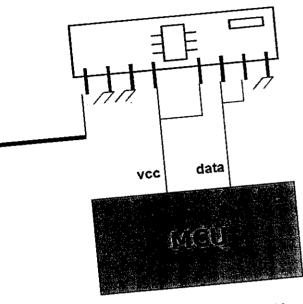

Radio Frequency identification (RFID) card readers provide a lowcost Solution to read passive RFID transponder tags. The RFID card reader read the RFID tag range and outputs unique identification code of the tag at baud rate of 9600. The data from RFID reader is interfaced to be read by the microcontroller.

# 1.2.2 Overview of AT89S52 Microcontroller

The Microcontroller used is AT89S52, it is a low-power, highperformance CMOS 8-bit microcontroller with 4K bytes of In-System Programmable Flash memory. The Unique RFID tag numbers are stored in the microcontroller. The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional non-volatile memory programmer. By combining a versatile 8-bit CPU with In-System Programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.

# 1.2.3 Overview of IC MAX232 Block

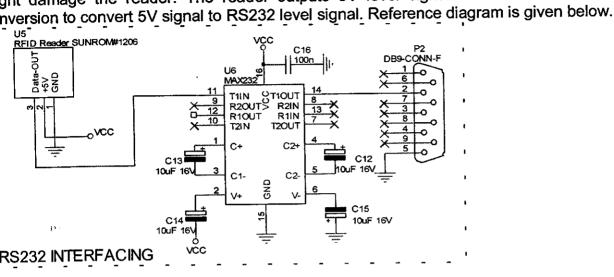

RS-232 is an important part in interfacing a peripheral device with microcontroller. The output of the microcontroller is usually in TTL format but the peripheral devices require a RS-232 input. Hence RS-232 serves the part of serial communication.

## 2.4 RF Transceiver

The RF transceiver Available for operation between 433.075 and 434.725 MHz in 50KHz steps these modules give the possibility of 34 different requency channels and are able to transmit at distances of up to 400m.

- . 12A at 120VAC for RW & 12A at 240VAC for RWH are UL approved. to comply with user's wide selection.

- . RW Series Relay covers switching capacity by 10A is spite of miniature size

- . The employment of suitable plastic materials is applied under high temperature condition and various chemical solutions.

- . Complete protective construction is designed form dust and soldering flux. If required, plastic sealed type is available for washing procedure.

- . RWH is approved C-UL & TÜV safety standard.

The rechargeable batteries are lead-lead dioxide systems. The dilute 1.2.6 BATTERY sealed and is, therefore, maintenance-free, leak proof and usable in any position. immobilized. Should the battery be accidentally overcharged producing hydrogen and oxygen, special one-way valves allow the gases to escape thus avoiding excessive pressure build-up. Otherwise, the battery is completely sulphuric acid electrolyte is absorbed by separators and plates and thus

Fig 1.2 Microcontroller with RFID reader and RF transceiver

## **CHAPTER 2**

# RFID READER MODULE

Although it may seem like a new technology, Radio Frequency 1 RFID SYSTEM dentification (RFID) has been around since the 1940's. In fact the United States Air Force first used RFID technology to track friendly aircraft in world war II.

Today, RFID has the potential to dramatically improve many applications in the industrial, transportation and service industries through automatic detection, identification, and control of products and assets. The expectation for RFID is to provide supply chain efficiencies, reduced labour costs, and accurate real-time resource information.

RFID is a term used for any device that can be sensed at a 2.2 DEFINITION distance by radio frequencies or thereabouts, with a few problems from obstruction or mis-orientation. The origins of the term lie in the invention of tags that reflect or re-transmit a radio frequency signal. In its current usage, those working below 300 Hz and those working above 300 MHz, such as microwave (GHz) tags, are included. For example, one type of chip less tag works at 100 Hz and one recent type of battery-driven chip tag works across 5.7-7.0 GHz, rather than at one frequency. Higher frequencies such as visible and infrared devices are excluded as these systems have very different properties and are frequently sensitive to obstruction, heat, light, and orientation. The term "tag" is used to describe any small device-the shapes vary from pendants to beads, nails, labels, or micro wires and fibres-that can be incorporated into paper and even special printed inks on, for example, paper.

# .3 UNDERSTANDING THE RADIO FREQUENCY

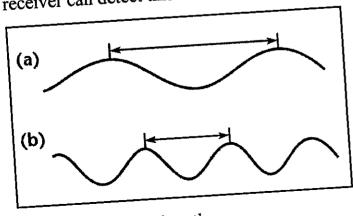

Radio Frequency (RF) is all about physics. RF communication works by creating electromagnetic waves at a source and picking up those electromagnetic waves at a specified destination.

These electromagnetic waves travel through the air at near the speed of light. The wavelength of an electromagnetic signal is inversely proportional to the frequency; the higher the frequency, the shorter the wavelength.

Frequency is measured in Hertz (cycles per second) and radio frequencies are measured in kilohertz (KHz or thousands of cycles per second), megahertz (MHz or millions of cycles per second) and gigahertz (GHz or billions of cycles per second). Higher frequencies result in shorter wavelengths. The wavelength for a 900 MHz device is longer than that of a 2.4 GHz device.

In general, signals with longer wavelengths travel a greater distance and penetrate through, and around objects better than signals with shorter wavelengths. Imagine an RF transmitter wiggling an electron in one location, this wiggling electron causes a ripple effect, somewhat akin to dropping a pebble in a pond. The effect is an electromagnetic wave that travels out from the initial location in electrons wiggling in remote locations. An RF receiver can detect this remote electron wiggling.

- (a) A long wavelength

- (b) A short wavelength

create the frequency of waves

## 4 ABOUT RFID

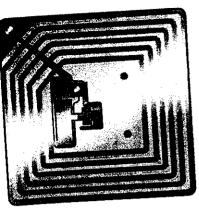

RFID uses wireless technology operating with 50 kHz to 2.5 GHz requency range. A RFID system consists of a RFID tag or transponder that contains data about the tagged item/object, and antenna, a RF transceiver to generate RF signals, and a RFID used for collecting RFID data, which it passes to a host system for processing.

RFID does not require line-of-sight to operate for communications between a tagged object(on the track) and a reader(on the train).

Data encoded on the RFID tag can contain a variety of information about the object, in this case the track number, using electronic product code (EPC).

# 2.5 WORKING PRINCIPLE OF RFID

The combined antenna and microchip are called an "RFID transponder" or "RFID tag" and work in combination with an "RFID reader" (sometimes called an "RFID interrogator"). An RFID system consists of a reader and one or more tags. The reader's antenna is used to transmit radio frequency (RF) energy. Depending on the tag type, the energy is "harvested" by the tag's antenna and used to power up the internal circuitry of the tag. The tag will then modulate the electromagnetic waves generated by the reader in order to transmit its data back to the reader. The reader receives the modulated waves and converts them into digital data. In the case of the Parallax RFID Reader Module, correctly received digital data is sent serially through the SOUT pin. There are two major types of tag technologies.

"Passive tags" are tags that do not contain their own power source or transmitter. When radio waves from the reader reach the chip's antenna, the energy is converted by the antenna into electricity that can power up the migrachin in the tag (known as "parasitic power"). The tag is then able to send

ack any information stored on the tag by reflecting the electromagnetic waves s described above.

"Active tags" have their own power source and transmitter.

The power source, usually a battery, is used to run the microchip's circuitry and to broadcast a signal to a reader. Due to the fact that passive tags do not have their own transmitter and must reflect their signal to the reader, the reading distance is much shorter than with active tags. However, active tags are typically larger, more expensive, and require occasional service. The RFID Reader Module is designed

specifically for low-frequency (125 kHz) passive tags. Frequency refers to the size of the radio waves used to communicate between the RFID system components. Just as you tune your radio to different frequencies in order to hear different radio stations, RFID tags and readers have to be tuned to the same frequency in order to communicate effectively. RFID systems typically use one of the following frequency ranges: low frequency (or LF, around 125 kHz), high frequency (or HF, around 13.56 MHz), ultra-high frequency (or UHF, around 868 and 928 MHz), or microwave (around 2.45 and 5.8 GHz). It is generally safe to assume that a higher frequency equates to

a faster data transfer rate and longer read ranges, but also more sensitivity to environmental factors such as liquid and metal that can interfere with radio waves. There really is no such thing as a "typical" RFID tag. The read range of a tag ultimately depends on many

factors: the frequency of RFID system operation, the power of the reader, and interference from other RF

devices.

Fig 2.2 RFID tag

## 2.6 RFID TAGS

Tag options include the following:

.Passive or active

.Read only, Read-write, or write once

.Short range or long range

Active, semi-passive and passive RFID tags are making RFID technology more accessible and prominent in our world. These tags are less expensive to produce, and they can be made small enough to fit on almost any product.

Active and semi-passive RFID tags use internal batteries to power their circuits. An active tag also uses its battery to broadcast radio waves to a reader, whereas a semi-passive tag relies on the reader to supply its power for broadcasting. Because these tags contain more hardware than passive RFID tags, they are more expensive. Active and semi-passive tags are reserved for costly items that are read over greater distances -- they broadcast high frequencies from 850 to 950 MHz that can be read 100 feet or more away. If it is necessary to read the tags from even farther away, additional batteries can boost a tag's range to over 300 feet (100 meters).

Passive RFID tags rely entirely on the reader as their power source. These tags are read up to 20 feet away, and they have lower production costs, meaning that they can be applied to less expensive merchandise. These tags are manufactured to be disposable, along with the disposable consumer goods on which they are placed. Whereas a railway car would have an active RFID tag, a bottle of shampoo would have a passive tag.

Another factor that influences the cost of RFID tags is data storage. There are three storage types: **read-write**, **read-only** and **WORM** (**write once**, **read-write** tag's data can be added to or overwritten. Read-only tags cannot be added to or overwritten -- they contain only the data that is stored in them when they were made. WORM tags can have additional data (like another serial number) added once, but they cannot be overwritten.

## **CHAPTER 3**

# MICROCONTROLLER AT89S52

The AT89S52 is a low-power, high-performance CMOS 8-bit 3.1 INTRODUCTION microcontroller with 8K bytes of in-system programmable Flash memory. The device is manufactured using Atmel's high-density non-volatile memory technology and is compatible with the industry-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional non-volatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.

The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM con-tents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

## 3.2 FEATURES

- Compatible with MCS®-51 Products

- 8K Bytes of In-System Programmable (ISP) Flash Memory

- Endurance: 10,000 Write/Erase Cycles

# Three-level Program Memory Lock

# 256 x 8-bit Internal RAM

# 32 Programmable I/O Lines

# Three 16-bit Timer/Counters

# Eight Interrupt Sources

- Full Duplex UART Serial Channel

- Low-power Idle and Power-down Modes

- Interrupt Recovery from Power-down Mode

- Watchdog Timer

- Dual Data Pointer

- Power-off Flag

- Fast Programming Time

- Flexible ISP Programming (Byte and Page Mode)

- Green (Pb/Halide-free) Packaging Option

# 3.3 INTERNAL ARCHITECTURE

# .4 Memory Organization

ACS-51 devices have a separate address space for Program and Data Memory.

Jp to 64K bytes each of external Program and Data Memory can be addressed.

If the EA pin is connected to GND, all program fetches are directed to external memory. On the AT89S52, if EA is connected to VCC, program fetches to addresses 0000H through 1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are to external memory.

The AT89S52 implements 256 bytes of on-chip RAM. The upper 128 bytes 3.4.2 Data Memory occupy a parallel address space to the Special Function Registers. This means that the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space. When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions which use direct addressing access the SFR space.

For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2). MOV 0A0H, #data Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H). MOV @R0, #data Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space.

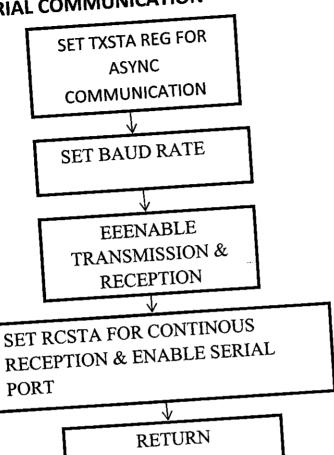

A universal asynchronous receiver/transmitter, abbreviated UART, is a **3.5 UART** type of "asynchronous receiver/transmitter", a piece of computer hardware that Hal and social forms HARTs are commonly used in 485. The universal designation indicates that the data format and transmission speeds are configurable and that the actual electric signalling levels and methods typically are handled by a special driver circuit external to the UART.

It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the receive register. (However, if the first byte still hasn't been read by the time reception of the second byte is complete, one of the bytes will be lost). The serial port receive and transmit registers are both accessed at Special Function Register SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically second receive register.

### 3.6 INTERRUPTS

The AT89S52 has a total of six interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (Timers 0, 1, and 2), and the serial port interrupt. Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE. IE also contains a global disable bit, EA, which disables all interrupts at once. Note that Table 13-1 shows that bit position IE.6 is unimplemented. User software should not write a 1 to this bit position, since it may be used in future AT89 products. Timer 2 interrupt is generated by the logical OR of bits TF2 and EXF2 in register T2CON. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine may have to determine whether it was TF2 or EXF2 that generated the interrupt, and that bit will have to be cleared in software.

The Timer 0 and Timer 1 flags, TF0 and TF1, are set at S5P2 of the cycle in which the timers overflow. The values are then polled by the circuitry in the next cycle. However, the Timer 2 flag, TF2, is set at S2P2 and is polled in the same cycle in which the timer overflows.

# 3.7 OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 16-1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven, as shown in Figure 16-2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clock-ing circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

# CHAPTER 4 SERIAL COMMUNICATION

The MAX232 is a dual driver/receiver that includes a capacitive voltage 4.1 MAX-232 generator to supply TIA/EIA-232 voltage levels from a single 5V supply. Each receiver converts TIA/EIA-232-F inputs to 5V TTL/CMOS levels. These receivers have a typical threshold of 1.3 V, a typical hysteresis of 0.5 V and can accept ±30V inputs. Each driver converts TTL/CMOS input levels into TIA/EIA-232 levels.

Fig 4.1 Pin configuration of MAX 232

|        | Fig 4.1 Fin configuration          |

|--------|------------------------------------|

|        | DESCRIPTION                        |

| PIN NO | The positive terminal of capacitor |

| 1      | The positive terminar              |

|        | C1 is connected.                   |

|        | A supply voltage of +5V            |

| 2      | Negative terminal of C1            |

| 3      | Positive terminal of C2            |

| 4      | Tositive terminal of C2            |

| ·                                     |                                   |

|---------------------------------------|-----------------------------------|

|                                       | Negative supply of -5V            |

|                                       | Driver 2 output( RS 232)          |

|                                       | Receiver 2 input(RS 232)          |

| · · · · · · · · · · · · · · · · · · · | Receiver 2 output(TTL)            |

|                                       | Driver 2 input(TTL)               |

| 10                                    | Driver 1 input(TTL)               |

| 11                                    | Receiver 1 output(TTL)            |

| 12                                    | Receiver 1 input(TTL)             |

| 13                                    |                                   |

| 14                                    | Driver 1 output (RS 232)          |

| 15                                    | ground                            |

| 16                                    | VCC (+5V)                         |

| · L                                   | le 4.1 Pin description of MAX 232 |

Table 4.1 Pin description of MAX 232

# 4.2 RS-232 STANDARDS

- 1.Most widely used serial I/O interfacing standard.

- 2.Used in PC's and numerous types of equipments.

- 3.it is not compatible with I/O voltage levels of TTL logic family.

# **VOLTAGE LEVELS IN RS-232**

- 1.Logic high(1) represented as -3 to -25

- 2.Logic low(0) represented as +3 to +25

- 3.-3 to +V not defined.

Fig 4.2 Figure of voltage levels of RS 232

# **4.3 RS-232 LEVEL CONVERTERS**

Usually all the digital ICs work on TTL or CMOS voltage levels which cannot be used to communicate over RS-232 protocol. So a voltage or level converter is needed which can convert TTL to RS232 and RS232 to TTL levels. voltage

The most commonly used RS-232 level converter is MAX232. This IC includes charge pump which can generate RS232 voltage levels (-10V and +10V) from 5V power supply. It also includes two receiver and two transmitters and is capable of full-duplex UART/USART communication.

- 4.4 RS 232 INTERFACE 1. RS=232 was introduced in 1960, and is currently the most widely used communication protocol. It is simple, inexpensive to implement, and though relatively slow it is more than adequate for most simple serial communication devices such as keyboards and mice.

- 2. 232 is a single-ended data transmission system, which means that it uses a single wire for data transmission.

- 3. since useful communication is generally two way, a two wire system is

## .5 RS 232 PINS

The table provides the pins and the labels for the RS 232 cable, commonly reffered to as DB-25 connector

The standard for RS 232 and similar interfaces usually restrict RS 232 to 20Kbps or less and line length of 15m or less.RS 232 is fair more robust than the traditional limits of 20Kbps over a 15m line would imply RS 232 as oerfectly adequate at speed upto 200Kbps Most RS 232 ports on mainframe and midrange computers are capable of far higher speeds than their rated 19.2Kbps. Usually these 1000 speed parts will run error free at 56Kbps and above 15m limitations for enable length can be strtched to about 20m for ordinary cable if well scanned and grounded, and about 100m if the cable is 10m capacity.

# 4.6 FEATURES OF RS 232

The essential features of RS 232 is the signals are carried as signla voltages referred to a common earth and print data to a common earth pin data is transmitted and received on pins 2&3 respectively. Data Set Ready (DSR) is an indication for the data set. i.e, the modem DSU/CSU i.e, it is on. Similarly, DTR indicates to the data set that the DTE is on. Data carrier (DCD) indicates that the carrier for transmit data is on. Pins 4&5 carry the RTS and CTS signals. In most situations RTS and CTS constantly go throughtout the communication session. However when the DTE is connected to a turn carrier on the modem on and off. On a multipoint linear, it is imperative that only one station is tranmitting at a line when a station wants to transmit, it raises RTS the modem turns on carrier.

The truth table for RS 232

Signal>+3V=0

Signal <-3V=1

t rignal level usually swings between +12V and -12V, the

## CHAPTER 5

## LCD DISPLAY

# 5.1 INTRODUCTION

LCD's also are used as numerical indicators, especially in digital watches where their much smaller current needs than LED displays (microamperes compared with mill amperes) prolong battery life. Liquid crystals are organic (carbon) compounds, which exhibit both solid and liquid properties. A 'cell' with transparent metallic conductors, called electrodes, on opposite daces, containing a liquid crystal, and on which light falls, goes 'dark' when a voltage is applied across the electrodes. The effect is due to molecular rearrangement within the liquid crystal. The LCD display used in this project consists of 2 rows. Each row consists of maximum 16 characters. So using this display only maximum of 32 characters can be displayed

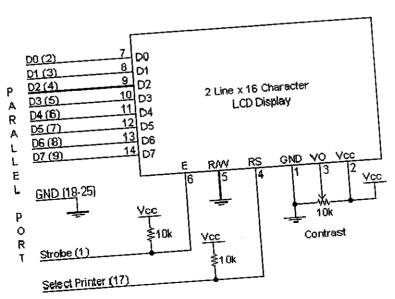

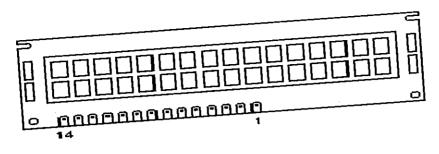

Fig 5.1 Schematic diagram of LCD display

# 3.2 CIRCUIT DESCRIPTION

- The LCD panel's Enable (E) of pin (6) and Register Select (RS) of pin (4) are connected to the Control Port (port 2).

- The Control Port is an open collector / open drain output. While all ports except port 0 have internal pull-up resistors, hence we incorporate the two 10K external pull up resistors, the circuit is more portable for a wider range of devices, some of which may have no internal pull up resistors.

- There is no need to make the Data bus into reverse direction. Hence hard wire the R/W line pin (5) of the LCD panel, into write mode. This will cause no bus conflicts on the data lines. As a result, read back the LCD's internal Busy Flag is not possible, which tells us if the LCD has accepted and finished processing the last instruction. This problem is overcome by inserting known delays into our program.

- The 10k Potentiometer controls the contrast of the LCD panel through V0 of pin (3). Pin (1) is ground.

The lines D0-D7 are called data lines they are connected with the port 0 through internal pull up resistors. They belong to the pins (7-14) .pin (12) forms the supply VCC.

# 5.3 FEATURES OF LCD DISPLAY

- 16 Characters x 2 Lines.

- 5 x 7 Dots with Cursor.

- Built in Controller.

- +5v Power Supply (Also Available for +3V).

Fig 5.2 Schematic view of LCD display

# 5.4 MAJOR STEPS IN LCD DISPLAY

Major task in LCD interfacing is the initialization sequence. In LCD initialization you have to send command bytes to LCD. Here you set the interface mode, display mode, address counter increment direction, set contrast of LCD, horizontal or vertical addressing mode, color format. This sequence is given in respective LCD driver datasheet. Studying the function set of LCD lets you know the definition of command bytes. It varies from one LCD to another. If you are able to initialize the LCD properly 90% of your job is done.

Next step after initialization is to send data bytes to required display data RAM memory location. Firstly set the address location using address set command byte and then send data bytes using the DDRAM write command. To address specific location in display data RAM one must have the knowledge of how the address counter is incremented.

# 5.5 COMMANDS AND INSTRUCTION SET

Only the instruction register (IR) and the data register (DR) of the LCD can be controlled by the MCU. Before starting the internal operation of the LCD, control information is temporarily stored into these registers to allow LCD, control information is temporarily stored at different speeds, or various

gnals sent from the MCU. These signals, which include register selection gnal (RS), read/write signal (R/W), and the data bus (DB0 to DB7), make up ne LCD instructions (Table 3). There are four categories of instructions that:

- Designate LCD functions, such as display format, data length, etc.

- Set internal RAM addresses

- Perform data transfer with internal RAM

- Perform miscellaneous functions

| erform miscel     | lane       | ous   | tur          | icuc           | )[15                    |      |     |                           |     |          |                |                           |     |             |

|-------------------|------------|-------|--------------|----------------|-------------------------|------|-----|---------------------------|-----|----------|----------------|---------------------------|-----|-------------|

| Olioz-            |            |       |              |                |                         | D    | 3   | $\overline{\mathbf{D}^2}$ |     | D        | 1              | $\overline{\mathbf{p}_0}$ | 1   | HEXADECIMAL |

| COMMANDS          | <b>D</b> 7 | D     | 6            | <b>D</b> 5     | D4                      | 1    |     |                           |     |          |                |                           |     | VALUE       |

|                   | l          |       | 1            |                |                         |      |     |                           |     | <u> </u> |                | 1                         |     | 01          |

|                   | 0          | 10    | -+           | 0              | 0                       | C    | ,   | 0                         | !   | 0        |                | \                         | }   |             |

| CLEAR             | 10         | 1     | 1            | _              | \                       |      |     | <u> </u>                  |     | 1        |                | X                         |     | 02 or 03    |

| DISPLAY           | 0          | $+_0$ |              | 0              | 0                       | _ (  | )   | 0                         |     | 1        |                | 1.                        | . \ |             |

| DISPLAY &         | 10         | Ĭ     |              | ļ              |                         | \    |     |                           |     |          |                | 1                         | . } |             |

| CURSOR            | 1          |       |              | \<br>\         |                         |      |     | +                         |     | +-       | 1/D            | 15                        |     | 04 to 07    |

| HOME<br>CHARACTER | 10         | -17   | 0            | 0              | _ \ 0                   | \    | 0   | 1                         | ,   |          | ., -           | \                         |     |             |

|                   |            |       |              | 1              |                         | 1    |     |                           |     | 1        |                | \_                        |     | <u> </u>    |

| ENTRY<br>MODE     | \          |       |              |                |                         |      | 1   | ╁                         | D   | 7        | Ū              | 7                         | В   | 08 to 0F    |

| DISPLAY ON        | 0          |       | 0            | 0              |                         | )    | ı   |                           | _   | 1        |                | $\perp$                   |     | 15          |

| AND OFF           | \ _        |       |              |                |                         | 1    | D/0 | -                         | R/I |          | X              | _ \                       | X   | 10 to 1F    |

| DISPAY/           | 0          | )     | 0            | 0              |                         | 1    |     |                           |     | }        |                | 1                         |     |             |

| CURSOR            |            | }     | l            | 1              | \                       |      | 1   | ١                         |     |          |                | \                         |     | 20 to 3F    |

| SHIFT             |            |       | <del> </del> | $-\frac{1}{1}$ |                         | 8/4  | 2/1 | <br>l                     | 10  | 17       | X              | }                         | X   | 20 10 31    |

| FUNCTION          | - 1        | 0     | 0            | 1              | · \                     | 0, - | 1   |                           |     |          | <del>  -</del> |                           | -   | 40 to 7F    |

| SET               |            |       | +            |                | $\overline{\mathbf{A}}$ | Α    | A   |                           | A   |          | A              |                           | A   | 40 10 11    |

| SET DDRAM         | VI \       | 0     | 1            | \              |                         |      | \   |                           | 1_  |          | +-             |                           | A   | 80 to FF    |

| ADDRESS           |            | 0     | TA           | -+             | $\overline{A}$          | A    | A   |                           | A   |          | A              | 7                         | 1   | .           |

| SET               | . \        | U     | \            | `              |                         |      |     |                           |     |          |                |                           |     |             |

| DISPLAY           |            |       |              | \              |                         |      |     |                           |     |          |                |                           |     |             |

| ADDRES            | 55         |       |              |                |                         |      |     |                           |     |          | e ta           | .hl                       | Ω   |             |

Table 5.1 LCD commands table

- 1/D '1' corresponds to increment

- '0' corresponds to decrement

- '1' display on

- U '1' corresponds to cursor underline on

- '0' cursor underline off

- B -'1' corresponds to cursor blink on

- '0' corresponds to cursor underline off

- R/L -'1' corresponds to right shift

- '0' corresponds to left shift

- 8/4 -'1' corresponds to 8bit interface

- '0' corresponds to 4 bit interface

- 2/1 -'1' corresponds to 2 line mode.

- '0' corresponds to 4 line mode.

- 10/7 -'0' corresponds to 5\*10 dot frame format

- '1' corresponds to 5\*7 display format

## CHAPTER 6

## RF TRANSCEIVER

## 6.1 INTRODUCTION

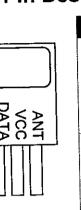

The 433.92 MHz RF Transmitter allows users to easily send serial data, robot control, or other information wirelessly. When paired with the matched RF Receiver, reliable wireless communication is as effortless as sending serial data. The power-down (PDN) pin may be used to place the module into a low power state (active low), or left floating (it is tied high internally).

### 6.2 FEATURES

- High-speed data transfer rates (1200 ~ 19.2k Baud depending on controller used)

- SIP header allows for ease of use with breadboards

- Compatible with all BASIC Stamp® modules (including BS1 and Javelin Stamp) and SX chips

- As easy to use as simple SEROUT/SERIN PBASIC instructions

- Power-down mode for conservative energy usage (longer battery life)

- Line-of-sight range of 500 feet (or greater depending on conditions)

6.3 THEORY OF OPERATION Short for Radio Frequency, RF refers to the frequencies that fall within the electromagnetic spectrum associated with radio wave propagation. When applied to an antenna, RF current creates electromagnetic fields that propagate the applied signal through space. Any RF field has a wavelength that is inversely proportional to the frequency. This means that the frequency of an RF signal is inversely proportional to the wavelength of the field. The Parallax RF modules utilize a frequency of 433.92 MHz, this works out to be a

33.92 MHz falls into the Ultra High Frequency (UHF) designation, which is defined as the frequencies from 300 MHz  $\sim$  3 GHz. UHF has free-space wavelengths of 1 m  $\sim$  100 mm (3.28  $\sim$  0.33 feet or  $1.05e-16 \sim 1.05e-17$  light-years).

## **6.4 RF TRANSMITTER**

### 6.4.1 Overview

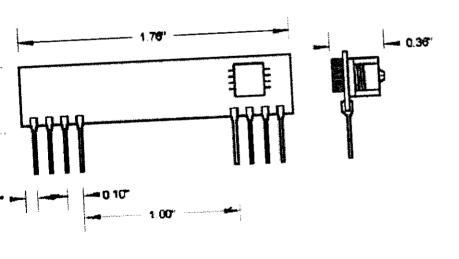

The STT-433 is ideal for remote control applications where low cost and longer range is required. The transmitter operates from a 1.5-12V supply, making it ideal for battery-powered applications. The transmitter employs a SAW-stabilized oscillator, ensuring accurate frequency control for best range performance. Output power and harmonic emissions are easy to control, making FCC and ETSI compliance easy. The manufacturing-friendly SIP style package and lowcost make the STT-433 suitable for high volume applications.

### 6.4.2 Features

- 433.92 MHz Frequency

- Low Cost

- 1.5-12V operation

- 11mA current consumption at 3V

- Small size

- 4 dBm output power at 3V

| N DESCI | RIPTION         | Description                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Pin Name<br>ANT | 50 ohm antenna output. The antenna port impedance affects output power and harmonic emissions. An L-C low-pass filter may be needed to sufficiently filter harmonic emissions. Antenna can be single core wire of approximately 17cm length or PCB                                                                                |

| ANT     | VCC             | Operating voltage for the transmitter. VCC should be bypassed  Operating voltage for the transmitter. VCC should be bypassed  with a .01uF ceramic capacitor and filtered with a 4.7uF tantalum  with a .01uF ceramic capacitor and filtered with a 4.7uF tantalum  appacitor. Noise on the power supply will degrade transmitter |

|         | DATA            | noise performance.                                                                                                                                                                                                                                                                                                                |

| ig 6.1  | GND             | driven with CMOS level inputs.  Transmitter ground. Connect to ground plane.                                                                                                                                                                                                                                                      |

|         |                 |                                                                                                                                                                                                                                                                                                                                   |

Table 6.1

| 6.4.4 SPECIFICATION |        |     | Typ                                  | Max | Unit     |

|---------------------|--------|-----|--------------------------------------|-----|----------|

|                     | Symbol | Min | Typ.                                 | 12  | Volts DC |

| Parameter           | Vcc    | 1.5 | 3.0                                  | _   | mA       |

| Operating Voltage   | Icc    | -   | 11mA @3V<br>59mA @5V                 |     |          |

| Operating Current   |        |     | 100                                  |     | uA       |

| Data = VCC          | Icc    | -   | 100                                  |     |          |

| Operating Current   |        |     | 0                                    | +75 | Khz      |

| Data = GND          | TOL fc | -75 |                                      | _   | Mhz      |

| Frequency Accuracy  | Fc     | -   | 433                                  |     | dBm/n    |

| Center Frequency    |        | -   | 4 dBM@3V (2 mW)<br>16 dBM@5V (39 mW) |     |          |

| RF Output Power     |        |     |                                      | 3K  | BPS      |

|                     |        | 200 | 1K                                   | +60 | Deg. C   |

| Data Rate           |        | -20 |                                      |     | ms       |

| Temperature         |        |     | 20                                   |     |          |

| Power up delay      |        |     |                                      |     |          |

Table 6.2

OOK(On Off Keying) modulation is a binary form of amplitude 6.4.5 OPERATION modulation. When a logical 0 (data line low) is being sent, the transmitter is off, the transmitter current is very low, tate, the module current consumption is at its highest, about 11mA with a 3V power supply.

OOK is the modulation method of choice for remote control applications where power consumption and cost are the primary factors. Because OOK transmitters draw no power when they transmit a 0, they exhibit significantly better power consumption than FSK transmitters.

OOK data rate is limited by the start-up time of the oscillator. High-Q oscillators which have very stable center frequencies take longer to start-up than low-Q oscillators. The start-up time of the oscillator determines the maximum data rate that the transmitter can send.

### 6.5 RF RECEIVER

#### 6.5.1 Overview

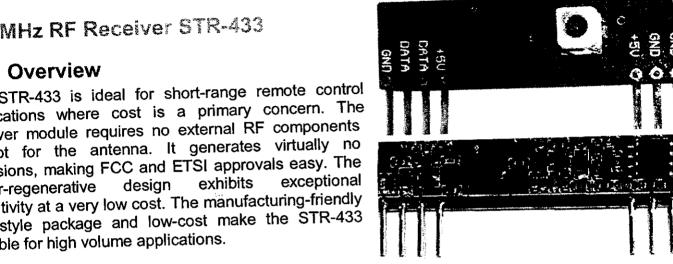

The STR-433 is ideal for short-range remote control applications where cost is a primary concern. The receiver module requires no external RF components except for the antenna. It generates virtually no emissions, making FCC and ETSI approvals easy. The super-regenerative design exhibits exceptional sensitivity at a very low cost. The manufacturing-friendly SIP style package and low-cost make the STR-433 suitable for high volume applications.

### 6.5.2 Features

- Low Cost

- 5V operation

- 3.5mA current drain

- No External Parts are required

- Receiver Frequency: 433.92 MHZ

- Typical sensitivity: -105dBm

- IE Frequency: 1MHz

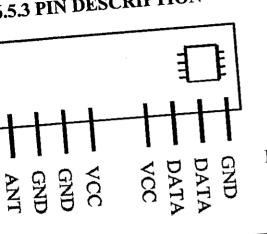

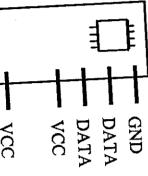

## 5.5.3 PIN DESCRIPTION

Fig 6.2

| H D U (  |                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

|          | Description                                                                                                                            |

| Pin Name |                                                                                                                                        |

| / (1 4 - | Antenna input.  Receiver Ground. Connect to ground plane.  Receiver Ground. Connected and provide operating voltage for the            |

| GND      |                                                                                                                                        |

| VCC(5V)  | receiver. VCC can be apply the receiver. VCC can be apply the receiver.                                                                |

|          | with a .1µF ceramic capable receiver sensitivity.  This output is capable of driving one TTL or CMOS logital data output. This output. |

| DATA     | It is a CMOS compatible output.                                                                                                        |

|          | Table 6.3                                                                                                                              |

## 6.5.4 SPECIFICATION

Operating Temperature

| 0.5.4 ST ECT        |        |       |        | I for | Uni  |

|---------------------|--------|-------|--------|-------|------|

|                     | Symbol | Min   | Typ.   | Max   | VDC  |

| Parameter           |        | 4.5   | 5.0    | 5.5   |      |

| Operating Voltage   | Vcc    | 7.0   | 3.5    | 4.5   | mA   |

| Operating voices    | lcc    | -     | 1.0    | _     | MHZ  |

| Operating Current   | BW rx  | _     |        | _     | MHZ  |

| Reception Bandwidth | Fc     | _     | 433.92 | _     | dBm  |

| Center Frequency    |        | -     | -105   | 01/   | Kbit |

| Sensitivity         |        | 300   | 1k     | 3K    |      |

| Max Data Rate       | -      | 1 000 | 25     |       | ms   |

| Max Data Turo       | -      |       |        | +60   | °C   |

| Turn On Time        | Top    | -10   |        |       |      |

| Tomperature         |        |       |        |       |      |

## 5.5.5 OPERATION

The STR-433 uses a super-regenerative AM detector to demodulate the incoming AM carrier. A super-regenerative detector is a gain stage with positive feedback greater than unity so that it oscillates. An RC-time constant is included in the gain stage so that when the gain stage oscillates, the gain will be lowered over time proportional to the RC time constant until the oscillation eventually dies. When the oscillation dies, the current draw of the gain stage decreases, charging the RC circuit, increasing the gain, and ultimately the oscillation starts again. In this way, the oscillation of the gain stage is turned on and off at a rate set by the RC time constant. This rate is chosen to be superaudible but much lower than the main oscillation rate. Detection is accomplished by measuring the emitter current of the gain stage. Any RF input signal at the frequency of the main oscillation will aid the main oscillation in restarting. If the amplitude of the RF input increases, the main oscillation will stay on for a longer period of time, and the emitter current will be higher. Therefore, we can detect the original base-band signal by simply low-pass filtering the emitter current.

The average emitter current is not very linear as a function of the RF input level. It exhibits a 1/ln response because of the exponentially rising nature of oscillator start-up. The steep slope of a logarithm near zero results in high sensitivity to small input signals.

### **CHAPTER 7**

## DECODER AND ENCODER UNIT

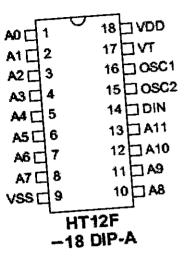

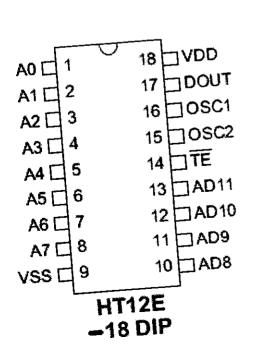

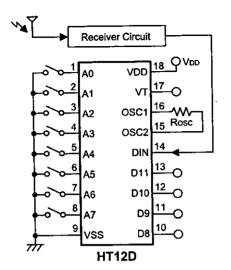

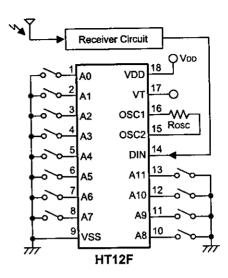

### 7.1 DECODER

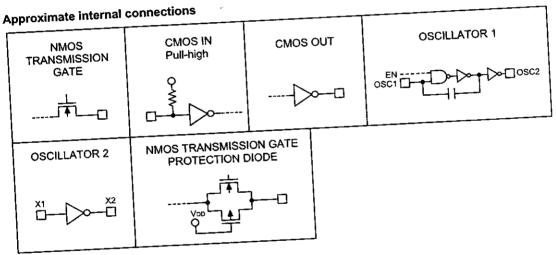

### 7.1.1 Features

- Operating voltage: 2.4V~12V

- Low power and high noise immunity CMOS technology

- Low standby current

- Capable of decoding 12 bits of information

- Binary address setting

- Received codes are checked 3 times

- Address/Data number combination

- HT12D: 8 address bits and 4 data bits

- HT12F: 12 address bits only

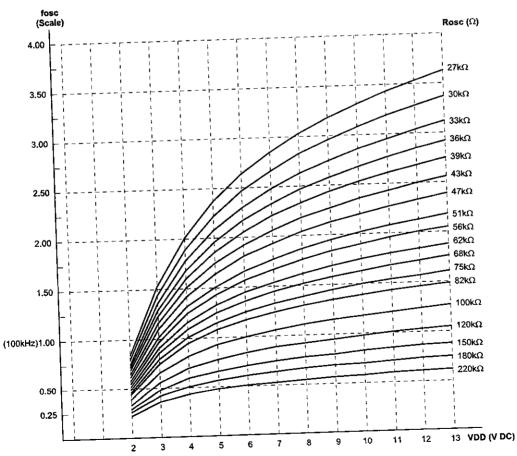

- Built-in oscillator needs only 5% resistor

- Valid transmission indicator

- Easy interface with an RF or an infrared transmission medium

- Minimal external components

- Pair with Holtek\_s 212 series of encoders

- 18-pin DIP, 20-pin SOP package

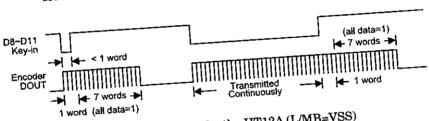

## 7.1.2 DESCRIPTION

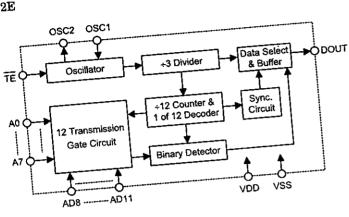

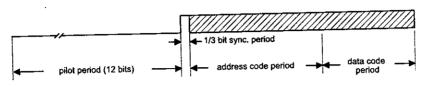

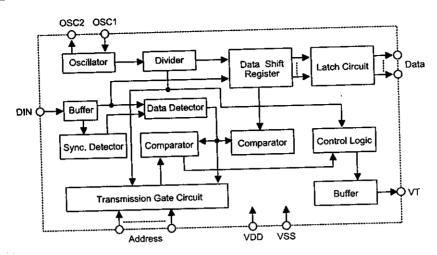

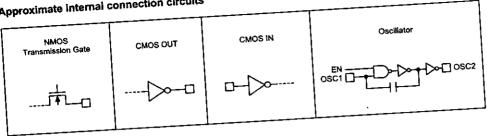

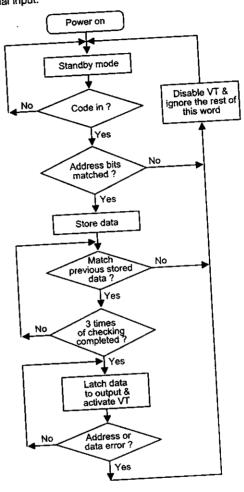

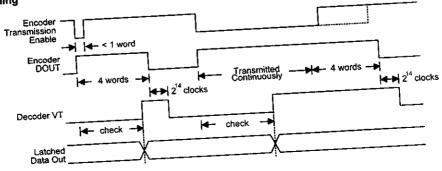

The 212 decoders are a series of CMOS LSIs for remote control system applications. They are paired with Holtek\_s 212 series of encoders (refer to the encoder/decoder cross reference table). For proper operation, a pair of encoder/decoder with the same number of addresses and data format should be chosen.

The decoders receive serial addresses and data from a programmed 212 series of encoders that are transmitted by a carrier using an RF or an IR transmission medium. They compare the serial input data three times continuously with their local addresses. If no input data codes are found, the input data codes are decoded error or unmatched codes are found, the input data codes are decoded and then transferred to the output pins. The VT pin also goes high to indicate a valid transmission.

The 212 series of decoders are capable of decoding information's that consist of N bits of address and 12\_N bits of data. Of this series, the HT12D is arranged to provide 8 address bits and 4 data bits, and HT12F is used to decode 12 bits of address information.

#### 12-Address 0-Data

Fig 7.1 Decoder Pin

## 7.2 ENCODER

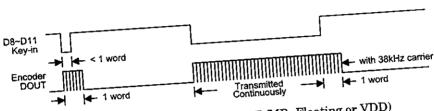

## 7.2.1 FEATURES

- Operating voltage

- 2.4V~5V for the HT12A

- 2.4V~12V for the HT12E

- Low power and high noise immunity CMOS technology

- Low standby current: 0.1\_A (typ.) at VDD=5V

- HT12A with a 38kHz carrier for infrared Transmission medium

- Minimum transmission word

- Four words for the HT12E

- Built-in oscillator needs only 5% resistor

- Data code has positive polarity

- Minimal external components

- HT12A/E: 18-pin DIP/20-pin SOP package

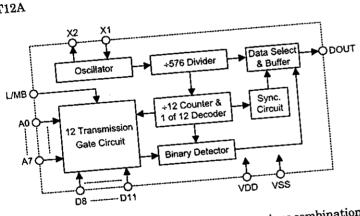

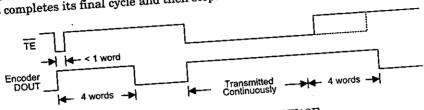

## 7.2.2 DESCRIPTION

The 212 encoders are a series of CMOS LSIs for remote control system applications. They are capable of encoding information which consists of N address bits and 12\_N data bits. Each address/ data input can be set to one of the two logic states. The programmed addresses/data are transmitted together with the header bits via an RF or an infrared transmission medium upon receipt of a trigger signal. The capability to select a TE trigger on the HT12E or a DATA trigger on the HT12A further enhances the application flexibility of the 212 series of encoders. The HT12A additionally provides a 38kHz carrier for infrared systems.

E-soder Pin

### CHAPTER 10

### **SOFTWARE**

### 10.1 KEIL-C

The Keil C51 C Compiler for the 8051 microcontroller is the most popular 8051 C compiler in the world. It provides more features than any other 8051 C compiler available today.

The C51 Compiler allows you to write 8051 microcontroller applications in C that, once compiled, have the efficiency and speed of assembly language. Language extensions in the C51 Compiler give you full access to all resources of the 8051.

The C51 Compiler translates C source files into relocatable object modules which contain full symbolic information for debugging with the μVision Debugger or an in-circuit emulator. In addition to the object file, the compiler generates a listing file which may optionally include symbol table and cross reference information.

### 10.1.1 FEATURES

- Nine basic data types, including 32-bit IEEE floating-point,

- Flexible variable allocation with bit, data, bdata, idata, xdata, and pdata memory types,

- Interrupt functions may be written in C,

- Full use of the 8051 register banks,

- Complete symbol and type information for source-level debugging,

- Use of AJMP and ACALL instructions,

- Bit-addressable data objects,

## 0.2 TOPWIN

TopWin, a type of software developed for TOP series programmers, adapts to the TOP hardware products of a new generation. TopWin has abandoned its method of one type of software matching for one mode of TOP product by operating different mode of hardware units. TopWin supports automatic identification of hardware mode and function. Once TopWin connects to hardware unit successfully, the name of hardware unit will appear at the bottom of window. The current basic modes that TopWin supported include TOP853, TOP2004, TOP2005 and TOP2048. Product of new mode developed in the future will be supported by new version of TopWin software.

TopWin supports multi-window operation, namely, it can connect multiple programmers on a computer to write device without any interference. Mode of programmer can be same or different. TopWin opens all devices in order of alignment. In theory, the number of connected devices is out of limitation.

# CHAPTER 11 CODING AND FLOWCHART

## 1.1 CODING FOR TRAIN A

#include<reg52.h>

#include<8lcd.h>

sbit rx0=P1^0;

sbit rx1=P1^1;

sbit rx2=P1^2;

sbit rx3=P1^3;

sbit tx0=P1^4;

sbit tx1=P1^5;

sbit tx2=P1^6;

sbit tx3=P1^7;

sbit buzzer=P2^7;

sbit m1p= $P3^4$ ;

```

bit m2p=P3^6;

bit m2n=P3^7;

void main()

unsigned char i=0,rfid[16];

unsigned char condition=0;

SCON=0x50;

TMOD=0x20;

TH1=0xFD;

TR1=1;

lcd_init();

lcd_data('S');

m1p=0;

m1n=0;

m2p=0;

m2n=0;

tx0=0;

tx1=0;

```

```

tx3=0;

SBUF='S';

while(1)

{

buzzer=1;

lcd_command(0x80);

lcd_display("RFID CARD NO:");

for(i=0;i<8;i++)

{

RI=0;

while(RI==0)

{

if(rx0==1\&\&rx1==0\&\&rx2==0\&\&rx3==0)//1000---

--->track 1 train a

{

if(condition=='1')

{

m1p=0;

m1n=0;

m2p=0;

```

```

buzzer=0;

}

else

f(rx0=-1\&&rx1==0\&&rx2==1\&&rx3==0)//1010----->track 2 train a

{

if(condition=='2')

{

m1p=0;

m1n=0;

m2p=0;

m2n=0;

buzzer=0;

}

}

else

{

m1p=1;

m1n=0;

m2p=0;

```

```

}

}

rfid[i]=SBUF;

}

lcd_command(0xC0);

lcd_display(rfid);

if(rfid[i-1]=='1')

{

tx0=0;

tx1=1;

tx2=0;

tx3=0;

condition='1';

}

else if(rfid[i-1]=='2')

{

tx0=0;

tx1=1;

tx2=0;

```

```

condition='1';

}

else if(rfid[i-1]=='6')

{

tx0=0;

tx1=1;

tx2=1;

tx3=0;

condition='2';

}

else if(rfid[i-1]=='7')

{

tx0=0;

tx1=1;

tx2=1;

tx3=0;

condition='2';

}

```

}

## 1.2 CODING FOR TRAIN B

include<reg52.h>

include<8lcd.h>

sbit rx0=P1^0;

sbit rx1=P1^1;

sbit rx2=P1^2;

sbit rx3=P1^3;

sbit tx0=P1^4;

sbit tx1=P1^5;

sbit tx2=P1^6;

sbit tx3=P1^7;

sbit buzzer=P2^7;

sbit m1p=P3^4;

sbit m1n=P3^5;

sbit m2p=P3^6;

d main()

```

unsigned char i=0,rfid[16];

unsigned char condition=0;

SCON=0x50;

TMOD=0x20;

TH1=0xFD;

TR1=1;

lcd_init();

lcd_data('S');

m1p=0;

m1n=0;

m2p=0;

m2n=0;

tx0=0;

tx1=0;

tx2=0;

tx3=0;

```

```

while(1)

{

lcd_command(0x80);

lcd_display("RFID CARD NO:");

for(i=0;i<8;i++)

{

RI=0;

while(RI==0)

{

if(rx0=0\&&rx1=1\&&rx2=0\&&rx3==0)//0100----

--->track 1 train b

{

if(condition=='1')

{

m1p=0;

m1n=0;

m2p=0;

m2n=0;

buzzer=0;

```

```

x0=0\&\&rx1=1\&\&rx2=1\&\&rx3=0)/(0110----->track 2 train b

{

if(condition=='2')

{

m1p=0;

m1n=0;

m2p=0;

m2n=0;

buzzer=0;

}

}

else

{

m1p=1;

m1n=0;

m2p=0;

m2n=1;

}

```

```

}

lcd_command(0xC0);

lcd_display(rfid);

if(rfid[i-1]=='1')

{

tx0=1;

tx1=0;

tx2=0;

tx3=0;

condition='1';

}

else if(rfid[i-1]=='2')

{

tx0=1;

tx1=0;

tx2=0;

tx3=0;

condition='1';

}

```

```

{

tx0=1;

tx1=0;

tx2=1;

tx3=0;

condition='2';

}

else if(rfid[i-1]=='7')

{

tx0=1;

tx1=0;

tx2=1;

tx3=0;

condition='2';

}

}

```

}

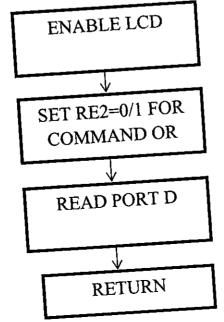

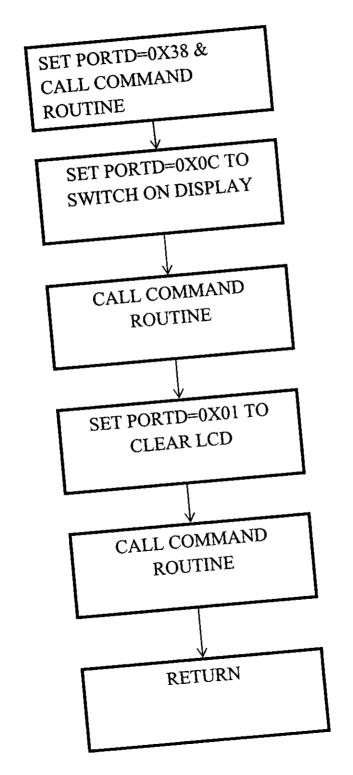

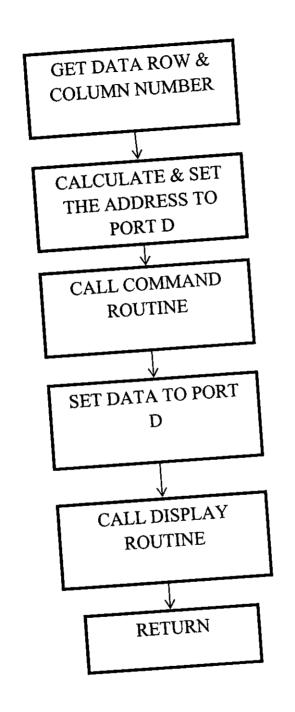

## 11.3 FLOWCHARTS

## LOWCHART OF ENTIRE PROCESS

## ITIALISE SERIAL COMMUNICATION

## SCOMMAND/DISPLAY LCD

## ITIALISING LCD

## RITE LCD

## . CONCLUSION

Thus, if the concept of Anti-collision in Trains using RFID is mplemented, system is accurate and does not raise any false alarms. Some of the number of Train collisions can be reduced or avoided altogether. The Automated important advantages that can be obtained by implementing this system are listed below.

- Man power error is reduced due to automation

- Cost of system is low compared to other systems

## **FUTURE EXPANSION**

RF Transceivers can be placed at level crossings, as the train approaches, are gates of the level cross can close automatically without the need for any nanual labour. The presences of trains entering and exiting the gates can also be etected consequently.

RFID tags will be able to detect the arrival of a train at a particular station and alerts/ buzzers can be sounded to inform the passengers.

The same concept can be used to keep track of the number of trains in a terminal. Since the cost-cutting rate of RFID tags have been enormously significant in the last few years, their usage will go a long way into helping maintaining financial stability as well.

## APPENDIX A

### atures

ompatible with MCS®-51 Products

( Bytes of in-System Programmable (ISP) Flash Memory

- Endurance: 10,000 Write/Erase Cycles

.ov to 5.5V Operating Range

ully Static Operation: 0 Hz to 33 MHz

Three-level Program Memory Lock

256 x 8-bit Internal RAM

32 Programmable I/O Lines

Three 16-bit Timer/Counters

Eight Interrupt Sources

Full Duplex UART Serial Channel

Low-power idle and Power-down Modes

Interrupt Recovery from Power-down Mode

**Watchdog Timer**

Dual Data Pointer

Power-off Flag

Fast Programming Time

• Flexible ISP Programming (Byte and Page Mode)

Green (Pb/Halide-free) Packaging Option

The AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8K bytes of in-system programmable Flash memory. The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.

The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

8-bit Microcontroller with 8K Bytes In-System **Programmable** Flash

AT89S52

## onfigurations

### ead PDIP

```

40 VCC

(T2) P1.0 ☐ 1

39 P0.0 (AD0)

(T2 EX) P1.1 디2

38 P0.1 (AD1)

P1.2 13

37 P0.2 (AD2)

P1.3 ☐ 4

36 P0.3 (AD3)

P1.4口5

35 D PO.4 (AD4)

(MOSI) P1.5 다 6

34 P0.5 (AD5)

(MISO) P1.6 다 7

33 P0.6 (AD6)

(SCK) P1.7 디 8

32 P0.7 (AD7)

RST ☐ 9

31 D EAVPP

(RXD) P3.0 4 10

30 ALE/PROG

(TXD) P3.1 ☐ 11

29 PSEN

(INTO) P3.2 ☐ 12

28 P2.7 (A15)

(INT1) P3.3 ☐ 13

(T0) P3.4 ☐ 14

27 P2.6 (A14)

26 P2.5 (A13)

(T1) P3.5 15

25 P2.4 (A12)

(WR) P3.6 □ 16

24 P2.3 (A11)

(RD) P3.7 17

23 P2.2 (A10)

XTAL2 18

22 P2.1 (A9)

XTAL1 d 19

口P2.0 (A8)

GND 120

```

### 4-lead TQFP

## 2.3 44-lead PLCC

## n Description

VCC

Supply voltage.

**GND**

Ground.

#### Port 0

Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs.

Port 0 can also be configured to be the multiplexed low-order address/data bus during accesse to external program and data memory. In this mode, P0 has internal pull-ups.

Port 0 also receives the code bytes during Flash programming and outputs the code bytes du ing program verification. External pull-ups are required during program verification.

#### Port 1

Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 output buffers c sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the int nal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled I will source current  $(I_{\rm IL})$  because of the internal pull-ups.

In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count in (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, as shown in the following

Port 1 also receives the low-order address bytes during Flash programming and verification.

| ort Pin  | Alternate Functions  Times/Counter 2), clock-out                                                          |

|----------|-----------------------------------------------------------------------------------------------------------|

| 21.0     | T2 (external count input to Timer/Counter 2), clock-out                                                   |

| <br>P1.1 | T2 (external count input to Timerres  T2EX (Timer/Counter 2 capture/reload trigger and direction control) |

| P1.5     | MOSI (used for In-System Programming)                                                                     |

| P1.6     | MISO (used for In-System Programming)                                                                     |

| P1.7     | SCK (used for In-System Programming)                                                                      |

### Port 2

..5

Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffe sink/source four TTL inputs. When 1s are written to Port 2 pins, they are pulled high by the nal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pul

will source current  $(I_{\rm IL})$  because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory a ing accesses to external data memory that use 16-bit addresses (MOVX @ DPTR) application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2

sives the bigh-order address bits and some control signals during Flash p Function Register.

#### ort 3

Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current  $(I_{\rm IL})$  because of the pull-ups.

Port 3 receives some control signals for Flash programming and verification.

Port 3 also serves the functions of various special features of the AT89S52, as shown in the following table.

| Port Pin | Alternate Functions                    |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

|          | INTO (external interrupt 0)            |

| P3.2     | INT1 (external interrupt 1)            |

| P3.3     | T0 (timer 0 external input)            |

| P3.4     | T1 (timer 1 external input)            |

| P3.5     | WR (external data memory write strobe) |

| P3.6     | RD (external data memory read strobe)  |

| P3.7     | HD (external data memory               |

#### **RST**

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRI bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of DISRTO, the RESET HIGH out feature is enabled.

### ALE/PROG

Address Latch Enable (ALE) is an output pulse for latching the low byte of the address dur accesses to external memory. This pin is also the program pulse input (PROG) during Fla

In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped ing each access to external data memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled I Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode

#### SEN

Program Store Enable (PSEN) is the read strobe to external program memory.