# SPACE VECTOR MODULATION FOR NINE SWITCH INVERTER

# A Project Report

Submitted by

S.BARATHI - 0710105010

M.POORNIMADEVI - 0710105036

S.PRASITTHAA - 0710105038

E.C.THANIKAIVELAN - 0710105055

in partial fulfillment for the award of the degree

of

Bachelor of Engneering

in

**Electrical and Electronics Engineering**

# DEPARTMENT OF ELECTRICAL &ELECTRONICS ENGINEERING KUMARAGURU COLLEGE OF TECHNOLOGY COIMBATORE – 641006 APRIL - 2011

#### **BONAFIDE CERTIFICATE**

Certified that this project report entitled "SPACE VECTOR MODULATION FOR

NINE SWITCH CONVERTER" is the bonafide work of

S.Barathi Register No. 0710105010

M.Poornima Devi Register No. 0710105036

S.Prasitthaa Register No. 0710105038

E.C.Thanikaivelan Register No. 0710105055

who carried out the project work under my supervision.

Signature of the Head of the Department

Dr. RANI THOTTUNGAL HOD (EEE)

Signature of the Supervisor

( melhays la

Mr. C. UDHAYA SHANKAR

Certified that the candidates with university Register No. 0710105055.......was examined in project via voce examination held on. 19:4:20!!.....

Internal Examiner

External Examiner

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING KUMARAGURU COLLEGE OF TECHNOLOGY, COIMBATORE - 641006

(An Autonomous Institute Affiliated To Anna University, Coimbatore)

#### **ABSTRACT**

This paper presents a Nine-switch converter for industrial and traction application with Space Vector Modulation (SVM) scheme for induction motor drives. Developed algorithm has several advantages like z source boosting up, wide speed operation range, good dynamics, low torque ripples, constant switching and low sampling frequency. The SVM can be used in various applications like electric vehicles, where field-weakening operation is required. Drive operation ranges including field-weakening region are described. Selected experimental results are measured on the induction motor drive, which illustrates steady state and dynamic performances of the developed system.

#### ACKNOWLEDGEMENT

It is our bounden duty to thank contribution made in one from or the other be the individuals we hereby acknowledge.

We express our heart-felt gratitude and thanks to Dean / HoD of Electrical and Electronics Engineering, **Dr. Rani Thottungal**, for encouraging us and for being with us right from beginning of the project and fine tuning us at every step.

We wish to place on record our deep sense of gratitude and profound thanks to our guide Mr. C.Udhaya Shankar, Assistant Professor, Electrical and Electronics Engineering Department, for his valuable guidance, constant encouragement and continuous support rendered throughout the project.

We are also thankful to all the reviewers for their valuable comments and encouragement.

Last but not least, we extend our sincere thanks to all the teaching and non-teaching staff who have contributed their ideas and encouraged us for completing the project.

# **CONTENTS**

| TITLE       |                                            | PAGE NO |

|-------------|--------------------------------------------|---------|

| Bonafide    | Certificate                                | i       |

| Abstract    |                                            | ii      |

| Acknowl     | edgement                                   | iii     |

| Contents    |                                            | iv      |

| List of fig | gures                                      | vi      |

| СНАРТІ      | ER 1: INTRODUCTION                         |         |

| 1.1         | General                                    | 1       |

| 1.2         | Objective                                  | 3       |

| 1.3         | Organization of the report                 | 4       |

| СНАРТІ      | ER 2: PULSE WIDTH MODULATION               |         |

| 2.1         | General                                    | 5       |

| 2.2         | Implementation in nine switch inverter     | 7       |

| 2.3         | Forming switching sequence                 | 9       |

| СНАРТЕ      | CR 3: IMPEDANCE SOURCE NETWORK             | •       |

| 3.1         | Introduction                               | 16      |

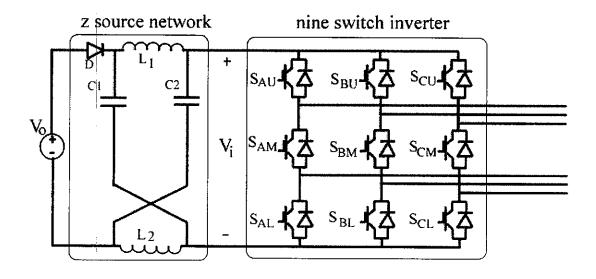

| 3.2         | Implementation of impedance source network | 17      |

# **CHAPTER 4: SIMULATION AND RESULTS**

| 4.1       | Simulation                      | 22 |

|-----------|---------------------------------|----|

| 4.2       | Simulink model                  | 23 |

| 4.3       | Simulation Results              | 24 |

| CHAPTER 5 | : HARDWARE IMPLEMENTATION       |    |

| 5.1       | Overall block diagram           | 26 |

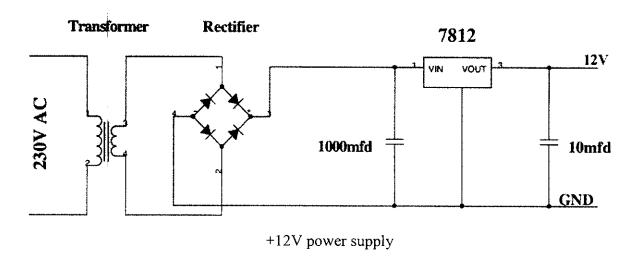

| 5.2       | Power supply circuit            | 27 |

| 5.3       | Inverter bridge                 | 29 |

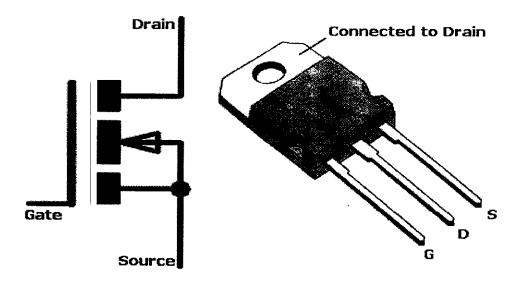

| 5.4       | MOSFET features                 | 30 |

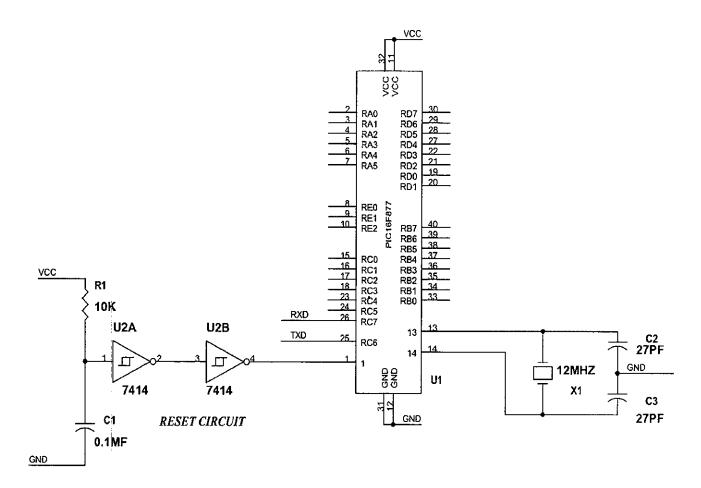

| 5.5       | PIC microcontroller             | 32 |

| 5.5.1     | Tact switch                     | 32 |

| 5.5.2     | Features of PIC microcontroller | 32 |

| 5.5.3     | Control circuit                 | 34 |

| 5.6       | Experimental setup              | 35 |

| 5.7       | Hardware results                | 35 |

| CHAPTER O | 6: CONCLUSION AND SCOPE         |    |

| 6.1       | Conclusion                      | 36 |

| 6.2       | Scope for future improvement    | 36 |

| REFERENC  | ŒS                              | 37 |

| APPENDIX  | A PIC 16F877A CODING            |    |

| APPENDIX  | B PIC 16F877A DATASHEET         |    |

| APPENDIX  | C IRF840 DATASHEET              |    |

# LIST OF FIGURES

| Figure | Title                                            | Page |

|--------|--------------------------------------------------|------|

| 2.1    | Carrier based PWM                                | 7    |

| 2.2    | Carrier based PWM for nine switch converter      | 8    |

| 2.3    | Nine-switch inverter                             | 9    |

| 2.4    | Available switching vectors for 110 upper active | 11   |

| 2.5    | Space vector diagram for nine switch inverter    | 12   |

| 2.6    | Space vector switching sequence                  | 14   |

| 2.7    | SVM with reduced THD                             | 15   |

| 3.1    | Z-source network                                 | 16   |

| 3.2    | Nine-switch z-source inverter switching sequence | 19   |

| 3.3    | Switching sequence for reduced switching         | 21   |

| 4.1    | Simulink diagram                                 | 23   |

| 5.1    | Overall block diagram                            | 26   |

| 5.2    | Power supply                                     | 27   |

| 5.3    | Nine switch with impedance network               | 29   |

| 5.4    | Schematic of MOSFET                              | 31   |

| 5.5    | Tact switch                                      | 32   |

| 5.6    | PIC control circuit                              | 34   |

# INTRODUCTION

# 1.1 GENERAL

Nowadays, there is a demand of power supply. As an electrical engineer, it is necessary to design system with low cost, reduced losses and higher efficiency. This paper proposes nine-switch converter with single controller, rather than using 12 switches for operation of drives separately. In electrical vehicle drives mostly AC motors are used.

It is because of its well known advantages like simplicity, reliability, lack of mechanical commutator and brushes, ability to work under unfriendly conditions (dust, humidity, etc.) and low cost. The most popular AC machines are induction motors - IM and permanent magnet synchronous motors - PMSM. These motors can be supplied from power electronics converters (like VSI inverters).

Therefore, are used in various applications like hybrid electric vehicles HEV, public transport, machine tools drives, etc. Some of these applications have to work above nominal speed. This is essential in EV and public transport drives. High-speed operation can be achieved either by increasing supply voltage (not always possible) or by field weakening. In the IM field-weakening operation can be easily performed.

The above requirements are not fulfilled in scalar control, where only angular speed (frequency) and magnitudes of flux, current and voltage vectors are adjusted. Instantaneous positions of these vectors are not controlled.

Therefore, space vector control methods have been strongly developed. In this case, not only angular speed (frequency) and magnitudes of flux, current and voltage vectors, but also instantaneous position of these vectors is controlled. This ensures excellent dynamic and stable steady state operation of space vector control methods.

## 1.2 OBJECTIVE

The aim of this project is to develop the space vector modulation (SVM) of nine-switch inverter and nine-switch-z-source inverter. Develop a method to increases the sum of modulation indices up to 15% in contrast with the conventional scheme in which the sum of modulation indices is less than the one by using Z source dc/dc inverter.

Also, in order to further reduce the cost of power devices and also thermal heat effect and to reduce the number of semiconductor switching, specific SVM switching pattern is presented. This feature will be advantageous for high-power inverter applications where cost and efficiency are key decision factors.

# 1.3 ORGANISATION OF THE REPORT

This report has been organized into the following chapters.

Chapter 1: Gives the introduction and objective of the project and the way the various chapters are organized.

Chapter 2: Focuses on the basic principle of PWM based inverters and operation of nine-switch inverter and implementation of space vector modulation in it.

Chapter 3: Explains the impedance source inverter and its advantages over the conventional inverters

Chapter 4: Describes the simulation model and results.

Chapter 5: Describes the hardware implementation of the project.

Chapter 6: Concludes the project with the scope for improvement.

# PULSE WIDTH MODULATION

## 2.1 GENERAL:

The advent of the transformerless multilevel inverter topology has brought forth various pulse width modulation (PWM) schemes as a means to control the switching of the active devices in each of the multiple voltage levels in the inverter. The most efficient method of controlling the output voltage is to incorporate pulse width modulation control (PWM control) within the inverters.

In this method, a fixed dc input voltage is supplied to the inverter and a controlled ac output voltage is obtained by adjusting the on and off periods of the inverter devices. Voltage-type PWM inverters have been applied widely to such fields as power supplies and motor drivers.

This is because: (1) such inverters are well adapted to high-speed self turn-off switching devices that, as solid-state power converters, are provided with recently developed advanced circuits; and (2) they are operated stably and can be controlled well.

The PWM control has the following advantages:

- (i) The output voltage control can be obtained without any additional components.

- (ii) With this type of control, lower order harmonics can be eliminated or minimized along with its output voltage control.

- (iii) The filtering requirements are minimized as higher order harmonics can be filtered easily.

The commonly used PWM control techniques are:

- (a) Sinusoidal pulse width modulation (sin PWM)

- (b) Space vector PWM

The performance of each of these control methods is usually judged based on the following parameters: a) Total harmonic distortion (THD) of the voltage and current at the output of the inverter, b) Switching losses within the inverter, c) Peak-to-peak ripple in the load current, and d) Maximum inverter output voltage for a given DC rail voltage.

From the above all mentioned PWM control methods, the Space vector modulation (SVM) is applied in the proposed inverter since it has various advantages over other techniques. SVM inverters provide an easy way to control amplitude, frequency and harmonics contents of the output voltage.

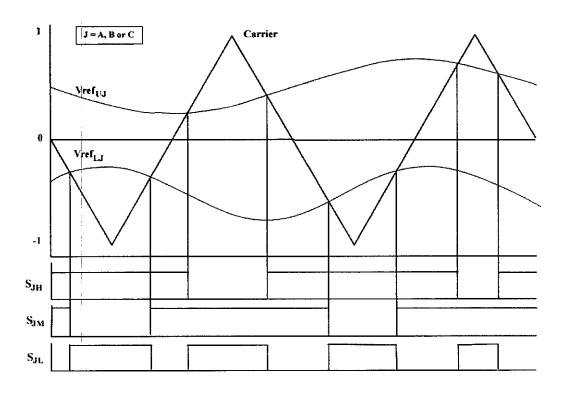

# 2.2 IMPLEMENTATION IN NINE-SWITCH INVERTER:

The carrier-based PWM control method for nine-switch inverter is shown in Fig2.1. There are two reference signals (upper and lower) for each phase. The upper and lower reference signals are related to upper and lower outputs respectively. The gate signal for upper switch of a leg is generated by comparing the carrier signal and upper reference signal of the related phase (VrefUJ).

Similarly, the gate signal for lower switch is generated from the carrier signal and lower reference signal of the related phase (VrefLJ). The gate signal for mid switch is generated by the logical XOR of the gate signals for upper and lower switches. With this method, always two switches are ON in each leg.

Fig2.1 Carrier based PWM

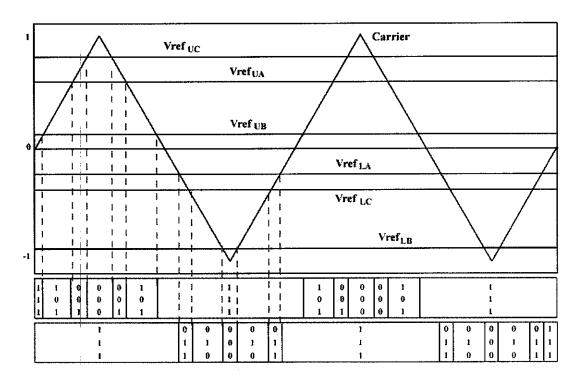

The fig 2.2 shows carrier-based PWM method switching vectors. There are six vectors in each switching cycle for both outputs: two nonzero vectors, one zero vector 0 0 0, two nonezero vectors and one zero vector 1 1 1 {two active—short zero (0 0 0)—two active—long zero (1 1 1)}. In an active vector, output load is connected to the dc input source, while in a zero vector, the output load is short-circuited. When one of the outputs has an active or short zero (0 0 0) vector, the other output has long zero (1 1 1) vector.

Fig2.2 Carrier based PWM for nine-switch converter

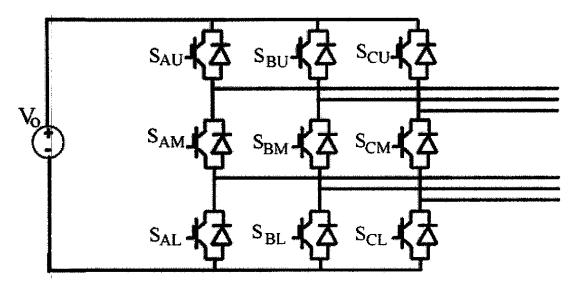

### 2.3 FORMING SWITCHING SEQUENCE

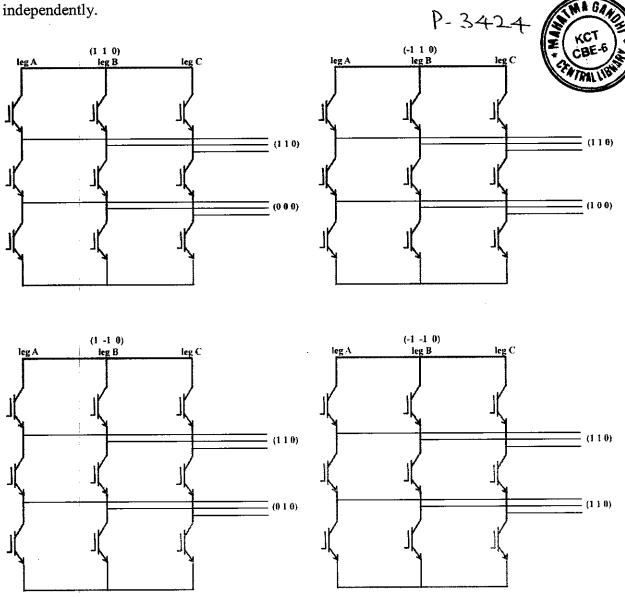

In regard to Fig2.3, each leg can be in three different semi-conductors ON-OFF position. These position can be called {1}, {0}, and {-1}, as is illustrated in Table I. In Table I, J refers to leg A, B, or C and U, M, L refers to upper, mid, and lower semiconductor, respectively.

Fig 2.3 Nine-switch inverter

The combination of switching vector of both outputs in Fig 2.2 creates a specific sequence as shown in table 2. This sequence is used to design SVM method. There are 12 vectors in each switching cycle: {two upper active (Vau)-zero (Vz)-two upper active (Vau)-zero (Vz)-two lower active (Val)-zero (Vz) two lower active (Val)-zero (Vz). The switching vectors are listed in Table II. The vectors V1 –V6 are upper active vectors. In these vectors, the upper output is in active state, and the lower output is in zero state. There is an inverse logic in lower active vectors (V7–V12). In zero vectors (V13–V15), both outputs are in zero state.

Table 1. Semiconductors ON-OFF position of legs

|    | Sju | Ѕјм | Sjl |

|----|-----|-----|-----|

| 1  | ON  | OFF | ON  |

| 0  | OFF | ON  | ON  |

| -1 | ON  | ON  | OFF |

Table 2. SVM switching vectors

| Vector | Leg A | Leg B | Leg C | Туре         |

|--------|-------|-------|-------|--------------|

| 1      | 1     | 0     | 0     |              |

| 2      | 1     | 1     | 0     | 1            |

| 3      | 0     | 1     | 0     | Upper Active |

| 4      | 0     | 1     | 1     | Opper Active |

| 5      | 0     | 0     | 1     |              |

| 6      | 0     | 0     | 1     |              |

| 7      | -1    | 1     | 1     |              |

| 8      | -1    | -1    | 1     | -            |

| 9      | 1     | -1    | 1     | Lower Active |

| 10     | 1     | -1    | -1    | Lowel Active |

| 11     | 1     | 1     | -1    |              |

| . 12   | -1    | 1     | -1    |              |

| 13     | 1     | 1     | 1     |              |

| 14     | 0     | 0     | 0     | Zero         |

| 15     | -1    | -1    | -1    |              |

Table 2 does not include all possible variations of switching states  $\{1\}$ ,  $\{0\}$ , and  $\{-1\}$ . Since a vector including  $\{-1\}$  and  $\{0\}$  connects both loads to the dc source at the same time, the loads lose their independence and they cannot have independent frequencies. This is the reason for avoiding a vector that includes combinations of  $\{-1\}$  and  $\{0\}$ .

In none of the switching vectors as listed in Table 2, both outputs are not in an active state at the same time. However, in vectors including both  $\{-1\}$  and  $\{0\}$  such as  $\{-1, 1, 0\}$ , both outputs are in active state. These vectors are ignored because there are not all combinations of active vectors for both outputs.

For example, if upper output be in active vector (1 1 0), lower output can be in vectors (000),(100),(010),or(110)as shown in Fig 2.4. However, vectors (0 1 1), (0 0 1), and (1 0 1) are not available for lower output. Therefore, outputs cannot be controlled independently.

Fig 2.4 Available switching vectors of nine-switch inverter while upper output is in active vector (1 1 0).

#### 2.3.1 DETERMING THE VECTORS

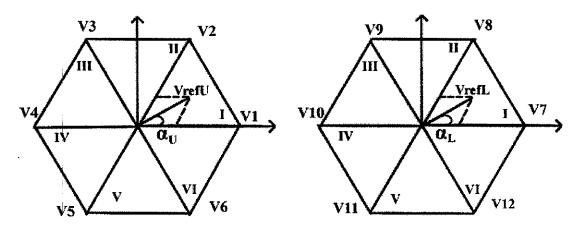

To determine the proper active vectors, two space vector diagrams are proposed as shown in Fig. 2.5.

Fig 2.5 Space vector diagrams for nine-switch inverter. (a) Upper output. (a) Lower output.

The diagrams (a) and (b) are used to determine the upper and lower active vectors, respectively. The SVM active vectors are determined with regard to location of upper reference signal (V refU) in the diagram (a) and lower reference signal (V ref L) in the diagram (b). The reference signals for the upper and lower outputs are defined as

$$V_{refU} = V_{refU} \alpha_U$$

(1)

$$V_{refL} = V_{refL} \alpha_L$$

(2)

$$\alpha_{U} = 2\pi f_{U}t + \varphi_{U} \qquad (3)$$

$$\alpha_L = 2\pi f_L t + \phi_L \tag{4}$$

where  $f_U$ ,  $f_L$  are the frequencies, and  $\phi_U$ ,  $\phi_L$  are the phases. All zero vectors V13, V14, and V15 can be used for zero states. The type of zero vectors can be selected based on control goals and optimizations such as minimum number of semiconductor switchings.

The switching time intervals of vectors are calculated as

$$T1 = (\sqrt{3}/2) * (m_U * T * \sin \pi - \alpha_U)$$

(5)

T2=

$$(\sqrt{3}/2)*m_U*T*\sin(\alpha_U)$$

(6)

$$T3 = (\sqrt{3}/2) m_L *T * \sin(\pi/3 - \alpha_L)$$

(7)

$$T4 = (\sqrt{3}/2) m_L *T * \sin(\alpha_L)$$

(8)

$$T0 = T - T1 - T2 - T3 - T4$$

(9)

Where T1, T2 are the time interval of upper active vectors, T3, T4 are time of lower active vectors, T0 is time of zero vectors and T is switching period. mU and mL are upper and lower modulation indices, respectively, and defined by

$$m_U = 2V_{refU}/Vi \qquad (10)$$

$$m_L = 2V_{refL}/Vi$$

(11)

The sum of active vector time intervals must be less or equals to T. Thus, the following constrain must be satisfied

$$(m_U + m_L) \le \sqrt{3}/2 \approx 1.155$$

(12)

Equation (12) clearly indicates that in the proposed SVM scheme, sum of modulation indices increases about 15%—a very important feature to provide higher torque for a given input dc-voltage. In the case of washing machines, the above capability translates to higher machine capacity (in terms of cloth load) at high spin speed (e.g., 1800 r/min)—an important product feature in marketplace.

A switching vector sequence for the proposed SVM is shown in Fig. 2.7. This switching sequence is developed to reduce the number of semiconductor switching. The zero vectors are placed just between two upper and lower active vectors. In upper active vectors, legs are in state {1} or {0} and in lower active vectors, legs are in state {1} or {-1}. If V13 zero vector is placed between the active vectors, minimum number of switching is required. While if V14 or V15 zero vectors are used, number of switching is increased.

V<sub>REF U</sub> in I, III, or V

# V<sub>REF L</sub> in I, III, or V

| V <sub>13</sub>   | $V_{AU2}$      | V <sub>AU1</sub> | V <sub>AU1</sub> | $V_{AU2}$      | V <sub>13</sub> | V <sub>AL1</sub> | $V_{AL2}$      | $V_{AL2}$      | V <sub>ALI</sub> | V <sub>13</sub> |

|-------------------|----------------|------------------|------------------|----------------|-----------------|------------------|----------------|----------------|------------------|-----------------|

| T <sub>0</sub> /2 | T <sub>2</sub> | $T_1$            | Tı               | T <sub>2</sub> | T <sub>0</sub>  | T <sub>3</sub>   | T <sub>4</sub> | T <sub>4</sub> | T <sub>3</sub>   | $T_0/2$         |

V<sub>REF U</sub> in II, IV, or VI

V<sub>REF L</sub> in I, III, or V

| $V_{13}$          | V <sub>AU1</sub> | $V_{AU2}$      | $V_{AU2}$      | V <sub>AU1</sub> | V <sub>13</sub> | V <sub>AL1</sub> | $V_{AL2}$      | $V_{AL2}$      | $V_{AL1}$      | V <sub>13</sub>   |

|-------------------|------------------|----------------|----------------|------------------|-----------------|------------------|----------------|----------------|----------------|-------------------|

| T <sub>0</sub> /2 | $T_1$            | T <sub>2</sub> | T <sub>2</sub> | T <sub>1</sub>   | T <sub>0</sub>  | T <sub>3</sub>   | T <sub>4</sub> | T <sub>4</sub> | T <sub>3</sub> | T <sub>0</sub> /2 |

V<sub>REF U</sub> in I, III, or V

V<sub>REF L</sub> in II, IV, or VI

| $V_{13}$          | $V_{AU2}$      | V <sub>AU1</sub> | V <sub>AU1</sub> | $V_{AU2}$      | V <sub>13</sub> | $V_{AL2}$      | V <sub>ALI</sub> | V <sub>ALI</sub> | $V_{AL2}$      | V <sub>13</sub>   |

|-------------------|----------------|------------------|------------------|----------------|-----------------|----------------|------------------|------------------|----------------|-------------------|

| T <sub>0</sub> /2 | T <sub>2</sub> | $T_1$            | $T_1$            | T <sub>2</sub> | $T_0$           | T <sub>4</sub> | T <sub>3</sub>   | T <sub>3</sub>   | T <sub>4</sub> | T <sub>0</sub> /2 |

V<sub>REF U</sub> in II, IV, or VI

V<sub>REF L</sub> in II, IV, or VI

| V <sub>13</sub> | $V_{AU1}$      | $V_{AU2}$      | $V_{AU2}$      | $V_{AU1}$ | V <sub>13</sub> | $V_{AL2}$      | $V_{AL1}$      | V <sub>AL1</sub> | $V_{AL2}$      | V <sub>13</sub>   |

|-----------------|----------------|----------------|----------------|-----------|-----------------|----------------|----------------|------------------|----------------|-------------------|

| $T_0/2$         | T <sub>1</sub> | T <sub>2</sub> | T <sub>2</sub> | $T_1$     | T <sub>0</sub>  | T <sub>4</sub> | T <sub>3</sub> | T <sub>3</sub>   | T <sub>4</sub> | T <sub>0</sub> /2 |

Fig 2.6 Space-vector modulation sequence vectors

There are two odd active vectors (V1, V3, V5, V8, V10, and V12) and two even active vectors (V2, V4, V6, V7, V9, and V11) in a switching sequence. In an even active vector, two legs are in state {1}, while in an odd active vector only one leg is in state {1}. If even active vectors are placed next to V13, number of switching will be reduced even more as in fig 2.6.

#### 2.3.2 TOTAL HORMONIC DISTORTION REDUCTION:

There are other possible switch generation methods too, e.g., a switching method, to reduce THD. To minimize THD, active vectors for each output should be centrally placed within the switching period. Fig. 2.7 shows a switching vector sequence that shifts active vector into center of switching period, hence reducing THD. In this sequence, zero vectors are inserted between active vectors. In Fig.2.7 V14 is inserted between upper active vectors and V15 is inserted between lower active vectors.

$V_{REFU}$  in I, III, or V

V<sub>REF</sub> L in I, III, or V

| $V_{AU2}$      | $V_{AU1}$ | V <sub>14</sub> | V <sub>AUI</sub> | $V_{AU2}$      | $V_{AL1}$      | V <sub>AL2</sub> | $V_{15}$ | V <sub>AL2</sub> | V <sub>AL1</sub> |

|----------------|-----------|-----------------|------------------|----------------|----------------|------------------|----------|------------------|------------------|

| T <sub>2</sub> | Tı        | T <sub>0</sub>  | $T_1$            | T <sub>2</sub> | T <sub>3</sub> | T <sub>4</sub>   | $T_0$    | T <sub>4</sub>   | T <sub>3</sub>   |

V<sub>REF U</sub> in II, IV, or VI

V<sub>REF L</sub> in I, III, or V

| V <sub>AUI</sub> | V <sub>AU2</sub> | V <sub>14</sub> | $V_{AU2}$      | $V_{AU1}$ | $V_{AL1}$      | V <sub>AL2</sub> | V <sub>15</sub> | $V_{AL2}$      | V <sub>AL1</sub> |

|------------------|------------------|-----------------|----------------|-----------|----------------|------------------|-----------------|----------------|------------------|

| $T_1$            | T <sub>2</sub>   | T <sub>0</sub>  | T <sub>2</sub> | Ti        | T <sub>3</sub> | T <sub>4</sub>   | T <sub>0</sub>  | T <sub>4</sub> | T <sub>3</sub>   |

V<sub>REF U</sub> in I, III, or V

V<sub>REF L</sub> in II, IV, or VI

| $V_{AU2}$      | V <sub>AU1</sub> | V <sub>14</sub> | $V_{AU1}$ | $V_{AU2}$ | $V_{AL2}$      | V <sub>AL1</sub> | V <sub>15</sub> | $V_{ALl}$      | $V_{AL2}$      |

|----------------|------------------|-----------------|-----------|-----------|----------------|------------------|-----------------|----------------|----------------|

| T <sub>2</sub> | T <sub>1</sub>   | T <sub>0</sub>  | $T_1$     | $T_2$     | T <sub>4</sub> | $T_3$            | $T_0$           | T <sub>3</sub> | T <sub>4</sub> |

V<sub>REF U</sub> in II, IV, or VI

V<sub>REF L</sub> in II, IV, or VI

| V <sub>AUI</sub> | $V_{AU2}$      | $V_{14}$ | $V_{AU2}$ | $V_{AU1}$ | $V_{AL2}$      | $V_{ALl}$      | $V_{15}$       | $V_{AL1}$      | $V_{AL2}$      |

|------------------|----------------|----------|-----------|-----------|----------------|----------------|----------------|----------------|----------------|

| $T_1$            | T <sub>2</sub> | $T_0$    | $T_2$     | $T_1$     | T <sub>4</sub> | T <sub>3</sub> | T <sub>0</sub> | T <sub>3</sub> | T <sub>4</sub> |

Fig 2.7 SVM with reduced THD

# IMPEDANCE SOURCE NETWORK

#### 3.1 INTRODUCTION

#### TRADITIONAL SOURCE INVERTERS

Traditional source inverters are Voltage Source Inverter and Current Source Inverter. The input of Voltage Source Inverter is a stiff dc voltage supply, which can be a battery or a controlled rectifier both single phase and three-phase voltage source inverter are used in industry. The switching device can be a conventional MOSFET, Thyristor, or a power transistor.

Voltage source inverter is one which the dc source has small or negligible impedance. In other words a voltage source inverter has stiff dc source voltage at its input terminals. A current-fed inverter or current source inverter is fed with adjustable dc current source. In current source inverter the load does not affect output current waves.

#### **Z-SOURCE INVERTER:**

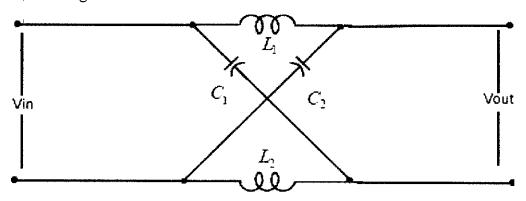

Z-Source Inverter (ZSI) is a novel inverter type that utilizes the traditional VSI or Current-Source Inverter (CSI) to achieve both buck and boost operations on voltage or current during inversion. The hardware circuit only requires two inductors, two capacitors and a diode in addition to the VSI. Furthermore, a significant change in switching pattern is also required to achieve this objective. The resulting single-stage boost type inverter saves cost, size and complexity over the conventional two-stage power-conditioning unit.

Fig 3.1 Z-source network

#### ADVANTAGES OF IMPEDANCE SOURCE NETWORK:

- The impedance source inverter concept can be applied to all ac-ac, dc-dc, ac-dc, dc-ac power conversion.

- The output voltage range is not limited.

- The impedance source inverter is used as a buck-boost inverter

- The impedance source inverter is immune to EMI noise

- The cost is low.

- It provides the buck-boost function by two stage power conversion.

#### 3.2 IMPLEMETATION OF Z SOURCE NETWORK:

The nine-switch-z-source inverter is shown in Fig. 2. This inverter has an extra z-source network including two inductors (L1 and L2), two capacitors (C1 and C2) and a diode (D). The z-source network is similar to a dc/dc boost converter.

$$V_i=BV_O$$

(13)

where Vo is input dc voltage and Vi is output of z-source network.

B is known as boost factor and is given by following equation:

$$B=1/(1-2(Tsc/T))$$

(14)

where T<sub>sc</sub> is shoot-through time. In the shoot-through times, the output of z-source network is shorted through the switches of the inverter. During shoot-through state, since the inverter (output of z-source network) is shorted, inverter cannot have an active vector. Therefore a shoot-through state can only occur when the inverter has a zero state.

Table 3. Shoot through vectors of nine-switch z-source inverter

| Vector | Leg A | Leg B | Leg C |

|--------|-------|-------|-------|

| 16     | 2     | 2     | 2     |

| 17     | 2     | 2     | 0     |

| 18     | 2     | 2     | 1     |

| 19     | 2     | 2     | -1    |

| 20     | 2     | 0     | 2     |

| 21     | 2     | 1     | 2     |

| 22     | 2     | -1    | 2     |

| 23     | 0     | 2     | 2     |

| 24     | 1     | 2     | 2     |

| 25     | -1    | 2     | 2     |

| 26     | 2     | 0     | 0     |

| 27     | 2     | 1     | 1     |

| 28     | 2     | -1    | -1    |

| 29     | 0     | 2     | 0     |

| 30     | 1     | 2     | 1     |

| 31     | -1    | 2     | -1    |

| 32     | 0     | 0     | 2     |

| 33     | 1     | 1     | 2     |

| 34     | -1    | -1    | 2     |

Table 4. On-Off position of semiconductor switches in state (2)

|   | S <sub>JU</sub> | S <sub>JM</sub> | S <sub>JL</sub> |

|---|-----------------|-----------------|-----------------|

| 2 | ON              | ON              | ON              |

Table 3 shows all the vectors that the inverter includes zero state and the z-source network has a shoot-through state. These vectors are known as shoot-through vectors. There is a new state (state {2}) in Table 3. The ON-OFF position of switches of a leg in state {2} is shown in Table 4. All vectors of Table III can be used for generating a shoot-through state.

| <b>T</b> 7 | •    | •  | TTT |    | * * |

|------------|------|----|-----|----|-----|

| $V_{REF}$  | 111n | I. | Ш.  | or | V   |

V<sub>REF L</sub> in I, III, or V

| V <sub>13</sub> | $V_{\text{SCU}}$   | $V_{AU2}$          | $V_{AUI}$      | $V_{AUI}$        | $V_{AU2}$        | $V_{\text{SCU}}$   | $V_{13}$        | $V_{\text{SCL}}$   | $V_{AL1}$           | $V_{AL2}$        | $V_{AL2}$        | $V_{AL1}$        | $V_{\text{SCL}}$   | $V_{13}$        |

|-----------------|--------------------|--------------------|----------------|------------------|------------------|--------------------|-----------------|--------------------|---------------------|------------------|------------------|------------------|--------------------|-----------------|

|                 | T <sub>SC</sub> /2 | T <sub>2</sub>     | $T_1$          | $T_1$            | $T_2$            | T <sub>SC</sub> /2 | $T_0$           | $T_{SC}/2$         | T <sub>3</sub>      | T <sub>4</sub>   | T <sub>4</sub>   | T <sub>3</sub>   | T <sub>SC</sub> /2 | 2               |

|                 |                    | V <sub>REF U</sub> | in II,         | IV, or           | VI               |                    |                 | $V_{RE}$           | <sub>F L</sub> in I | , III, o         | r V              |                  |                    |                 |

| V <sub>13</sub> | $V_{\text{SCU}}$   | V <sub>AUI</sub>   | $V_{AU2}$      | V <sub>AU2</sub> | V <sub>AU1</sub> | V <sub>SCU</sub>   | V <sub>13</sub> | V <sub>SCL</sub>   | V <sub>AL1</sub>    | V <sub>AL2</sub> | V <sub>AL2</sub> | V <sub>ALi</sub> | V <sub>SCL</sub>   | V <sub>13</sub> |

| 7               | T <sub>SC</sub> /2 | $T_1$              | T <sub>2</sub> | T <sub>2</sub>   | T <sub>1</sub>   | T <sub>SC</sub> /2 | T <sub>0</sub>  | T <sub>SC</sub> /2 | T <sub>3</sub>      | T <sub>4</sub>   | $T_4$            | T <sub>3</sub>   | T <sub>SC</sub> /2 | 2               |

V<sub>REF U</sub> in I, III, or V

V<sub>REF L</sub> in II, IV, or VI

| $V_{13}$ | $V_{SCU}$          | $V_{AU2}$      | $V_{AU1}$      | $V_{AU1}$      | $V_{AU2}$      | $V_{SCU}$          | $V_{13}$ | $V_{\text{SCL}}$   | $V_{AL2}$      | $V_{AL1}$      | $V_{AL1}$      | $V_{\text{AL2}}$ | $V_{SCL}$          | V <sub>13</sub> |

|----------|--------------------|----------------|----------------|----------------|----------------|--------------------|----------|--------------------|----------------|----------------|----------------|------------------|--------------------|-----------------|

| 7        | T <sub>SC</sub> /2 | T <sub>2</sub> | T <sub>1</sub> | T <sub>1</sub> | T <sub>2</sub> | T <sub>SC</sub> /2 | To       | T <sub>SC</sub> /2 | T <sub>4</sub> | T <sub>3</sub> | T <sub>3</sub> | T <sub>4</sub>   | T <sub>SC</sub> /2 | 2               |

# V<sub>REF U</sub> in II, IV, or VI

# V<sub>REF L</sub> in II, IV, or VI

| V <sub>13</sub> V <sub>SCU</sub>        | V <sub>AU1</sub> | $V_{AU2}$      | $V_{AU2}$      | V <sub>AU1</sub> | $V_{SCU}$          | V <sub>13</sub> | $V_{SCL}$          | $V_{AL2}$      | $V_{ALl}$ | $V_{AL1}$      | $V_{AL2}$      | V <sub>SCL</sub>   | V <sub>13</sub> |

|-----------------------------------------|------------------|----------------|----------------|------------------|--------------------|-----------------|--------------------|----------------|-----------|----------------|----------------|--------------------|-----------------|

| T <sub>SC</sub> /2<br>T <sub>0</sub> /2 | $T_1$            | T <sub>2</sub> | T <sub>2</sub> | Ti               | T <sub>SC</sub> /2 | T <sub>o</sub>  | T <sub>SC</sub> /2 | T <sub>4</sub> | Т3        | T <sub>3</sub> | T <sub>4</sub> | T <sub>SC</sub> /2 | 7               |

Fig 3.2. Nine-switch z-source inverter SVM with reduced switching

Fig 3.2 shows a SVM vector sequence for nine-switch inverter with reduced number of switching. The sequence is a modified version of Fig. 8. Two shoot-through vectors are placed in both sides of zero vector (V13). Here, the shoot-through vector close to upper active vector is called upper shoot-through vector ( $V_{SCU}$ ) and the shoot-through vector close to lower active vector is called lower shoot-through vector ( $V_{SCL}$ ). All vectors listed in Table 3 can be used as the upper and lower shoot-through vectors.

However, vectors V27, V30, and V33 are preferred because those vectors have only one state {2} and need less switching. As shown in Fig.10, even active vectors are placed close to shoot-through vectors.

In even active vectors, two legs are in state {1} and one leg is in state {0} or {-1}. On other hand, in shoot-through vectors V27, V30, and V33, two legs are in state {1} and one leg is in state {2}. To reduce the number of switching, the two legs in state {1} must have the same state in an even active vector and shoot-through vector close to it. Table 5 can be used for shoot-through vectors selection.

Table5.Determining upper and lower shoot-through vector with reduced number of switching

| Section of V <sub>refU</sub> | V <sub>scu</sub> | Section of V <sub>refL</sub> | $V_{SCL}$       |

|------------------------------|------------------|------------------------------|-----------------|

| I                            | V <sub>33</sub>  | I                            | V <sub>27</sub> |

| II                           | V <sub>33</sub>  | II                           | $V_{30}$        |

| III                          | V <sub>27</sub>  | III                          | V <sub>30</sub> |

| IV                           | V <sub>27</sub>  | IV                           | $V_{33}$        |

| V                            | V <sub>30</sub>  | V                            | V <sub>33</sub> |

| VI                           | V <sub>30</sub>  | VI                           | V <sub>27</sub> |

Table 6. Determining upper and lower shoot-through vector with reduced THD

| Section of V <sub>refU</sub> | V <sub>SCU</sub> | Section of V <sub>refL</sub> | V <sub>SCL</sub> |  |

|------------------------------|------------------|------------------------------|------------------|--|

| I                            | V <sub>26</sub>  | I                            | V <sub>34</sub>  |  |

| II                           | V <sub>29</sub>  | II                           | V <sub>34</sub>  |  |

| III                          | V <sub>29</sub>  | III                          | V <sub>28</sub>  |  |

| IV                           | V <sub>32</sub>  | IV                           | V <sub>28</sub>  |  |

| V                            | V <sub>32</sub>  | V                            | V <sub>31</sub>  |  |

| VI                           | V <sub>26</sub>  | VI                           | V <sub>31</sub>  |  |

For reducing THD, switching sequence shown in Fig.3.3 is developed for nine-switch-z-source inverter. Similar to Fig.3.2, zero vectors and shoot-through vectors are inserted between similar active vectors. Table VI can be used for shoot-through vector selection with reduced THD.

V<sub>RFF II</sub> in I, III, or V  $V_{REFL}$  in I, III, or V  $\overline{

m V}_{

m AU1}$  $\overline{V_{AL2}}$  $\overline{V}_{AL1}$  $V_{AU2}$  $V_{SCU}$  $V_{14}$  $V_{SCU}$  $V_{AUI}$  $m V_{AU2}$  $V_{SCL}$  $V_{AL2}$  $V_{15}$  $V_{SCL}$  $m V_{ALI}$ T<sub>sc</sub>/2  $T_{SC}/2$  $T_{SC}/2$  $T_{SC}/2$  $T_2$  $T_1$  $T_{1} \\$  $T_2$  $T_3$  $T_4$  $T_4$  $T_3$  $T_0$  $T_0$ V<sub>REF U</sub> in II, IV, or VI  $V_{REFL}$  in I, III, or V  $\overline{V_{14}}$  $V_{AL1}$  $\overline{V_{AU2}}$  $V_{AU2}$  $\overline{V_{\mathtt{ALl}}}$  $V_{AU1}$  $\overline{V_{SCL}}$  $V_{AU1}$  $\overline{V}_{SCU}$  $V_{scu}$  $V_{AL2}$  $\overline{V_{SCL}}$  $\overline{V_{15}}$  $V_{AL2}$  $T_{SC}/2$  $T_{SC}/2$  $T_{SC}/2$  $\overline{T_{SC}/2}$  $T_1$  $T_2$  $T_2$  $\mathbf{T}_1$  $T_3$  $T_{4}$  $T_4$  $T_{3}$  $T_0$  $T_0$ V<sub>REF U</sub> in I, III, or V V<sub>REF L</sub> in II, IV, or VI  $V_{AU1}$  $V_{\text{AU2}}$  $V_{14}$  $V_{AL2}$  $V_{AU2}$  $V_{SCU}$  $V_{\text{SCU}}$  $V_{\mathsf{AUI}}$  $V_{ALl}$  $V_{SCL}$  $\overline{V_{15}}$  $V_{\mathsf{SCL}}$  $V_{\mathsf{ALI}}$  $V_{AL2}$  $T_{SC}/2$  $T_{SC}/2$  $T_{SC}/2$  $T_{SC}/2$  $T_2$  $T_1$  $T_{l}$  $T_{\text{\tiny 2}}$  $T_4$  $T_3$  $T_3$  $T_4$  $T_0$  $T_0$  $V_{REFU}$  in II, IV, or VI V<sub>REF L</sub> in II, IV, or VI  $\overline{V}_{AU2}$  $V_{\text{AUI}}$  $V_{AU1}$  $V_{SCU}$  $\overline{\mathrm{V}_{14}}$  $V_{\text{SCU}}$  $\overline{V}_{AU2}$  $\overline{V}_{AL2}$  $\overline{V_{AL1}}$  $V_{SCL}$  $\overline{V_{15}}$  $V_{\mathtt{SCL}}$  $\overline{V}_{AL1}$  $\overline{V}_{AL2}$  $T_{SC}/2$  $T_{SC}/2$  $T_{SC}/2$  $T_{SC}/2$  $T_{1} \\$  $T_2$  $T_{\text{\tiny 2}}$  $T_1$  $T_{4} \\$  $T_3$  $T_3$  $T_4$  $T_0$  $T_0$

Fig 3.3 Nine-switch z-source inverter SVM with reduced switching

# SIMULATION AND RESULTS

The simulations for the project are carried out in Matlab simulink software. The simulation results verify that the proposed project reduces the number of switches used for controlling two three phase loads. The inverter is designed in the model window and the control system is designed as a separate subsystem with the following parameters.

# 4.1 SIMULATION PARAMETERS

| Parameter                | Value |

|--------------------------|-------|

| Switching frequency      | 3 khz |

| Frequency for upper load | 25 hz |

| Frequency for lower load | 50 hz |

| Lf                       | 1 mh  |

| Cf                       | 20 μF |

# 4.2 SIMULINK DIAGRAM

**NINE SWITCH INVERTER** В To see ₽ LOWER SWITCHG MIDDLE SWITCHG UPPER SWITCH A LOWER SWITCHA H UPPER SWITCHS

UPPER SWITCHS control system Centinuous

Fig 4.1 Simulink Diagram

# **4.3 SIMULATION RESULTS:**

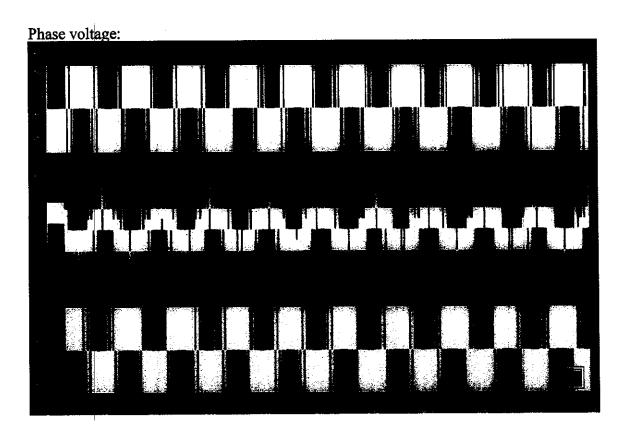

Line voltage:

# Filtered Waveform:

# CHAPTER 5

# **CHAPTER 5**

# HARDWARE IMPLEMENTATION

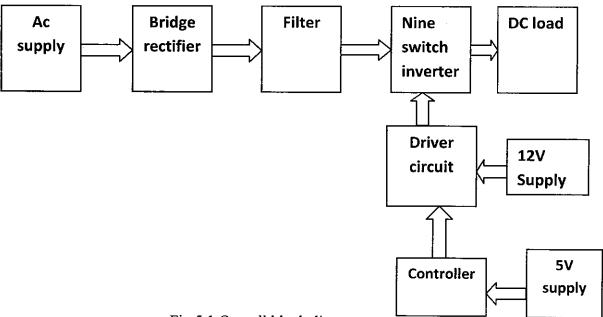

# 5.1 OVERALL BLOCK DIAGRAM

Fig 5.1 Overall block diagram

The circuit consists of the following blocks

- Input transformer

- Power supply circuit

- Impedance source

- Inverter bridge

- PIC microcontroller

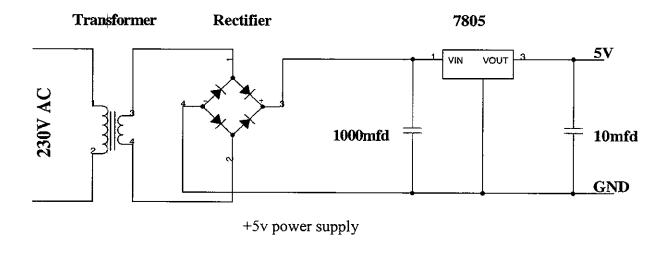

#### **5.2 POWER SUPPLY:**

Since all electronics circuits work only with low DC voltage, a power supply unit is needed to provide the approximate voltage supply. This unit consists of transformer, receiver, filter and regulator. AC voltage typically 230 V is connected to a step down transformer. The output of transformer is given to the bridge rectifier and then a simple capacitor filter to produce a DC voltage initially filters it. This DC voltage is given to regulator, which gives a constant DC voltage.

Fig 5.2 Power supply

#### **5.2.1 TRANSFORMER**

A transformer is a static piece of which electric power in one circuit is transformed into electric power of same frequency in another circuit. It can raise or lower the voltage in a circuit but with corresponding decrease or increase in current. Step down transformer have been used for providing a necessary supply for the electronic circuit.

#### 5.2.2 RECTIFIER

Rectifier to be used is bridge rectifier. It is now available in a single entity. It is IR BR 6840. Here IR stands for INTERNATIONAL RECTIFIER that is the company manufacturing the product. BR stands for the bridge rectifier.6 stands for it's rating that is 600V, 6A. Rectifier is used for converting AC into pulsating DC. Here instead of using the DC source such as battery we are using the rectifier because those sources have fewer lifetimes.

Certain parameters of the IR BR 6840 are given below:

Maximum peak reverse voltage = 800V

Maximum RMS voltage = 560 V

Maximum DC blocking voltage = 500V

#### **5.2.3 FILTER**

Filtering should be done in order to reduce the harmonics and ripples. For this purpose we use capacitors for the filtering. They are rated at 100 V. Here output voltage from rectifier is 100 V. The capacitors are used in two arms. They share this voltage equally. The capacitors are therefore rated at 1000  $\mu$ f/100 V. Each of the capacitors share 50 V. The capacitors is electrolytic in nature.

#### 5.2.4 REGULATOR

Regulator IC units contains the circuitry for reference source, comparator amplifier, control device and overload protection in a single IC. Although the internal construction of the IC is somewhat different from that described one, the external operation is the same. IC units provide regulation of a fixed positive voltage, a fixed

negative voltage or an adjustable set voltage. A power supply can be built using a transformer connected to the AC supply line to step the AC voltage to the desired amplitude. It is then rectified filtered with the capacitor and finally regulating the DC voltage using an IC regulator. The regulators can be selected for operation with load currents from hundreds of milli amperes to tones of amperes, corresponding to power rating from milli watts to tens of watts.

## **5.3 NINE SWITCH INVERTER:**

A dual output inverter has been developed using only nine semiconductor switches (see Fig. 1). This inverter is known as nine-switch inverter. The nine-switch inverter is composed of two conventional inverters with three common switches. The switches used are MOSFETs.

In nine-switch inverter, sum of modulation index of two outputs must be less than or equal to one. Therefore, voltage amplitude of outputs is smaller, compared with two separate inverters. To remedy this problem, this paper proposes using an impedance source (z-source) network in front of nine-switch inverter as a dc/dc boost converter. Z-source network was used as front-end boost converter.

Fig 5.3 Nine switch inverter with impedance network

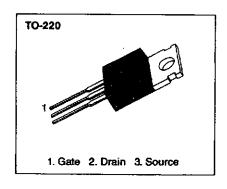

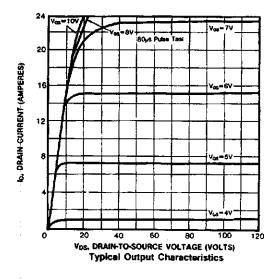

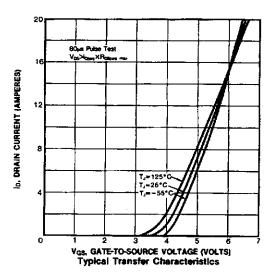

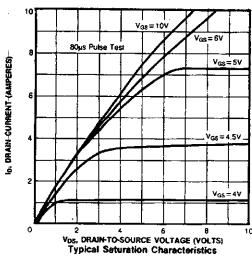

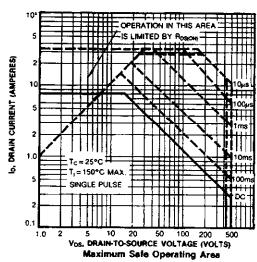

#### **5.4 MOSFET:**

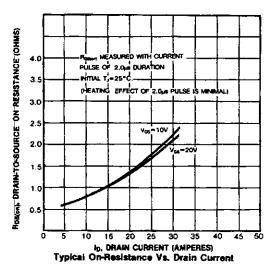

MOSFET used is IRF P250. It's voltage rating is 250V, current rating is 20A.It has following advantages:

- (1)Extremely high dv/dt capability

- (2) Very low intrinsic capacitances

- (3) Gate charge is minimized.

- (4)Fast switching is possible.

- (5)Ease of paralleling with other MOSFET.

The distance between the pins of IRFP460 is optimal and hence it meets the safety requirements. Certain absolute maximum ratings of various parameters are given below:

Drain current at  $V_{GS} = 10V$  is 20A Gate to Source voltage  $V_{GS} = 20V$ dv/dt of IRFP6840 is = 3.5V/ns

It is used in following applications:

- (1) High current switching.

- (2)Uninterruptible power supply.

- (3)Inverters such as this system

The internal schematic diagram of IRFP46 is shown in following figure.4.5

Fig 5.4 Schematic of a MOSFET

#### 5.5 PIC MICROCONTROLLER:

The 16F877A PIC microcontroller is used for generating the pulses of the desired pulse width for driving the MOSFETs, by fixing either the frequency or voltage so that the MOSFETS are turned ON and OFF in the desired sequence.

The port C is used as the output port that gives the gate signals, whereas the port B is used as the input port, which receives the signals from the tact switch.

#### 5.5.1 TACT SWITCH

A tact switch is type of switch that is only on when the button is pressed. Four of these switches are used to give input to the micro controller regarding choosing the speed of the motor. One of these four switches is a reset switch that is used to stop the motor.

Fig 5.5 Tact switch

# 5.2 FEAT URES OF THE PIC 16F877A MICROCONTROLLER

- High-performance RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two cycle

- Operating speed: DC 20 MHz clock input

DC - 200 ns instruction cycle

- Up to 8K x 14 words of Flash Program Memory,

- Up to 368 x 8 bytes of Data Memory (RAM)

Up to 256 x 8 bytes of EEPROM data memory

- Pin out compatible to the PIC16C73/74/76/77

- Interrupt capability (up to 14 internal/external

- Eight level deep hardware stack

- · Direct, indirect, and relative addressing modes

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC Oscillator for reliable operation

- Programmable code-protection

- Power saving SLEEP mode

- Selectable oscillator options

- Low-power, high-speed CMOS EPROM/EEPROM technology

- Fully static design

- In-Circuit Serial Programming (ICSP) via two pins

- Only single 5V source needed for programming capability

- In-Circuit Debugging via two pins

- Processor read/write access to program memory

- Wide operating voltage range: 2.5V to 5.5V

- High Sink/Source Current: 25 mA

- Commercial and Industrial temperature ranges

- Low-power consumption:

- ⇒ 2mA typical @ 5V, 4 MHz

- $\Rightarrow$  20mA typical @ 3V, 32 kHz

- ⇒ 1mA typical standby current

## 5.5.3 PIC 16F877A BASED CONTROL CIRCUIT

Fig 5.6 Pic Controller Circuit

# **5.6 EXPERIMENTAL SETUP**

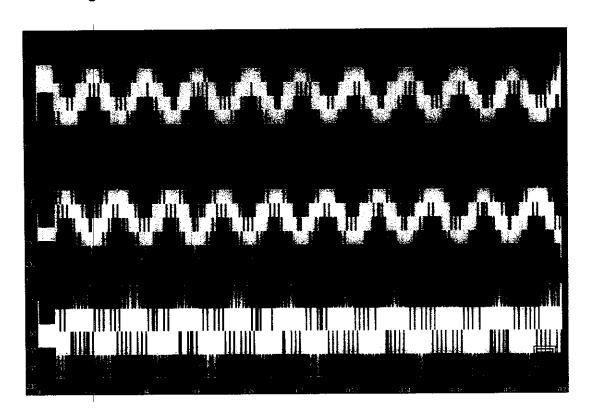

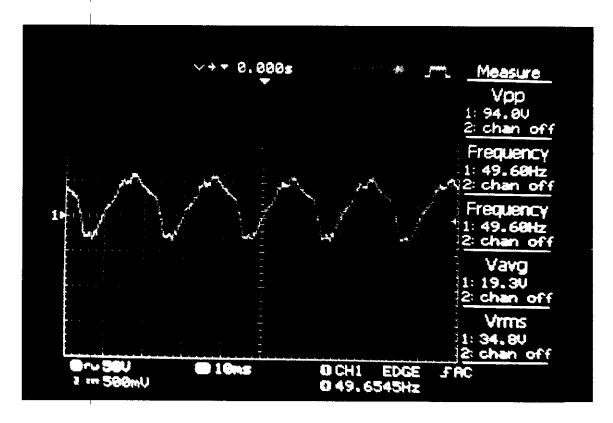

## **5.7 HARDWARE OUTPUT:**

# CHAPTER 6

## **CHAPTER 6**

# CONCLUSION AND SCOPE FOR FUTURE DEVELOPMENT

#### **CONCLUSION:**

- Switching sequence of the proposed SVM is composed of the upper active vectors, the lower active vectors and the zero vectors. The upper and lower active vectors are determined.

- For the impedance source inverter SVM algorithm is developed to reduce the number of switching and number of semiconductor switches.

- The performance of the proposed SVM was verified using computer simulation and it was validated using experimental data.

# SCOPE FOR FUTURE IMPROVEMENT:

Further in future an SVM algorithm for reduced total harmonic distortion can be implemented.

#### REFERENCE

- T. Kominami and Y. Fujimoto, "A novel nine-switch inverter for independent control of two three-phase loads," in Proc. IEEE Ind. Appl. Soc. Annu. Conf. (IAS), 2007, pp. 2346–2350.

- C. Liu, B. Wu, N. Zargari, and D. Xu, "A novel three-phase three-leg AC/AC converter using nine IGBTs," IEEE Trans. Power Electron., vol. 24, no. 5, pp. 1151–1160, May 2009.

- C. Liu, B.Wu, N. Zargari, and D.Xu, "A novel nine-switch PWM rectifier inverter topology for three-phase UPS applications," J. Eur. Power Electron. (EPE), vol. 19, no. 2, pp. 1–10, 2009.

- K. Oka, Y. Nozawa, R. Omata, K. Suzuki, A. Furuya, and K. Matsuse,

"Characteristic comparison between five-leg inverter and nine-switch inverter,"

in Proc. Power Convers. Conf., Nagoya, 2007, pp. 279–283.

- F<sub>1</sub> Z. Peng, "Z-source inverter," IEEE Trans. Ind. Appl., vol. 39, no. 2,pp. 504–510, Mar./Apr. 2003

# **APPENDI**

## APPENDIX

# 16F877A PIC MICROCONTROLLER CODING AND DETAILS

```

Code:

#include<pic.h>

//PIC16F Header File Declaration

#include<stdio.h>

//Embedded C Header File Decleration

#include "delay.c"

//Subroutine Declaration

__CONFIG(0x3f71);

//IC Initialization

void main()

//Main Program

{

RBPU=0;

TRISB=0XFF;

TRISC=0x00;

PORTC=0;

PORTB=0xFF:

while(1)

// Continuous Operation

{

PORTC=0x11;

//Generate first part signal

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x12;

//Generate second Part Signal 2

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x06;

//Generate third part signal

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x09;

//Generate fourth part signal 4

DelayMs(2);

//Call Delay

DelayUs(500);

```

```

PORTC=0x0C;

//Generate fifth part signal

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x1C;

//Generate sixth part signal 6

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x01;

//Generate seventh part signal 7

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x0C;

//Generate eighth part signal 8

DelayMs(2);

//Call Delay

DelayUs(500);

PORTC=0x1C;

//Generate ninth part signal 9

DelayMs(2);

//Call Delay

DelayUs(500);

}

```

}

#### APPENDIX B

# PIC MICROCONTROLLER

The microcontroller that has been used for this project is from PIC series. PIC microcontroller is the first RISC based microcontroller fabricated in CMOS (complementary metal oxide semiconductor) that uses separate bus for instruction and data allowing simultaneous access of program and data memory.

The main advantage of CMOS and RISC combination is low power consumption resulting in a very small chip size with a small pin count. The main advantage of CMOS is that it has immunity to noise than other fabrication techniques.

EEPROM, EPROM, FLASH etc. are some of the memories of which FLASH is the most recently developed. Technology that is used in pic16F877 is flash technology, so that data is retained even when the power is switched off. Easy Programming and Erasing are other features of PIC 16F877.

#### PIN DIAGRAM OF PIC 16F877

# **TABLE \$PECIFICATIONS**

| DEVICE     | PROGRAM FLASH | DATA<br>MEMORY | DATA EEPROM |

|------------|---------------|----------------|-------------|

| PIC 16F877 | 8K            | 368 Bytes      | 256 Bytes   |

## PERIPHERAL FEATURES:

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during sleep

Via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules

Capture is 16-bit, max resolution is 12.5 ns,

Compare is 16-bit, max resolution is 200 ns.

PWM max. Resolution is 10-bit

- 10-bit multi-channel Analog-to-Digital converter

- Synchronous Serial Port (SSP) with SPI. (Master Mode) and I2C. (Master/Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with

9- Bit addresses detection.

- Brown-out detection circuitry for Brown-out Reset (BOR).

#### **FEATURES**

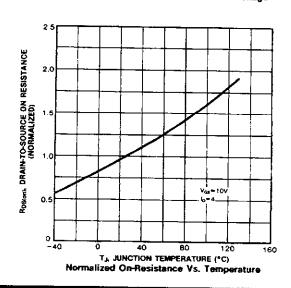

- · Lower Ros(on)

- · Improved inductive ruggedness

- · Fast switching times

- Rugged polysilicon gate cell structure

- · Lower input capacitance

- · Extended safe operating area

- · improved high temperature reliability

# **PRODUCT SUMMARY**

| Part Number | Vos  | Ros(on) | ìo   |

|-------------|------|---------|------|

| IRF840      | 500V | 0.85Ω   | 8.0A |

| IRF841      | 450V | 0.85Ω   | 8.0A |

# **ABSOLUTE MAXIMUM RATINGS**

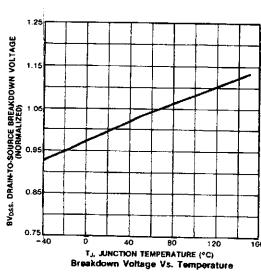

| Characteristic Symbol                                                      |          | IRF840      | IRF841 | Unit |

|----------------------------------------------------------------------------|----------|-------------|--------|------|

| Drain-Source Voltage (1)                                                   | Voss     | 500         | 450    | Vdc  |

| Drain-Gate Voltage (Rgs=1.0MΩ )(1)                                         | VDGR     | 500         | 450    | Vdc  |

| Gate-Source Voltage                                                        | Vas      |             | Vdc    |      |

| Continuous Drain Current Tc=25 °C                                          | al       |             | Adc    |      |

| Continuous Drain Current Tc=100 °C                                         | io io    |             | Adc    |      |

| Drain Current - Pulsed (3)                                                 | \$DM     |             | Adc    |      |

| Gate Current - Pulsed                                                      | lдм      | <u> </u>    | Adc    |      |

| Single Pulsed Avalanche Energy (4)                                         | Eas      |             | mJ     |      |

| Avalanche Current                                                          | las      |             | A      |      |

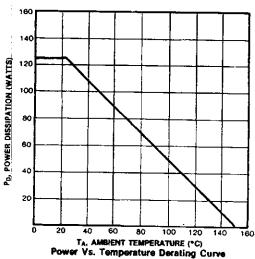

| Total Power Dissipation @ Tc=25 °C                                         |          |             | Watts  |      |

| Derate above 25 °C                                                         | Po       |             | W/°C   |      |

| Operating and Storage Junction Temperature Range                           | TJ, TSTG | -55 to +150 |        | °C   |

| Maximum Lead Temp. for Soldering<br>Purposes, 1/8" from case for 5 seconds | TL       | 3           | °C     |      |

Notes: (1) TJ=25°C to 150°C

(2) Pulse test : Pulse width ≤300 μs, Duty Cycle ≤2%

(3) Repetitive rating: Pulse width limited by max, junction temperature

(4) L=1.4mH, Vod=50V, RG=25Ω , Starting TJ=25°C

# ELECTRICAL CHARACTERISTICS (Tc=25°C unless otherwise specified)

| Symbol  | Characteristic                  | Min            | Тур        | Max          | Units    | Test Conditions                                                                                                         |

|---------|---------------------------------|----------------|------------|--------------|----------|-------------------------------------------------------------------------------------------------------------------------|

|         | Drain-Source Breakdown Voltage  |                |            | <del> </del> |          | - Conditions                                                                                                            |

| BVDSS   | IRF840                          | 500            | -          | -            | v        | Vgs=0V, lo=250µA                                                                                                        |

| [ ]     | IRF841                          | 450            | _          |              | V        | , 100-01, ID-230µA                                                                                                      |

| VGS(th) | Gate Threshold Voltage          | 2.0            | -          | 4.0          | v        | VDS=VGS, ID=250µA                                                                                                       |

| IGSS    | Gate-Source Leakage Forward     | -              | † <u> </u> | 100          | nA       | Vgs=20V                                                                                                                 |

| igss    | Gate-Source Leakage Reverse     | -              | -          | -100         | пA       | Vss=-20V                                                                                                                |

| loss    | Zero Gate Voltage Drain Current |                |            | 250          | μA       | Vos=Max. Rating, Vos=0V                                                                                                 |

|         |                                 | -              | -          | 1000         | μA       | VDS=0.8 Max. Rating, VGS=0V, Tc=125°C                                                                                   |

| RDS(on) | Static Drain-Source On          |                |            |              | <u> </u> | 3, 100-01, 10-120 0                                                                                                     |

|         | Resistance (2)                  | -              | -          | 0.85         | Ω        | Vgs=10V, lo=4.0A                                                                                                        |

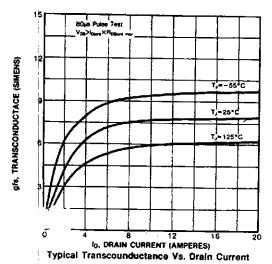

| g#s     | Forward Transconductance (2)    | 4.0            | 6.5        | -            | U        | Vos≥10V, Io=4.0A                                                                                                        |

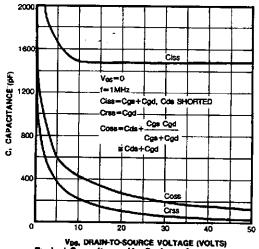

| Ciss    | Input Capacitance               | T -            | 1510       | -            | pF       |                                                                                                                         |

| Coss    | Output Capacitance              | -              | 154        | -            | pF       | Vgs=0V, Vps=25V, f=1.0MHz                                                                                               |

| Crss    | Reverse Transfer Capacitance    | -              | 66         | -            | pF       | 23, 122 (23, 17, 11, 11, 11, 12, 12, 13, 12, 13, 12, 13, 12, 13, 12, 13, 13, 12, 13, 13, 13, 13, 13, 13, 13, 13, 13, 13 |

| td(on)  | Turn-On Delay Time              | -              | 14         | 21           | ns       | Voo=0.5 8Voss, Io=8.0A, Zo=9.1Ω                                                                                         |

| tr      | Rise Time                       | -              | 23         | 35           | ns       | (MOSFET switching times are essentially                                                                                 |

| to(off) | Turn-Off Delay Time             | 1 -            | 49         | 74           | ns       | independent of operating temperature)                                                                                   |

| tr      | Fall Time                       | <del>  -</del> | 20         | 30           | ns       | or operating temperature)                                                                                               |

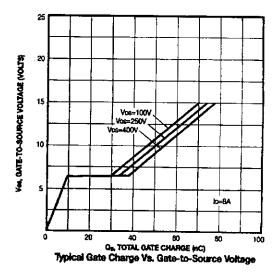

| Cg      | Total Gate Charge               | -              | -          | 74           | nC       | VGS=10V, Io=8.0A, Vos=0.8 Max. Rating                                                                                   |

|         | (Gate-Source Plus Gate-Drain)   |                |            |              |          | (Gate charge is essentially independent of                                                                              |

| Clgs _  | Gate-Source Charge              | -              | 9.0        | - 1          | nC       | operating temperature)                                                                                                  |

| Qgd     | Gate-Drain ("Miller") Charge    | 1 - 1          | 27.0       |              | nC       |                                                                                                                         |

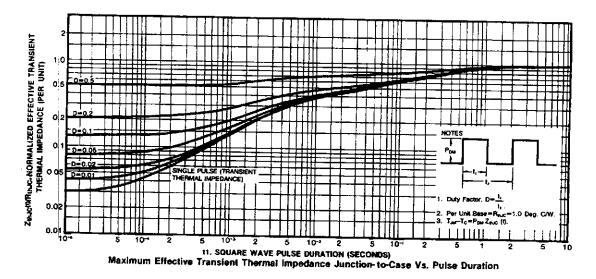

# THERMAL RESISTANCE

| Symbol       | Characteristics     |     | All  | Units | Remark                 |

|--------------|---------------------|-----|------|-------|------------------------|

| Rttuc        | Junction-to-Case    | MAX | 1.0  | KW    | пения к                |

| Rthcs        | Case-to-Sink        | TYP | 0.5  | K/W   | Mounting surface flat, |

| <u> </u>     |                     |     |      |       | smooth, and greased    |

| Rinja Juncti | Junction-to-Ambient | MAX | 62.5 | K/W   | Free Air Operation     |

Notes: (1) T<sub>J</sub>=25°C to 150°C

(2) Pulse test : Pulse width ≤ 300 µs, Duty Cycle ≤ 2%

(3) Repetitive rating: Pulse width limited by max. junction temperature

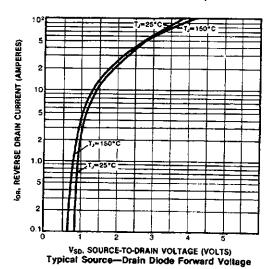

#### **SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS**

| Symbol | Characteristic                            | Min | Тур | Max | Units | Test Conditions                         |  |

|--------|-------------------------------------------|-----|-----|-----|-------|-----------------------------------------|--|

| ls     | Continuous Source Current<br>(Body Diode) | -   | -   | 8.0 | А     | Modified MOSFET symbol showing the      |  |

| Ism    | Pulse Source Current<br>(Body Diode) (3)  | -   | -   | 32  | А     | integral reverse P-N junction rectifier |  |

| Vso    | Diode Forward Voltage (2)                 | -   | -   | 2.0 | ٧     | TJ=25°C, Is=8.0A, Vgs=0V                |  |

| tır    | Reverse Recovery Time                     | -   | 460 | 970 | ns    | Tj=25°C, I=8.0A, dlf/dt=100A/µS         |  |

Notes: (1) TJ=25°C to 150°C

(2) Pulse test : Pulse width ≤300 µs, Duty Cycle ≤2%

(3) Repetitive rating: Pulse width limited by max. junction temperature

SAMSUNG

325

ELECTRONICS

7964142 0028239 944 |

V<sub>06</sub>, DRAIN-TO-SOURCE VOLTAGE (VOLTS)

Typical Capacitance Vs. Drain to Source Voltage

(b. DRAIN CURRENT (AMPERES) 0 <u>L</u> TA, AMBIENT TEMPERATURE (°C) Maximum Drain Current Vs. Case Temperature