## ADVANCED MULTILEVEL INVERTER WITH REDUCED NUMBER OF SWITCHES

#### A PROJECT REPORT

Submitted by

LAKSHMI SHREE SEKAR

0710105029

MADHAN.S

0710105031

SATHIS KUMAR.S

0710105044

**VIGNESH.B**

0710105058

In partial fulfillment of the requirements for the Award of the Degree

01

#### **BACHELOR OF ENGINEERING**

In

#### **ELECTRICAL & ELECTRONICS ENGINEERING**

Under the guidance of

Dr. Rani Thottungal

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

KUMARAGURU COLLEGE OF TECHNOLOGY,

COIMBATORE - 641 049.

**APRIL 2011**

#### BONAFIDE CERTIFICATE

Certified that this project report "ADVANCED MULTILEVEL INVERTER WITH REDUCED NUMBER OF SWITCHES" is the bonafide work of

| LAKSHMI SHREE SEKAR | 0710105029 |

|---------------------|------------|

|---------------------|------------|

MADHAN.S 0710105031

SATHIS KUMAR.S 0710105044

VIGNESH.B 0710105058

who carried out the project work under my supervision

SIGNATURE OF HOD

\_\_\_\_\_\_\_

Dr. Rani Thottungal Electrical and Electronics Engineering,

Kumaraguru College of Technology

Coimbatore - 641049

SIGNATURE OF THE SUPERVISO

Dr. Rani Thottungal

Electrical and Electronics Engineering,

Kumaraguru College of Technology

Coimbatore - 641049

The candidates with University Register Nos.0710105029, 0710105031, 0710105044, 0710105058 was examined by us in the project.

viva-voce examination held on 19/04/2011.

INTERNAL EXAMINER

EXTERNAL EXAMINER

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

KUMARAGURU COLLEGE OF TECHNOLOGY, COIMBATORE - 641049.

An Autonomous Institute Affiliated To Anna University, Coimbatore.

#### **ABSTRACT**

The multilevel inverter is a recent new development in the field of power electronics. The use of the multilevel inverters results in improved power quality. But the number of power semiconductor switches used in the multilevel inverters is very large. This increases the cost of employing these multilevel inverters in electrical drives. So there is a need for reducing the switch count.

Here a new topology of multilevel inverter is used where the multilevel output is obtained by using the minimum number of switches. Here the output can be obtained for any number of levels by increasing the number of sources or capacitors. With the number of switches reduced, this multilevel inverter also gives better a power quality than a normal conventional inverter.

#### CONTENTS

| TITLE         |                                                                           | P.NO |

|---------------|---------------------------------------------------------------------------|------|

|               | FIDE CERTIFICATE                                                          | i    |

|               |                                                                           | ii   |

| ABSTR         |                                                                           | iii  |

|               | OWLEDGEMENT                                                               | iv   |

| CONTE         |                                                                           | vii  |

| LIST O        | OF FIGURES                                                                | 1    |

| CHAP'         | TER 1 INTRODUCTION                                                        | 1    |

| 1.1           | INTRODUCTION                                                              | 1    |

| 1.2           | A LITERATURE SURVEY ON INVERTERS                                          | 9    |

| 1.3           | PROPOSED SYSTEM                                                           | •    |

| 1.4           | ORGANISATION OF THE REPORT                                                | 10   |

|               |                                                                           |      |

| СНА           | PTER 2 MULTILEVEL INVERTER                                                | 11   |

| 2.1           | MULTILEVEL INVERTER                                                       | 11   |

| 2.2           | A LITERATURE SURVEY ON MULTILEVEL INVERTERS                               | 11   |

| 2.3           | PROPOSED MULTILEVEL INVERTER TOPOLOGY                                     | 16   |

| 2.4           | COMPARISION BETWEEN CASCADED H- BRIDGE INVERTER AND THE PROPOSED TOPOLOGY | 19   |

| 2.5           | ADVANTAGES OF THE PROPOSED TOPOLOGY                                       | 20   |

|               |                                                                           |      |

| СНА           | PTER 3 SIMULATION RESULTS                                                 | 21   |

| 3.1           | CONVENTIONAL THREE PHASE INVERTER                                         | 21   |

|               | 3.1.1 Output waveforms                                                    | 21   |

|               | 3.1.2 FFT analysis                                                        | 23   |

| 3.2           | FIVE LEVEL INVERTER                                                       | 29   |

| <i>ـک</i> . ک | 3.1.1 Output waveforms                                                    | 29   |

|               | 3.1.2 FFT analysis                                                        | 31   |

|               | SEVEN LEVEL INVERTER                                                      | 37   |

| 3.3           | PEAEM PEAER INAPPLEM                                                      |      |

### ACKNOWLEDGEMENT

The satisfaction that accompanies the successful completion of any task would be incomplete without mentioning the people who gave us constant guidance and support.

We would like to express our deep sense of gratitude towards our project guide **Dr. RANI THOTTUNGAL**, (Professor and HOD of EEE Department) who guided us throughout our project and encouraged us to successfully complete our work. We express our immense gratitude to her for the immense help and guidance that she provided during the entire course of our project.

We also extend our heartiest thanks to all our staff members and technicians of EEE Department as well as our parents without whom we would have never attained the completion of our work.

|     |                                          | 27 |

|-----|------------------------------------------|----|

|     | 3.1.1 Output waveforms                   | 37 |

|     | 3.1.2 FFT analysis                       | 39 |

| 3.4 | NINE LEVEL INVERTER                      | 45 |

|     | 3.1.1 Output waveforms                   | 45 |

|     | 3.1.2 FFT analysis                       | 47 |

| 3.5 | CONCLUSION                               | 53 |

| СНА | PTER 4 HARDWARE DESCRIPTION              | 54 |

| 4.1 | INTRODUCTION                             | 54 |

| 4.2 | OVERALL BLOCK DIAGRAM                    | 54 |

| 4.3 | POWER SUPPLY CIRCUIT                     | 55 |

| 4.5 | 4.3.1 Transformer                        | 56 |

|     | 4.3.2 Bridge rectifier                   | 56 |

|     | 4.3.3 IC voltage regulators              | 57 |

| 4.4 | H-BRIDGE INVERTER CIRCUIT                | 58 |

| 4.5 | BI-DIRECTIONAL SWITCHING CIRCUIT         | 60 |

| 4.6 | MOSFET DRIVER CIRCUIT                    | 60 |

| 4.7 | OPTOISOLATOR                             | 61 |

| 4.8 | PIC BASED CONTROL CIRCUIT                | 63 |

| 4.9 | HARDWARE RESULTS                         | 65 |

|     | 4.9.1 Hardware prototype                 | 65 |

|     | 4.9.2 Output waveform                    | 66 |

|     | 4.9.3 Total Harmonic Distortion Analysis | 67 |

|     |                                          |    |

| СН  | APTER 5 CONCLUSION                       | 68 |

| 5.1 | CONCLUSION                               | 68 |

| 5.2 | FUTURE SCOPE                             | 68 |

| RE  | FERENCES                                 |    |

| AP  | PPENDIX A                                |    |

|     |                                          |    |

APPENDIX B

#### LIST OF FIGURES

| SERIAL | NAME OF THE FIGURE                                             | PAGE NO |

|--------|----------------------------------------------------------------|---------|

| NUMBER | NAME OF THE FIGURE                                             |         |

| 1.1    | HALF BRIDGE INVERTER                                           | 2       |

| 1.2    | OUTPUT WAVEFORM OF HALF BRIDGE                                 | 2       |

| 1.3    | FULL BRIDGE CONFIGURATION                                      | 3       |

| 1.4    | OUTPUT WAVEFORM OF FULL BRIDGE                                 | 4       |

| 1.5    | THREE PHASE INVERTER                                           | 5       |

| 1.6    | WAVEFORM OF 180 CONDUCTION MODE                                | 6       |

| 1.7    | WAVEFORM OF 120 CONDUCTION MODE                                | 7       |

| 1.8    | GENERALIZED OUTPUT OF MULTILEVEL INVERTER                      | 8       |

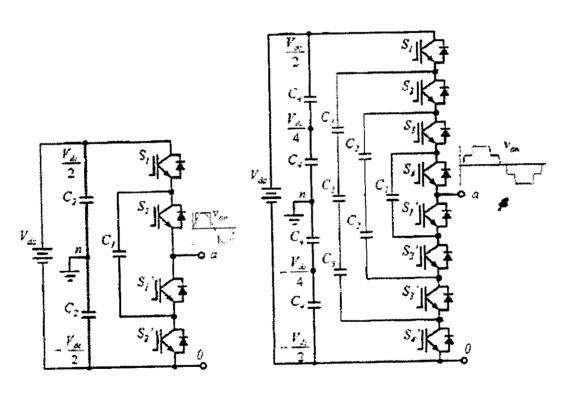

| 2.1    | DIODE CLAMPED INVERTERS                                        | 12      |

| 2.2    | FLYING CAPACITOR INVERTERS                                     | 13      |

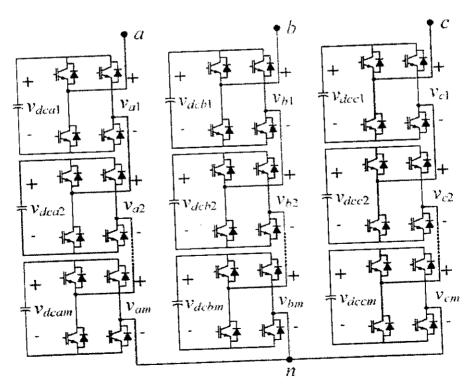

| 2.3    | CASCADED H-BRIDGE MULTILEVEL INVERTER                          | 14      |

| 2.4    | GENERALIZED MULTILEVEL INVERTER                                | 16      |

| 2.5    | POWER CIRCUIT OF THE PROPOSED THREE-PHASE 5-<br>LEVEL INVERTER | 17      |

| 2.6    | OUTPUT PHASE VOLTAGES                                          | 18      |

| 2.7    | OUTPUT LINE VOLTAGE                                            | 18      |

| 2.8    | COMPARISON BETWEEN CASCADED AND PROPOSED                       | 19      |

| 3.1    | CONVENTIONAL THREE PHASE INVERTER- PHASE VOLTAGE               | 21      |

| 3.2    | CONVENTIONAL THREE PHASE INVERTER- LINE VOLTAGE                | 21      |

| l .    |                                                                |         |

| CONVENTIONAL THREE PHASE INVERTER- CURRENT                | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONVENTIONAL THREE PHASE INVERTER- R PHASE FFT            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- Y PHASE FFT            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- B PHASE FFT            | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- RY PHASE FFT           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- YB PHASE FFT           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- BR PHASE FFT           | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- R PHASE<br>CURRENT FFT | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- Y PHASE CURRENT FFT    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONVENTIONAL THREE PHASE INVERTER- B PHASE CURRENT FFT    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- PHASE VOLTAGE                        | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- LINE VOLTAGE                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- CURRENT                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- R PHASE FFT                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- Y PHASE FFT                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- B PHASE FFT                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- RY LINE FFT                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- YB LINE FFT                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- BR LINE FFT                          | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIVE LEVEL INVERTER- R PHASE CURRENT FFT                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | CONVENTIONAL THREE PHASE INVERTER- R PHASE FFT  CONVENTIONAL THREE PHASE INVERTER- B PHASE FFT  CONVENTIONAL THREE PHASE INVERTER- RY PHASE FFT  CONVENTIONAL THREE PHASE INVERTER- RY PHASE FFT  CONVENTIONAL THREE PHASE INVERTER- BR PHASE FFT  CONVENTIONAL THREE PHASE INVERTER- R PHASE FFT  CONVENTIONAL THREE PHASE INVERTER- R PHASE CURRENT FFT  CONVENTIONAL THREE PHASE INVERTER- Y PHASE CURRENT FFT  CONVENTIONAL THREE PHASE INVERTER- B PHASE CURRENT FFT  FIVE LEVEL INVERTER- PHASE VOLTAGE  FIVE LEVEL INVERTER- LINE VOLTAGE  FIVE LEVEL INVERTER- CURRENT  FIVE LEVEL INVERTER- R PHASE FFT  FIVE LEVEL INVERTER- B PHASE FFT  FIVE LEVEL INVERTER- B PHASE FFT  FIVE LEVEL INVERTER- RY LINE FFT  FIVE LEVEL INVERTER- YB LINE FFT  FIVE LEVEL INVERTER- YB LINE FFT  FIVE LEVEL INVERTER- BR LINE FFT |

| 3.24 | FIVE LEVEL INVERTER- B PHASE CURRENT FFT  | 36 |

|------|-------------------------------------------|----|

| 3.25 | SEVEN LEVEL INVERTER- PHASE VOLTAGE       | 37 |

| 3.26 | SEVEN LEVEL INVERTER- LINE VOLTAGE        | 37 |

| 3.27 | SEVEN LEVEL INVERTER- CURRENT             | 38 |

| 3.28 | SEVEN LEVEL INVERTER- R PHASE FFT         | 39 |

| 3.29 | SEVEN LEVEL INVERTER- Y PHASE FFT         | 39 |

|      |                                           | 40 |

| 3.30 | SEVEN LEVEL INVERTER- B PHASE FFT         | 41 |

| 3.31 | SEVEN LEVEL INVERTER- RY LINE FFT         | 41 |

| 3.32 | SEVEN LEVEL INVERTER- YB LINE FFT         | 42 |

| 3.33 | SEVEN LEVEL INVERTER- BR LINE FFT         |    |

| 3.34 | SEVEN LEVEL INVERTER -R PHASE CURRENT FFT | 43 |

| 3.35 | SEVEN LEVEL INVERTER -Y PHASE CURRENT FFT | 43 |

| 3.36 | SEVEN LEVEL INVERTER -B PHASE CURRENT FFT | 44 |

| 3.37 | NINE LEVEL INVERTER -PHASE VOLTAGE        | 45 |

| 3.38 | NINE LEVEL INVERTER –LINE VOLTAGE         | 45 |

| 3.39 | NINE LEVEL INVERTER -CURRENT              | 46 |

| 3.40 | NINE LEVEL INVERTER –R PHASE FFT          | 47 |

| 3.41 | NINE LEVEL INVERTER -Y PHASE FFT          | 47 |

| 3.42 | NINE LEVEL INVERTER -B PHASE FFT          | 48 |

| 3.43 | NINE LEVEL INVERTER –RY LINE FFT          | 49 |

| 3.44 | NINE LEVEL INVERTER -YB LINE FFT          | 49 |

| 3.45 | NINE LEVEL INVERTER –BR LINE FFT          | 50 |

|      |                                           |    |

# **CHAPTER**

# CHAPTER 1 INTRODUCTION

#### 1.1 INTRODUCTION

An inverter is an electrical device that converts direct current (DC) to alternating current (AC); the converted AC can be at any required voltage and frequency with the use of appropriate transformers, switching, and control circuits. Solid-state inverters have no moving parts and are used in a wide range of applications, from small switching power supplies in computers, to large electric utility high-voltage direct current applications that transport bulk power. Inverters are commonly used to supply AC power from DC sources such as solar panels or batteries.

They are of two types

- 1. Single phase inverters

- 2. Three phase inverters

## 1.2 A LITERATURE SURVEY ON INVERTERS

As per literature these are different types of inverters existing in the current system. The general description of widely used inverters is explained below.

#### HALF BRIDGE INVERTERS:

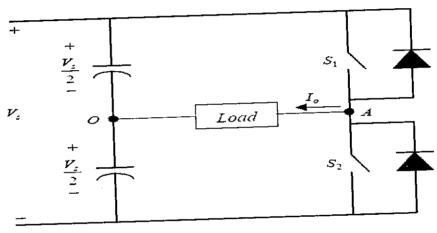

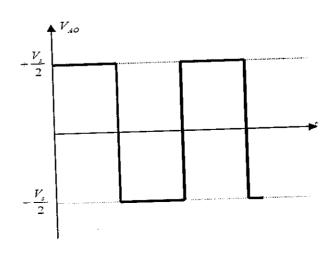

Switch-mode dc-to-ac inverters used in ac power supplies and ac motor drives where the objective is to produce a sinusoidal ac output whose magnitude and frequency can both be controlled. Practically, we use an inverter in both single-phase and three phase ac systems. A half-bridge is the simplest topology, which is used to produce a two level square-wave output waveform. A center-tapped voltage source supply is needed in such a topology. It may be possible to use a simple supply with two well-matched capacitors in series to provide the center tap. The full-bridge topology is used to synthesize a three-level square-wave output waveform. The half-bridge and full-bridge configurations of the single-phase voltage source inverter are shown in Fig. 1.1 and 1.3, respectively.

A single-phase half-bridge inverter, only two switches are needed. To avoid shoot-through fault, both switches are never turned on at the same time. S1 is turned on and S2 is turned off to give a load voltage,  $AO\ V$  in Fig. 1.1, of  $/\ 2\ s\ +V$ . To complete one cycle, S1 is turned off and S2 is turned on to give a load voltage,  $AO\ V$ , of  $/\ 2\ s\ -V$ . In full bridge configuration, turning on S1 and S4 and turning off S2 and S3 give a voltage of VS between point A and B (AB V) in Fig. 1.1, while turning off S1 and S4 and turning on S2 and S3 give a voltage of VS between

Fig 1.1. Half bridge inverter

Fig 1.2. Output waveform of half bridge

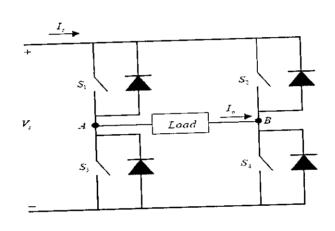

#### **FULL BRIDGE INVERTER:**

The smallest number of voltage levels for a multilevel inverter using cascaded inverter with SDCSs is three. To achieve a three-level waveform, a single full-bridge inverter is employed. Basically, a full-bridge inverter is known as an H-bridge cell, which is illustrated in Fig. 1.3. The inverter circuit consists of four main switches and four freewheeling diodes.

Fig 1.3. Full bridge configuration

To generate zero level in a full-bridge inverter, the combination can be S1 and S2 on while S3 and S4 off or vice versa. The three possible levels referring to above discussion are shown in Table 1.1.

Table 1.1. Possible levels of switches

| Conducting Switches                                                | Load Voltage V <sub>AR</sub> |

|--------------------------------------------------------------------|------------------------------|

| S <sub>1</sub> , S <sub>4</sub>                                    | + V <sub>s</sub>             |

| S <sub>2</sub> , S <sub>3</sub>                                    | $-V_s$                       |

| S <sub>1</sub> , S <sub>2</sub> or S <sub>3</sub> , S <sub>4</sub> | 0                            |

Fig 1.5 Three phase inverter

#### MODES OF CONDUCTION

A three phase output can be obtained from a configuration of six transistors and six diodes as shown in fig. Two types of control signals can be applied to transistors

- 180 degree conduction

- 120 degree conduction

#### 180 degree conduction:

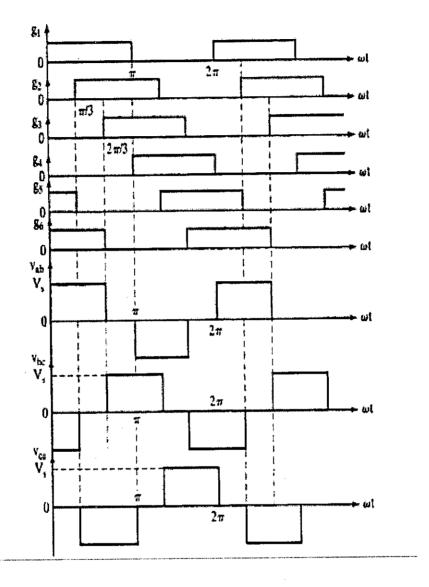

In this mode each transistor conducts for 180 degrees. Three transistors remain on at any instant of time. When S1 is switched on, terminal a is connected to the positive terminal of the dc input voltage. When S4 is switched on, terminal a is brought to the negative terminal of the dc source. There are six modes of operation in a cycle with duration of 60 degrees each.

The gating signals are provided such that the switching sequence is S6 S1 S2, S1 S2 S3 S2 S3 S4, S3 S4 S5, S4 S5 S6 and S5 S6 S1 as in fig. The gating signals are shifted by 60 degree to obtain three phase balanced voltage.

Fig 1.6. Waveform of 180 conduction mode

#### 120 degree conduction mode:

In this mode each transistor conducts for 120 degrees. Three transistors remain on at any instant of time. There are six modes of operation in a cycle with duration of 60 degrees each. The

gating signals are provided such that the switching sequence is S6 S1, S1 S2, S2 S3, S3 S4, S4 S5 and S5 S6 as in fig. There is a delay of 30 degrees turning off of S1 and turning on of S4. Thus there is no possibility of short circuit of the dc supply through one upper and one lower transistor.

The voltage waveform is shown in figure 1.7.

Fig 1.7. Waveform of 120 conduction mode

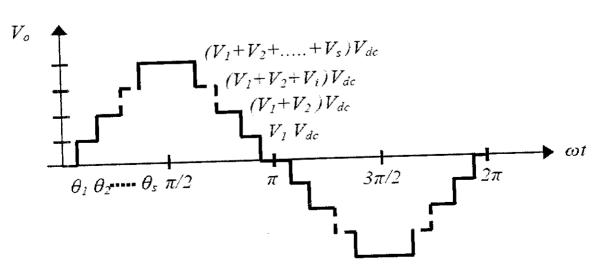

## MULTILEVEL INVERTERS

The multilevel voltage source inverter is recently applied in many industrial applications such as ac power supplies, static VAR compensators, drive systems, etc. One of the significant advantages of multilevel configuration is the harmonic reduction in the output waveform without increasing switching frequency or decreasing the inverter power output. The output voltage waveform of a multilevel inverter is composed of the number of levels of voltages, typically obtained from capacitor voltage sources. The so-called multilevel starts from three levels. As the number of levels reach infinity, the output THD approaches zero. The number of the achievable voltage levels, however, is limited by voltage unbalance problems, voltage clamping requirement, circuit layout, and packaging constraints. There are three general configurations of multilevel inverter. They are

- Diode clamped

- Flying capacitor

- Cascaded H-bridge

But there are also other types of multilevel inverters existing. The generalized output of a multilevel inverter is shown below.

Fig 1.8. Generalized output of multilevel inverter

### 1.4 ORGANISATION OF THE PROJECT

#### Chapter 1:

It comprises of general introduction to basics of inverters, multilevel inverters and the proposed topology.

#### Chapter 2:

It includes fundamental configurations of multilevel inverters and also our proposed system with reduced number of switches.

#### Chapter 3:

Simulation results of five, seven, and nine level inverters are shown along with the THD values and THD comparisons of different levels of inverter.

#### Chapter 4:

Hardware details of the proposed system.

#### Chapter 5:

It includes scope of the project and its future expansion.

# **CHAPTER**

#### CHAPTER 2

#### **MULTILEVEL INVERTER**

#### 2.1. MULTILEVEL INVERTER

Multilevel inverter is considered as one of the most significant recent advances in power electronics. Multilevel inverters have drawn tremendous interest in the field of high-voltage high-power applications such as laminators, mills, conveyors, compressors, large induction motor drives, UPS systems and static VAR compensation. Its concept is based on producing small output voltage steps, resulting in better power quality. Multilevel inverters accomplish the concept of power conversion using small voltage steps, then achieving better power quality. Although this requires a large number of semiconductor devices, which is considered as a primary disadvantage. They are of lower ratings and operate at the fundamental frequency so that the switching loss is reduced and better electromagnetic compatibility is achieved. The fundamental configurations of multilevel inverters include; the diode-clamp topology, the flying-capacitor topology, and the series H-bridge topology. Recently, there has been a great interest in cascaded hybrid topologies dedicated to large drive systems applications.

## 2.2. A LITERATURE SURVEY ON MULTILEVEL INVERTERS

As per literature there are three fundamental configurations of multilevel inverter. They are

- Diode clamped

- Flying capacitor

- Cascaded H-bridge

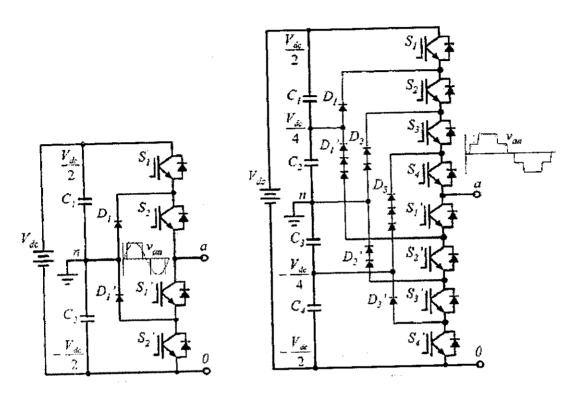

#### DIODE CLAMPLED MULTILEVEL INVERTER

fig 2.1. Diode clamped inverters

The diode clamped multilevel inverter is can produce any number of levels of output voltage. An m-level inverter requires (m-1) capacitors, 2( m-1) switching devices and (m-1)(m-2) clamping diodes. The diode clamped multilevel inverter has the following characteristics:

- High voltage rating of the blocking diodes

- Unequal switching of devices

- Capacitor voltage unbalance

The following are the advantages of diode clamped multilevel inverter.

- Reduced harmonic content

- Control method is simple

- Inverter efficiency is high because all devices are switched at fundamental frequency

The following are the disadvantages of diode clamped multilevel inverter.

- More number of clamping devices are required when the number of level are increased

- It is difficult to control the real power flow in the system

### FLYING CAPACITOR MULTILEVEL INVERTER

Fig 2.2. Flying capacitor inverters

The flying capacitor configuration multilevel inverter is shown in the figure. This topology requires large number of capacitors. For m-level inverter it requires (m-1)\*(m-2)/2 auxiliary capacitors phase per leg in addition to (m-1) dc bus capacitors. This multilevel inverter has the following characteristics.

- This topology uses large number of capacitors

- There is balance in the voltages of the capacitors used

The following are the advantages of flying capacitor multilevel inverter.

- Large amount of storage capacitors are used which can provide capabilities during power outages.

- These inverters provide switch combination redundancy for balancing different voltage levels

- With the increase in the number of levels the harmonic content is reduced thus reduces the usage of filters

- Both active power and reactive power can be controlled

The following are the disadvantages of flying capacitor multilevel inverter.

- Usage of large number of capacitors

- Control of inverter is complicated

- Switching frequency and switching losses are high for real power transmission

## CASCADED H-BRIDGE MULTILEVEL INVERTER

Fig 2.3. Cascaded H-bridge multilevel inverter

Cascaded multilevel inverters are based on a series connection of several single-phase inverters. This structure is capable of reaching medium output voltage levels using only standard low-voltage mature technology components. Typically, it is necessary to connect three to ten inverters in series to reach the required output voltage. The general circuit diagram of a three phase cascaded H- bridge inverter is shown in fig. The cascaded multilevel structure has the following features.

- It requires separate dc source. So it is very useful in conversion process for renewable energy sources such as photovoltaic cell, biomass etc.

- Connecting two dc source back to back is not possible because short circuit may occur if not switched synchronously

The following are the advantages of cascaded multilevel inverter.

- It requires least number of switches when compared to the other two topologies

- Since it has the same structure connected together optimized circuit layout and packing is

possible. There are no requirements of extra clamping diodes or voltage balancing

capacitors.

- Soft switching techniques are used to reduce the switching losses anddevice stresses.

The following are the disadvantages of cascaded multilevel inverter.

It needs separate dc sources for real power conversions thereby limiting its applications

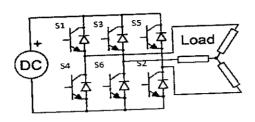

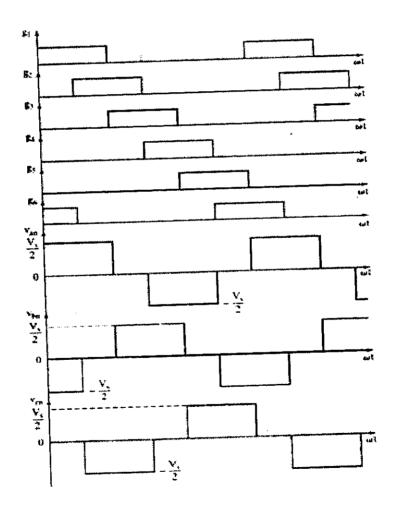

#### 2.3. PROPOSED MULTILEVEL INVERTER TOPOLOGY:

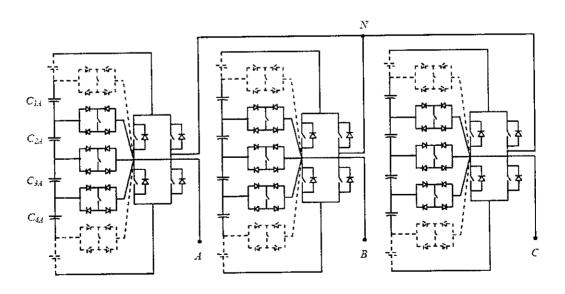

The principle objective of the proposed configuration of multilevel inverter power circuit is to reach at the minimum possible number of switching devices, without affecting thestaircase output voltage waveform characterized by conventional multilevel topologies. However, there is a small penalty have to be paid, which is the increased rating of the four main switches as they have to withstand the whole dc bus. The continued and increased advances in high power semiconductor technology allowed the working range of IGBTs to reach 6.5kV, which will indeed increase the popularity of the presented configuration. The generalized configuration of the proposed three-phase multilevel inverter is shown in Fig.1. Each phase consists of4 main switches in an H-bridge configuration connected across the dc bus. A group of capacitors are connected acrossthe dc bus to achieve voltage divider task for the differentnumber of inverter levels. A number of bi-directional switches are connected from the supply voltage dividerpoints to the phase voltage point of the main bridge. The generalized multilevel inverter can be developed for any required number of levels.

Fig 2.4. Generalized circuit diagram of proposed multilevel inverter

Fig 2.5. Power circuit of the proposed three-phase 5-level inverter

## EXPECTED OUTPUT OF THE PROPOSED SYSTEM

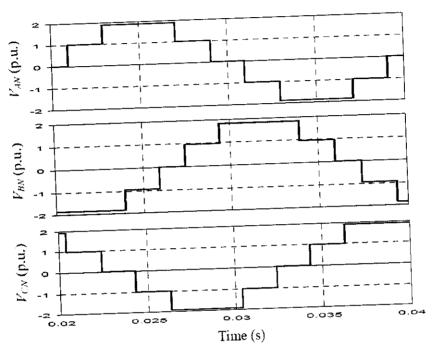

Fig 2.6. Output phase voltages

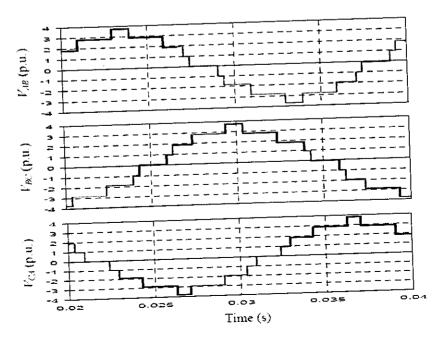

Fig 2.7. Output line voltage

# 2.4. COMPARISION BETWEEN CASCADED H-BRIDGE TOPOLOGY AND THE PROPOSED TOPOLOGY:

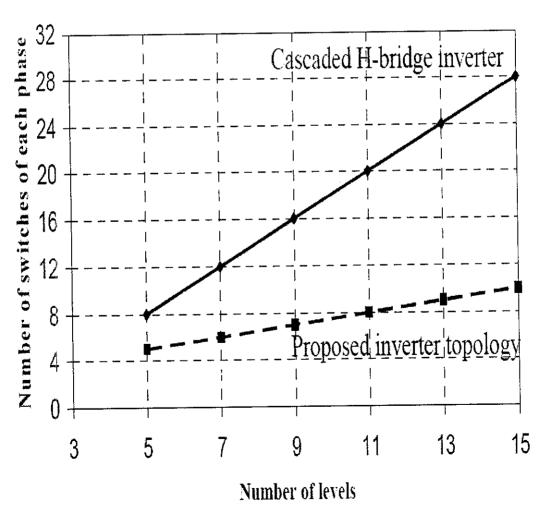

The graph following graph is plotted between number of levels and number of switches for each phase. Here the cascaded H-bridge inverter and proposed inverter topology are compared. And it can be seen that the number of switches used is very much reduced in the new inverter topology.

Fig 2.8. Comparison between cascaded H-bridge inverter and proposed topology

## 2.5. ADVANTAGES OF THE PROPOSED TOPOLOGY:

The new topology has some good advantages over other existing inverter topologies. They are.

- Substantial reduction in the number of switching devices used.

- Complexity of the circuit is reduced

- Reduction in the overall size of the hardware

- Multilevel output can be realized for any number of levels

Thus this is the most widely used topology of multilevel inverter because of these advantages it has over other topologies.

# **CHAPTER**

#### **CHAPTER 3**

## SIMULATION RESULTS

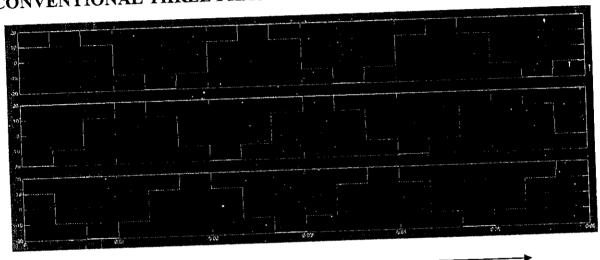

## 3.1. CONVENTIONAL THREE PHASE INVERTER

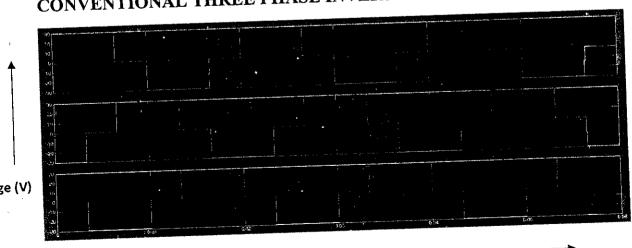

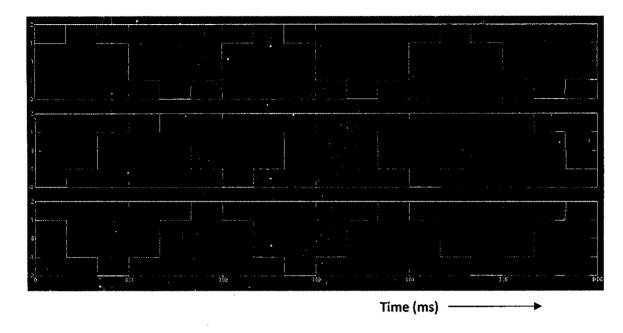

## 3.1.1. OUTPUT WAVEFORMS

(V)

## CONVENTIONAL THREE PHASE INVERTER- PHASE VOLTAGE

Time (ms)

Fig 3.1. Phase Voltage of Three Phase Inverter

## CONVENTIONAL THREE PHASE INVERTER- LINE VOLTAGE

Time (ms)

Fig 3.2. Line Voltage of Three Phase Inverter

#### CONVENTIONAL THREE PHASE INVERTER- CURRENT

Fig 3.3. Current Waveform of Three Phase Inverter

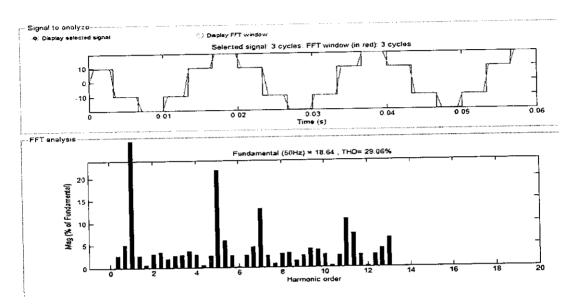

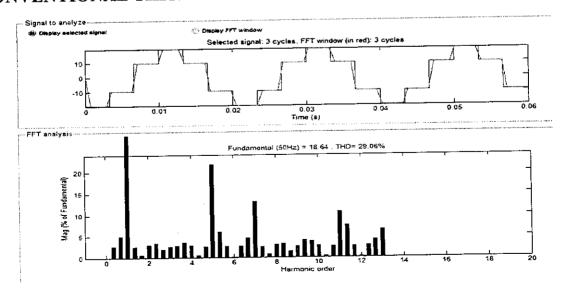

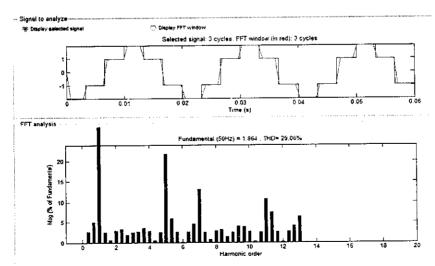

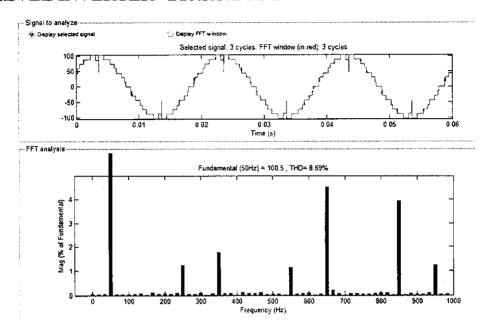

#### 3.1.2. FFT ANALYSIS

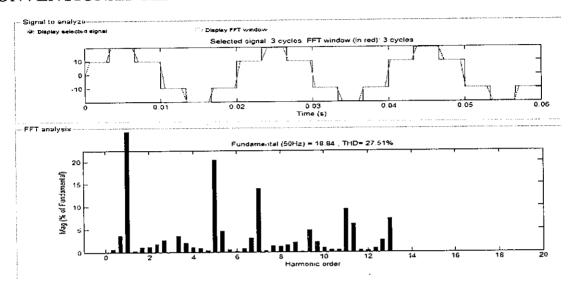

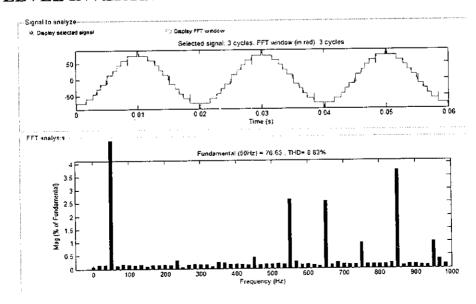

## CONVENTIONAL THREE PHASE INVERTER- R PHASE FFT

THD=29.06%

Fig 3.4. FFT-R Phase

## CONVENTIONAL THREE PHASE INVERTER- Y PHASE FFT

THD=29.06%

Fig 3.5. FFT-Y Phase

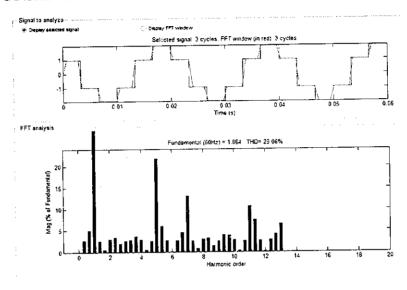

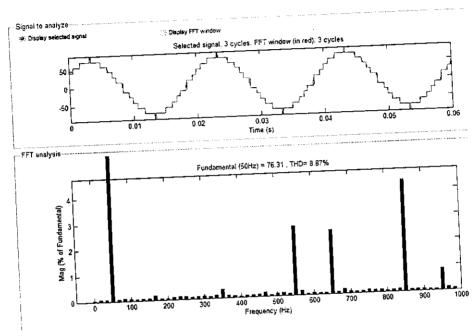

## CONVENTIONAL THREE PHASE INVERTER- B PHASE FFT

THD=27.51%

Fig 3.6. FFT-B Phase

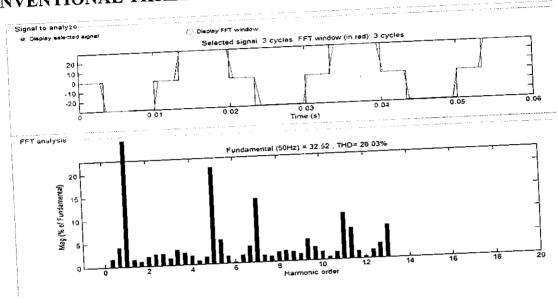

# CONVENTIONAL THREE PHASE INVERTER- RY PHASE FFT

THD=28.03%

Fig 3.7. FFT-RY Line

# CONVENTIONAL THREE PHASE INVERTER- YB PHASE FFT

THD=28.03%

Fig 3.8. FFT-YB Line

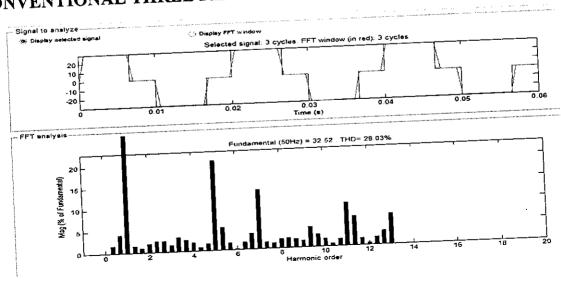

## CONVENTIONAL THREE PHASE INVERTER- BR PHASE FFT

THD=29.58%

Fig 3.9. FFT-BR Line

### CONVENTIONAL THREE PHASE INVERTER- R PHASE CURRENT FFT

THD=27.51%

Fig 3.10 FFT-R Phase Current

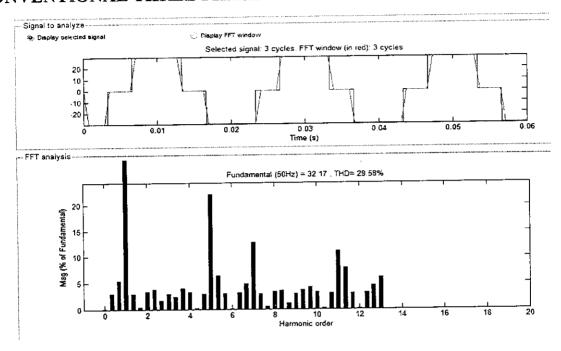

### CONVENTIONAL THREE PHASE INVERTER- Y PHASE CURRENT FFT

THD=29.06%

Fig 3.11 FFT-Y Phase Current

# CONVENTIONAL THREE PHASE INVERTER- B PHASE CURRENT FFT

THD=29.06%

Fig 3.12 FFT-B Phase Current

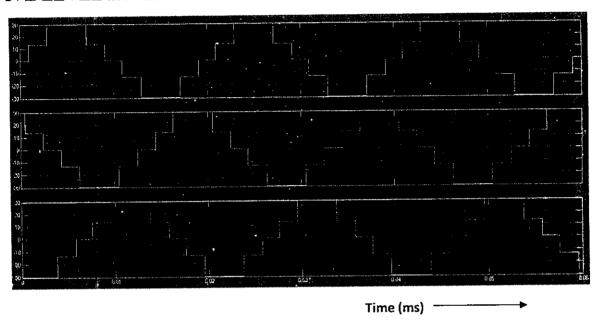

### 3.2. FIVE LEVEL INVERTER

### 3.2.1. OUTPUT WAVEFORMS

### FIVE LEVEL INVERTER- PHASE VOLTAGE

Fig 3.13. Phase Voltage Of Five Level Inverter

### FIVE LEVEL INVERTER- LINE VOLTAGE

Time (ms) Fig 3.14. Line Voltage Of Five Level Inverter

# FIVE LEVEL INVERTER- CURRENT

Fig 3.15. Current Waveforms of Five Level Inverter

20

### 3.2.2 FFT ANALYSIS

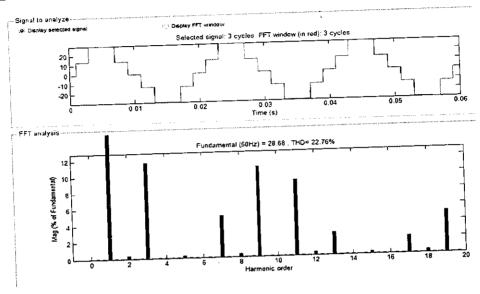

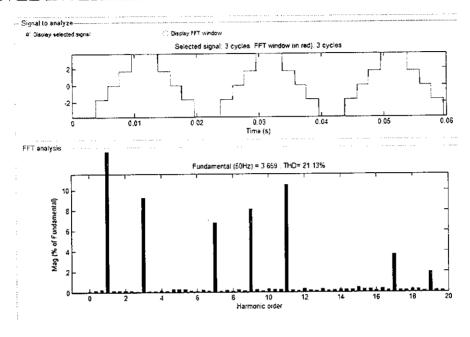

# FIVE LEVEL INVERTER- R PHASE FFT

THD=22.76%

Fig 3.16. FFT-R Phase

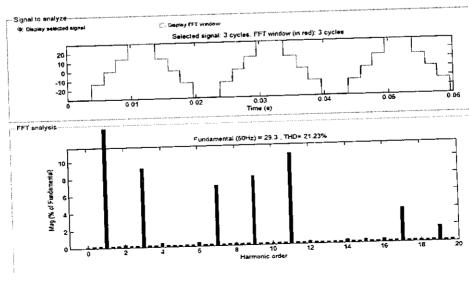

# FIVE LEVEL INVERTER- Y PHASE FFT

THD=21.23%

Fig 3.17. FFT-Y Phase

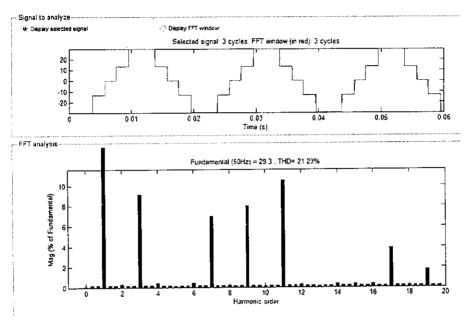

### FIVE LEVEL INVERTER- B PHASE FFT

THD=21.23%

Fig 3.18. FFT-B Phase

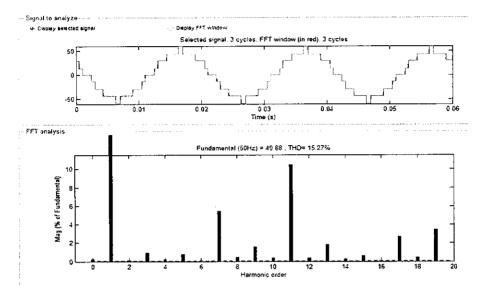

### FIVE LEVEL INVERTER- RY LINE FFT

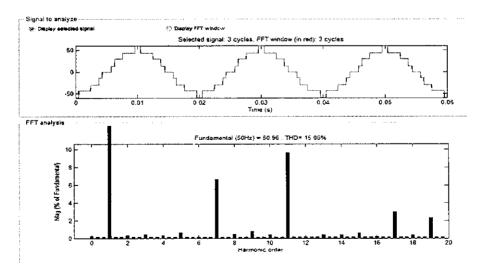

THD=15.27%

Fig 3.19. FFT-RY Line

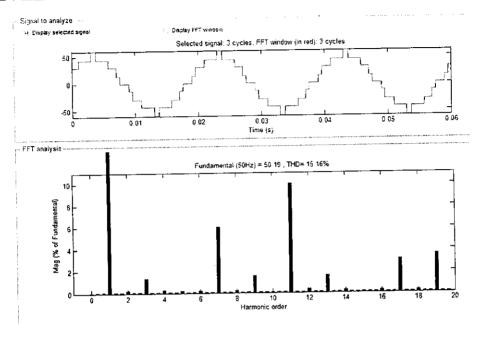

### FIVE LEVEL INVERTER- YB LINE FFT

THD=15.06%

Fig 3.20. FFT-YB Line

### FIVE LEVEL INVERTER- BR LINE FFT

THD=15.16%

Fig 3.21. FFT-BR Line

# FIVE LEVEL INVERTER- R PHASE CURRENT FFT

Fig 3.22. FFT-R Phase Current

# FIVE LEVEL INVERTER- Y PHASE CURRENT FFT

THD=21.43%

Fig 3.23. FFT-Y Phase Current

### FIVE LEVEL INVERTER- B PHASE CURRENT FFT

THD=21.23%

Fig 3.24. FFT-B Phase Current

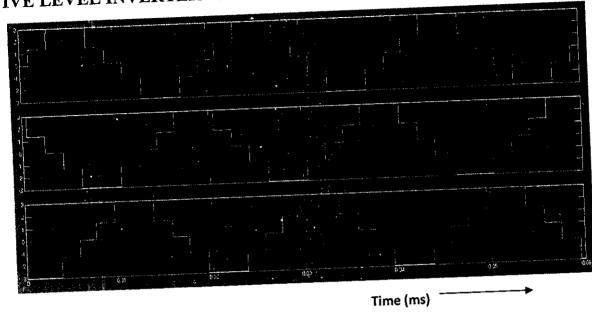

### 3.3. SEVEN LEVEL INVERTER

#### 3.3.1 OUTPUT WAVEFORMS

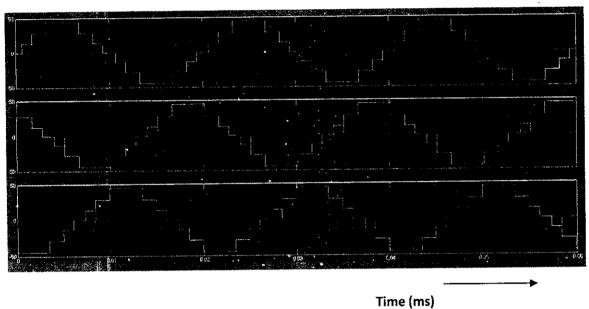

### SEVEN LEVEL INVERTER- PHASE VOLTAGE

Fig 3.25. Phase Voltage Of Seven Level Inverter

### SEVEN LEVEL INVERTER- LINE VOLTAGE

Time (ms)

Fig 3.26.Line Voltage Of Seven Level Inverter

# SEVEN LEVEL INVERTER- CURRENT

Fig 3.27. Current Waveforms of Seven Level Inverter

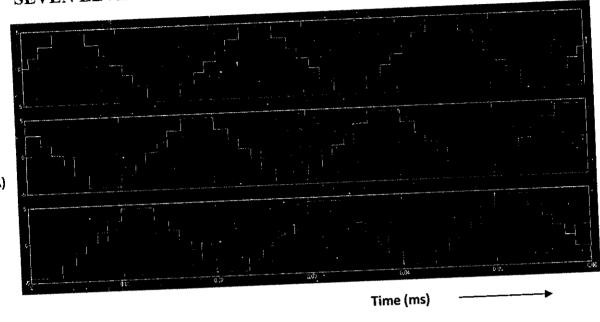

### 3.3.2 FFT ANALYSIS

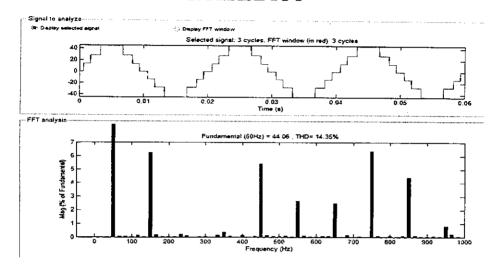

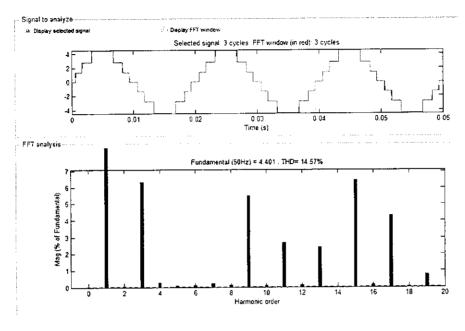

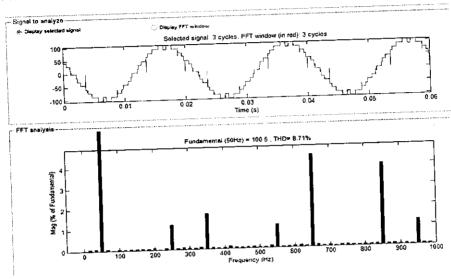

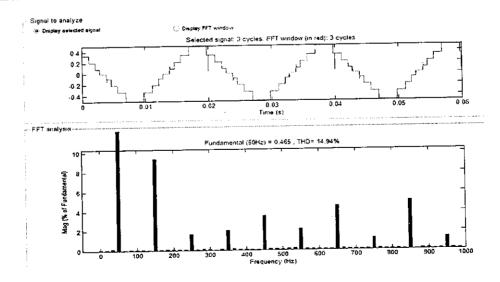

### SEVEN LEVEL INVERTER- R PHASE FFT

THD=14.35%

Fig 3.28. FFT-R Phase

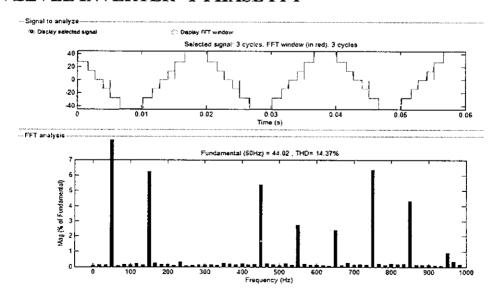

### SEVEN LEVEL INVERTER- Y PHASE FFT

THD=14.37%

Fig 3.29. FFT-Y Phase

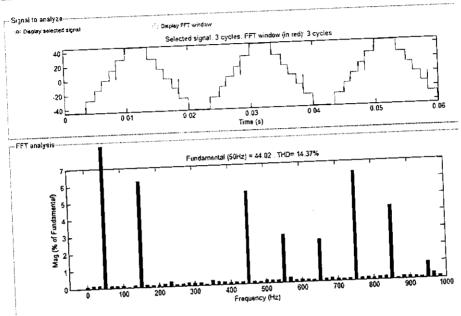

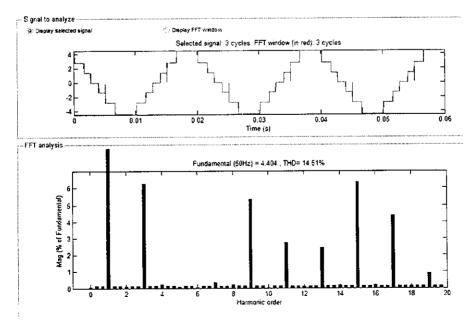

# SEVEN LEVEL INVERTER- B PHASE FFT

THD=14.37%

Fig 3.30. FFT-B Phase

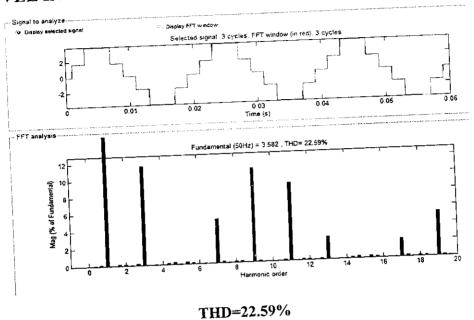

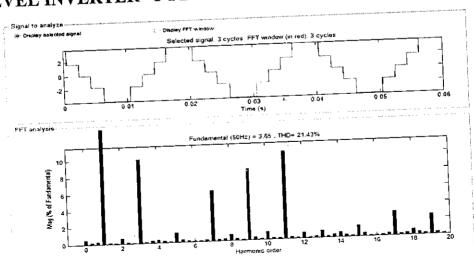

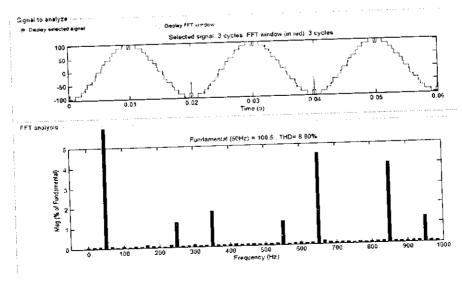

### SEVEN LEVEL INVERTER- RY LINE FFT

THD=15.27%

Fig 3.31. FFT-RY Line

### SEVEN LEVEL INVERTER- YB LINE FFT

THD=15.06%

Fig 3.32. FFT-YB Line

# SEVEN LEVEL INVERTER- BR LINE FFT

THD=15.16%

Fig 3.33. FFT-BR Line

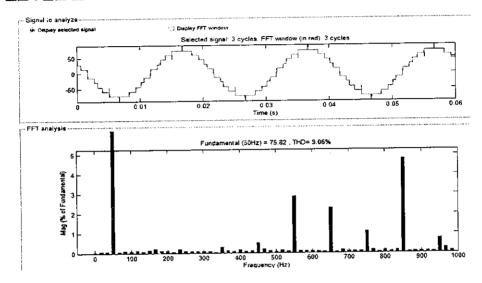

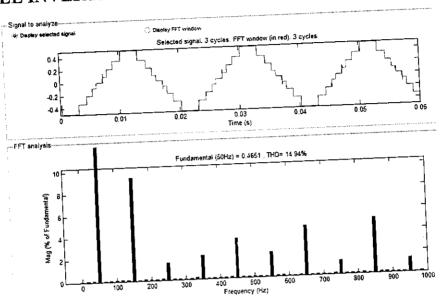

### SEVEN LEVEL INVERTER -R PHASE CURRENT FFT

THD=14.57%

Fig 3.34. FFT-R Phase Current

### SEVEN LEVEL INVERTER -Y PHASE CURRENT FFT

THD=14.51%

Fig 3.35. FFT-Y Phase Current

# 3.4. NINE LEVEL INVERTER

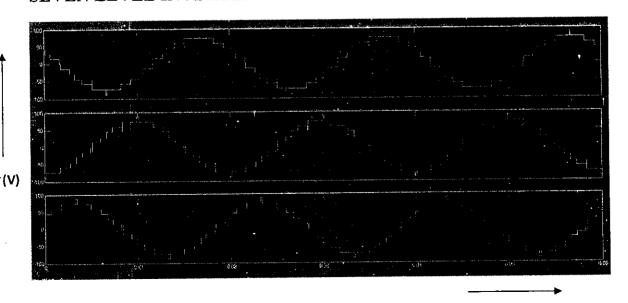

# 3.4.1. OUTPUT WAVEFORMS

(V)

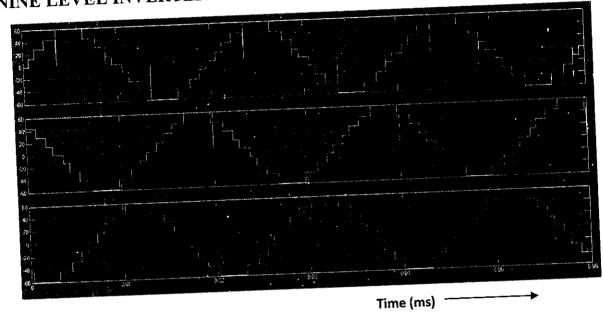

# NINE LEVEL INVERTER -PHASE VOLTAGE

Fig 3.37. Phase Voltage Of Nine Level Inverter

# NINE LEVEL INVERTER -LINE VOLTAGE

Time (ms) \_\_\_\_\_

Fig 3.38. Line Voltage Of Nine Level Inverter

# NINE LEVEL INVERTER -CURRENT

Fig 3.39. Current Waveforms Of Nine Level Inverter

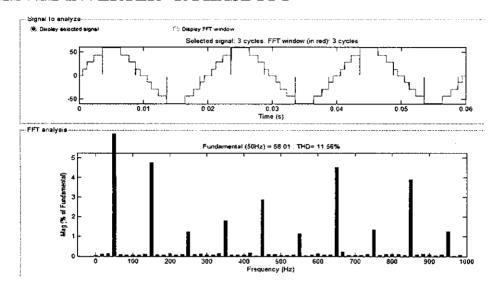

#### 3.4.2 FFT ANALYSIS

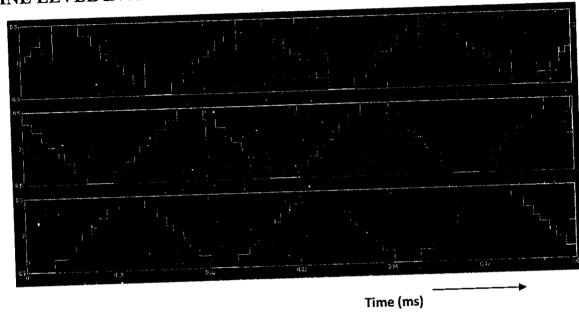

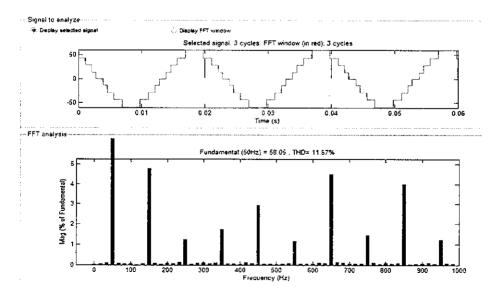

### NINE LEVEL INVERTER -R PHASE FFT

THD=11.56%

Fig 3.40 FFT-R Phase

#### NINE LEVEL INVERTER -Y PHASE FFT

THD=11.57%

Fig 3.41 FFT-Y Phase

## NINE LEVEL INVERTER -B PHASE FFT

THD=11.59%

Fig 3.42 FFT-B Phase

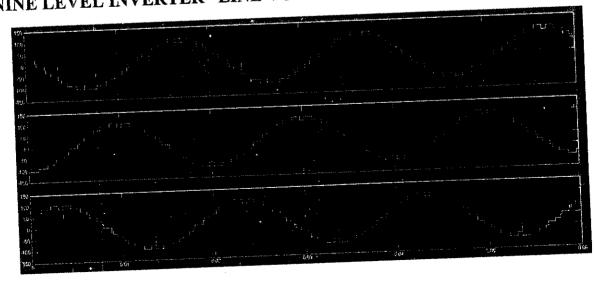

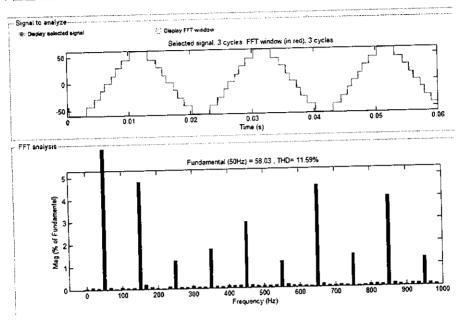

# NINE LEVEL INVERTER -RY LINE FFT

THD=8.71%

Fig 3.43. FFT-RY Line

# NINE LEVEL INVERTER -YB LINE FFT

THD=8.80%

Fig 3.44. FFT-YB Line

### NINE LEVEL INVERTER -BR LINE FFT

THD=8.69%

Fig 3.45. FFT-BR Line

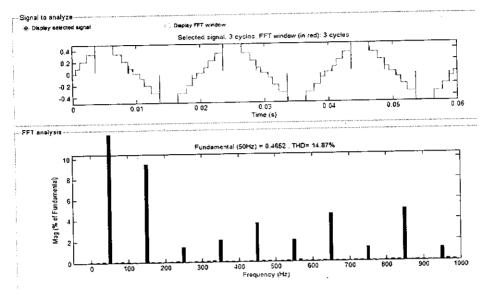

### NINE LEVEL INVERTER -R PHASE CURRENT FFT

THD=14.87%

Fig 3.46. FFT-R Phase Current

### NINE LEVEL INVERTER -Y PHASE CURRENT FFT

THD=14.94%

Fig 3.47. FFT-Y Phase Current

# NINE LEVEL INVERTER -B PHASE CURRENT FFT

THD=14.94%

Fig 3.48. FFT-B Phase Current

### 3.5 CONCLUSION

From the simulation results obtained, we have formulated the table which compares the THD values of phase and line voltages for 5-level, 7- level, 9- level and conventional inverter. And also the number of switches used for different levels are also tabulated. Here the simulation results for this topology are obtained by using optimized harmonic stepped waveform technique. This further reduces the harmonics in the system. Hence we come to the conclusion that the harmonics are considerably reduced when compared with the conventional inverter. Thus reduced THD is obtained using the least number of switching semiconductor devices.

| Inverter                          | Phase voltage THD | Line voltage | Number of switches |

|-----------------------------------|-------------------|--------------|--------------------|

|                                   | (%)               | THD (%)      |                    |

| 5-level inverter                  | 21.14             | 15.54        | 15                 |

| 7-level inverter                  | 14.36             | 9.10         | 18                 |

| 9-level inverter                  | 11.58             | 8.82         | 21                 |

| Conventional three phase inverter | 27.51             | 28.03        | -                  |

|                                   |                   |              |                    |

# **CHAPTER**

#### **CHAPTER 4**

#### HARDWARE DESCRIPTION

#### 4.1 INTRODUCTION

The hardware for the proposed topology requires a separate MOSFET driver circuit there by increasing the overall cost. So hardware implementation is done only for single phase because of this problem. Here for single phase operation of the inverter hardware, harmonics is analyzed using a THD analyzer and the results are shown.

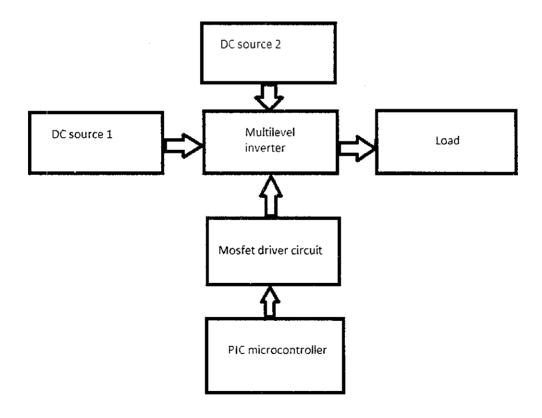

#### 4.2 OVERALL BLOCK DIAGRAM

Fig 4.1. Overall block diagram

The circuit consists of the following blocks

- Power supply circuit

- H-bridge inverter circuit

- Bi-directional switching circuit

- Mosfet driver circuits

- Optoisolator circuits

- PIC microcontroller

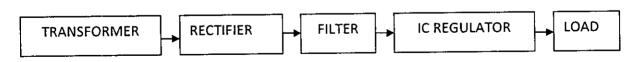

#### 4.3 POWER SUPPLY CIRCUIT

The ac voltage, typically 220V rms, is connected to a transformer, which steps that ac voltage down to the level of the desired dc output. A diode rectifier then provides a full-wave rectified voltage that is initially filtered by a simple capacitor filter to produce a dc voltage. This resulting dc voltage usually has some ripple or ac voltage variation.

A regulator circuit removes the ripples and also remains the same dc value even if the input dc voltage varies, or the load connected to the output dc voltage changes. This voltage regulation is usually obtained using one of the popular voltage regulator IC units.

Fig 4.2. Block diagram (Power supply)

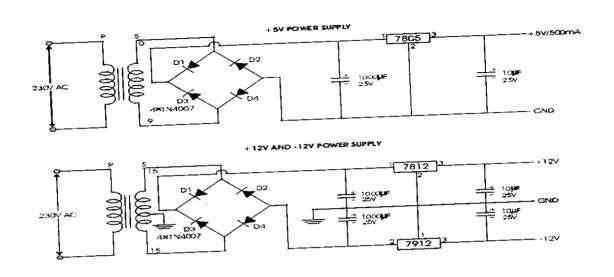

#### 4.3.1 TRANSFORMER

The potential transformer will step down the power supply voltage (0-230V) to (0-6V) level. Then the secondary of the potential transformer will be connected to the precision rectifier, which is constructed with the help of op-amp. The advantages of using precision rectifier are it will give peak voltage output as DC, rest of the circuits will give only RMS output.

#### 4.3.2 BRIDGE RECTIFIER

When four diodes are connected as shown in figure, the circuit is called as bridge rectifier. The input to the circuit is applied to the diagonally opposite corners of the network, and the output is taken from the remaining two corners.

Let us assume that the transformer is working properly and there is a positive potential, at point A and a negative potential at point B. the positive potential at point A will forward bias D3 and reverse bias D4.

The negative potential at point B will forward bias D1 and reverse D2. At this time D3 and D1 are forward biased and will allow current flow to pass through them; D4 and D2 are reverse biased and will block current flow.

The path for current flow is from point B through D1, up through RL, through D3, through the secondary of the transformer back to point B. this path is indicated by the solid arrows. Waveforms (1) and (2) can be observed across D1 and D3.

One-half cycle later the polarity across the secondary of the transformer reverse, forward biasing D2 and D4 and reverse biasing D1 and D3. Current flow will now be from point A through D4, up through RL, through D2, through the secondary of T1, and back to point A. This path is indicated by the broken arrows. Waveforms (3) and (4) can be observed across D2 and D4. The current flow through RL is always in the same direction. In flowing through RL this current develops a voltage corresponding to that shown waveform (5). Since current flows through the load (RL) during both half cycles of the applied voltage, this bridge rectifier is a full-wave rectifier.

One advantage of a bridge rectifier over a conventional full-wave rectifier is that with a given transformer the bridge rectifier produces a voltage output that is nearly twice that of the conventional full-wave circuit.

This may be shown by assigning values to some of the components shown in views A and B. assume that the same transformer is used in both circuits. The peak voltage developed between points X and y is 1000 volts in both circuits. In the conventional full-wave circuit shown—in view A, the peak voltage from the center tap to either X or Y is 500 volts. Since only one diode can conduct at any instant, the maximum voltage that can be rectified at any instant is 500 volts.

The maximum voltage that appears across the load resistor is nearly-but never exceeds-500 volts, as result of the small voltage drop across the diode. In the bridge rectifier shown in view B, the maximum voltage that can be rectified is the full secondary voltage, which is 1000 volts. Therefore, the peak output voltage across the load resistor is nearly 1000 volts. With both circuits using the same transformer, the bridge rectifier circuit produces a higher output voltage than the conventional full-wave rectifier circuit.

#### 4.3.3 IC VOLTAGE REGULATORS

Voltage regulators comprise a class of widely used ICs. Regulator IC units contain the circuitry for reference source, comparator amplifier, control device, and overload protection all in a single IC. IC units provide regulation of either a fixed positive voltage, a fixed negative voltage, or an adjustably set voltage. The regulators can be selected for operation with load currents from hundreds of milli amperes to tens of amperes, corresponding to power ratings from milli watts to tens of watts.

Fig 4.3. Circuit diagram (Power supply)

A fixed three-terminal voltage regulator has an unregulated dc input voltage, Vi, applied to one input terminal, a regulated dc output voltage, Vo, from a second terminal, with the third terminal connected to ground.

The series 78 regulators provide fixed positive regulated voltages from 5 to 24 volts. Similarly, the series 79 regulators provide fixed negative regulated voltages from 5 to 24 volts.

- For ICs, microcontroller, LCD ----- 5 volts

- For alarm circuit, op-amp, relay circuits ----- 12 volts

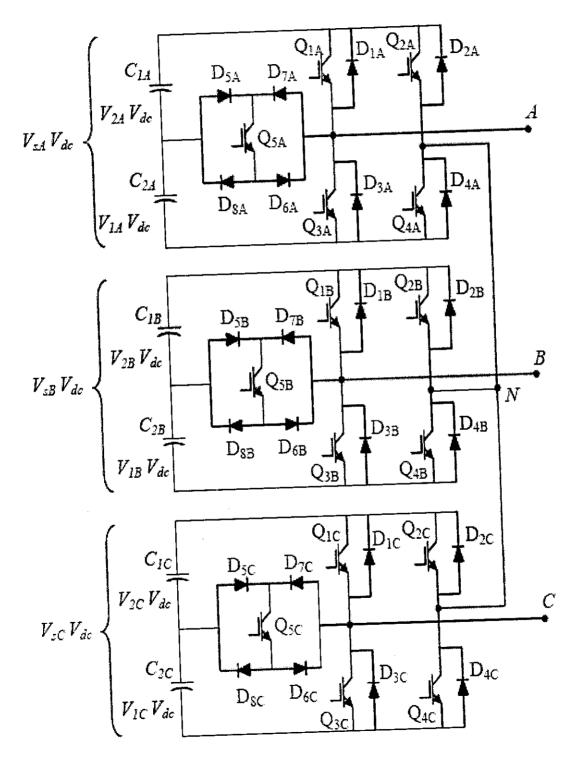

## 4.4. H-BRIDGE INVERTER CIRCUIT

The circuit involves a single phase inverter that consists of four MOSFETS as switching devices. They are named as Q1, Q2, Q3, and Q4. The snubber circuit has resistors and capacitors for protecting the bridge from overvoltage and overcurrent. The load used here involves an

inductor. During the positive half cycle, MOSFETs Q1 and Q4 will conduct and Q2 and Q3 conduct during the negative half cycle.

Fig 4.4. H-bridge circuit diagram

The driver circuit forms the most important part of the hardware unit because it gives the triggering pulses to the switches in proper sequence. It is used to provide 9 to 20 to switch the MOSFETs of the inverter. Driver amplifies the voltage from microcontroller which is 5 Volts.

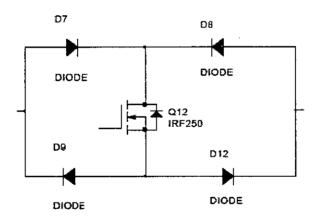

#### 4.5. BI-DIRECTIONAL SWITCHING CIRCUIT

There are five levels in the topology for single phase. (i.e. Vrms, Vrms/2, zero, -Vrms/2, -Vrms). And for three phase Y-phase is generated with 120 degree phase shift and B-phase with 240 degree phase shift. This is the bi-directional switching circuit generally consists of four diodes and one Mosfet which is used to generate the Vrms/2 & -Vrms/2 level of five levels.

During positive half cycle to generate +Vrms/2 level diode D7, Q12, D12 will be conducting and at negative half cycle -Vrms/2 level will be generated by the conduction of D9, Q12, D8.

Fig 4.5. Bi-directional switching circuit

This bi-directional switching circuit is also controlled by the driver circuit which was provided signal from micro controller.

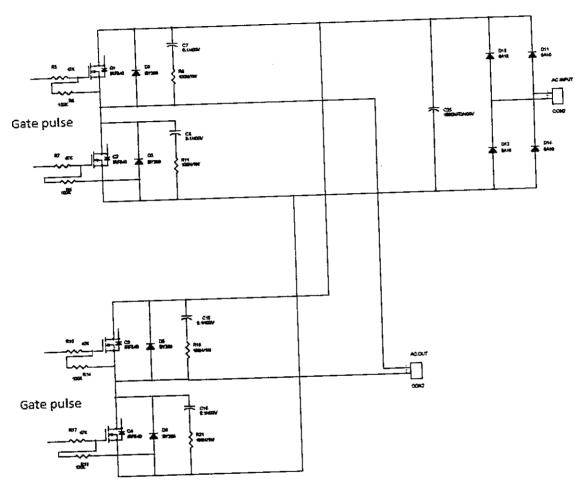

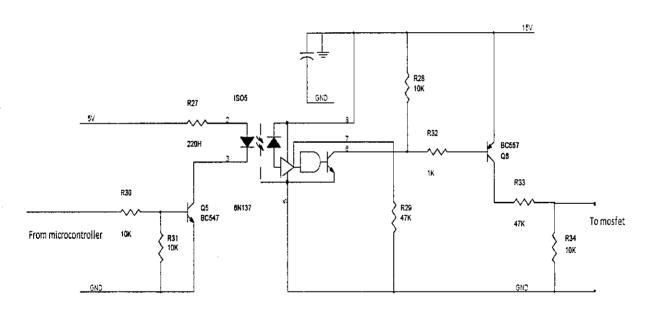

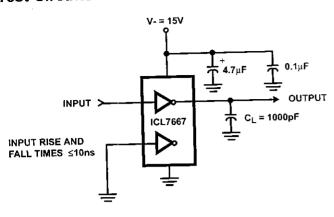

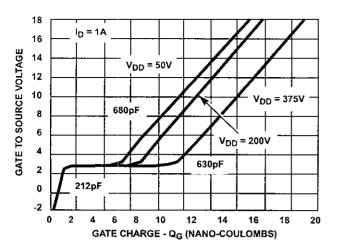

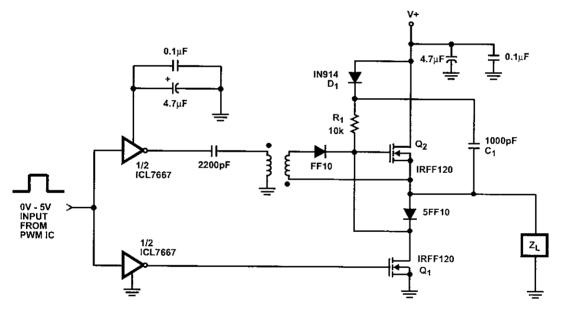

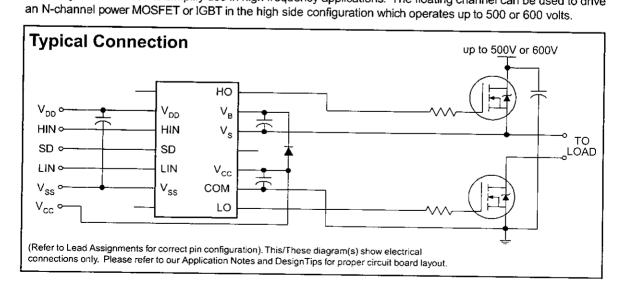

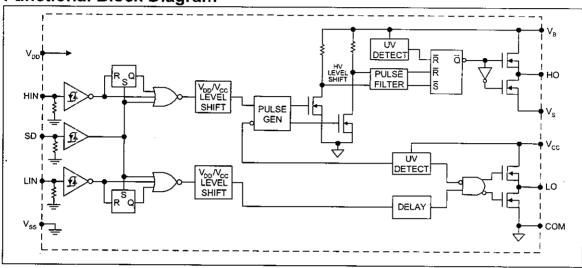

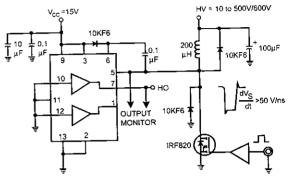

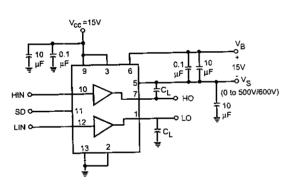

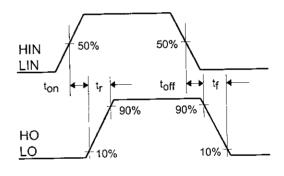

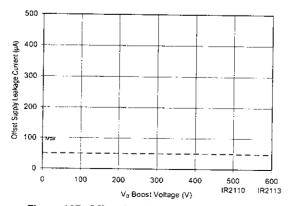

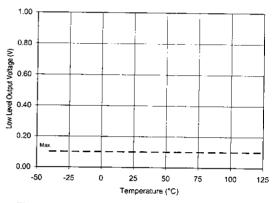

#### 4.6. MOSFET DRIVERS

To turn a power MOSFET on, the gate terminal must be set to a voltage at least 10 volts greater than the source terminal (about 4 volts for logic level MOSFETs). This is comfortably above the Vgs(th) parameter.

One feature of power MOSFETs is that they have a large stray capacitance between the gate and the other terminals, Ciss. The effect of this is that when the pulse to the gate terminal arrives, it must first charge this capacitance up before the gate voltage can reach the 10 volts required.

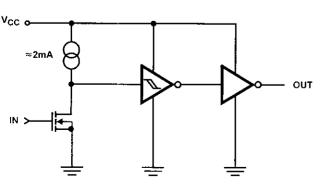

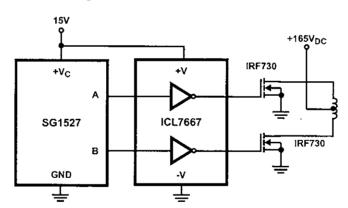

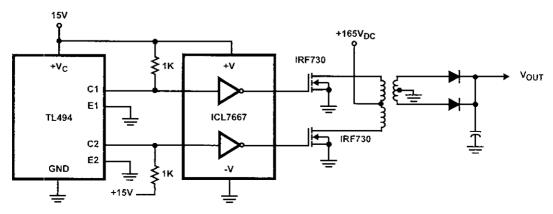

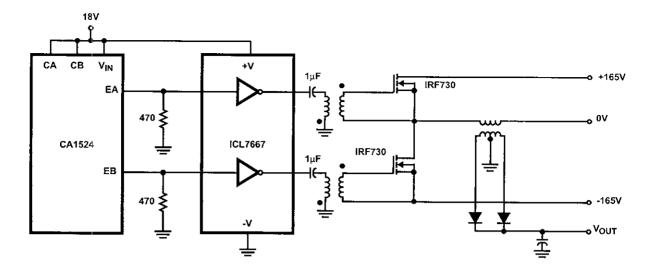

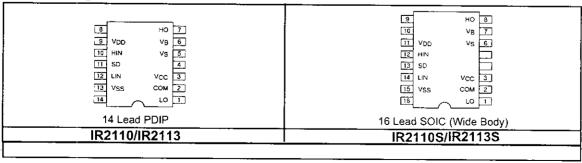

The gate terminal then effectively does take current. Therefore the circuit that drives the gate terminal should be capable of supplying a reasonable current so the stray capacitance can be charged up as quickly as possible. The best way to do this is to use a dedicated MOSFET driver chip. The driver circuit used is ICL7667 and IR2110

Fig 4.6. Mosfet driver circuit

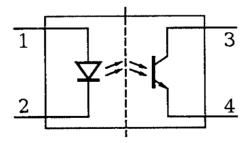

#### 4.7. OPTOISOLATOR

In electronics, an opto-isolator, also called an optocoupler, photocoupler, or optical isolator is an electronic device designed to transfer electrical signals by utilizing light waves to provide coupling with electrical isolation between its input and output. The main purpose of an

opto-isolator is "to prevent high voltages or rapidly changing voltages on one side of the circuit from damaging components or distorting transmissions on the other side." Commercially available opto-isolators withstand input-to-output voltages up to  $10 \, kV$  and voltage transients with speeds up to  $10 \, kV/\mu s$ .

Opto-isolator contains a source of light, almost always a near infrared light-emitting diode (LED), that converts electrical input signal into light, a closed optical channel (also called dielectrical channel) and a photo sensor, which detects incoming light and either generates electric energy directly, or modulates electric current flowing from an external power supply. The sensor can be a photo resistor, a photodiode, a phototransistor, a silicon-controlled rectifier (SCR) or a triac. Because LEDs can sense light in addition to emitting it, construction of symmetrical, bidirectional opto-isolators is possible. An optocoupled solid state relay contains a photodiode opto-isolator which drives a power switch, usually a complementary pair of MOSFET transistors. A slotted optical switch contains a source of light and a sensor, but its optical channel is open, allowing modulation of light by external objects obstructing the path of light or reflecting light into the sensor. The optocoupler used is 6N137 and FOD817.

Fig 4.7. optoisolator

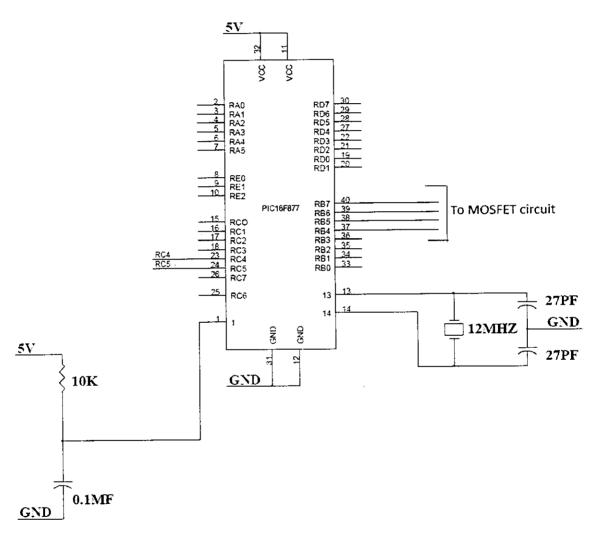

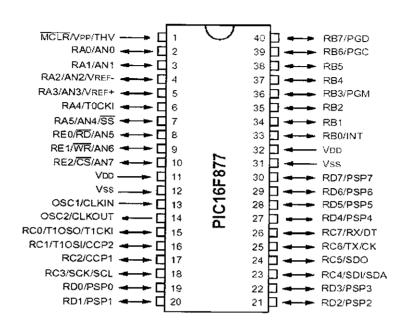

#### 4.8 PIC MICROCONTROLLER

#### PIC 16F877 BASED CONTROL CIRCUIT

RESET CIRCUIT

Fig 4.8. Microcontroller based control circuit

In this circuit the PIC microcontroller PIC16F877 is used. Here out of the four ports the port B is used for giving data to the MOSFET switches. In the port B pins 40, 39, 38 and 37 are used. The 5V supply to the microcontroller is given by means of the power supply

circuit. And the microcontroller input clock is given by means of external clock circuit of frequency 12MHZ to the pins 13 and 14. We also have a reset circuit of giving the external reset pulse in case of refreshing the whole control circuit. The 5V supply for the reset circuit is also provided by means of the power circuit. The data sheet of this PIC microcontroller and the microcontroller coding are provided in the appendix.

### 4.9 HARWARE RESULTS

### 4.9.1 HARDWARE PROTOTYPE

Fig 4.9. Hardware Prototype

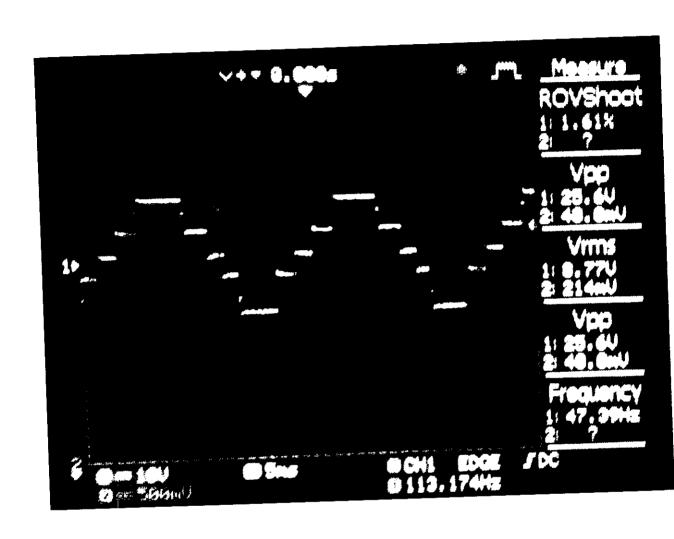

# 4.9.2 OUTPUT WAVEFORM

Fig 4.10. Hardware output waveform

INPUT VOLTAGE = +12V (DC voltage)

OUTPUT VOLTAGE = 24V (peak to peak voltage)

### 4.9.3 TOTAL HARMONIC DISTORTION ANALYSIS

Fig 4.11. Total Harmonic Distortion Output

The output waveform from the hardware is analyzed using THD analyzer and the value of THD thus obtained is 6.3%.

# **CHAPTER**

#### **CHAPTER 5**

#### CONCLUSION

#### 5.1. CONCLUSION

Here we have obtained output for single phase multilevel inverter in the hardware. We also did THD analysis using THD analyser. Here we obtained optimized output waveform. This inverter configuration may be applied to large drive systems, UPS systems, static VAR compensation schemes, and distributed power generation involving fuel cells and photovoltaic cells. This can also be implemented using PWM and the harmonics in the system can be further reduced.

#### 5.2. FUTURE SCOPE

This multilevel inverter configuration can be widely employed in power electronic drives because of its simple construction and minimum output distortion. Because of recent development the cost of the power electronic devices are being reduced rapidly. This can also be used in the field of renewable energy source. So this further shows the compatibility of this topology in the future.

#### REFERENCES

- 1. J. Lai and F. Peng, "Multilevel converters—a new breed of power converters," IEEE Trans. Ind. Appl., vol. 32, no. 3, pp. 509-517, 1996.

- 2. J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverter: a survey of topologies, controls, and applications," IEEE Trans. Power Electron., vol. 49, no. 4, pp. 724–738, 2000.

- 3. K. Corzine, and Y. Familiant, "A new cascaded multilevel H0bridge drive," IEEE Trans. Power Electron., vol. 17, no. 1, pp. 125–131, 2002.

- 4. T. Abdelhamid, and N. Abbasy, "A new topology of three-phase five level inverter applied to static var generation schemes," International Review of Electrical Engineering Journal, vol. 2, no. 3, pp. 359-368, 2006.

- 5. G. Su, "Multilevel DC-link inverter," IEEE Trans. Ind. Appl., vol. 41, no. 3, pp. 848-854, 2005.

- 6. D. Soto-Sanchez and T. Green, "Voltage balance and control in a multi-level unified power flow controller," IEEE Trans. Power Delivery, vol. 16, no. 4, pp. 732–738, 2001.

- 7. Z. Du, L. Tolbert, and J. Chiasson, "Harmonic elimination for multilevel converter with programmed PWM method," Proc. of the IEEE Industry Applications Annual Meeting Conference, 2004, pp. 2210–2215.

**APPENDIX**

#### APPENDIX A

#### PIC MICROCONTROLLER

The microcontroller that has been used for this project is from PIC series. PIC microcontroller is the first RISC based microcontroller fabricated in CMOS (complementary metal oxide semiconductor) that uses separate bus for instruction and data allowing simultaneous access of program and data memory.

The main advantage of CMOS and RISC combination is low power consumption resulting in a very small chip size with a small pin count. The main advantage of CMOS is that it has immunity to noise than other fabrication techniques.

EEPROM, EPROM, FLASH etc. are some of the memories of which FLASH is the most recently developed. Technology that is used in pic16F877 is flash technology, so that data is retained even when the power is switched off. Easy Programming and Erasing are other features of PIC 16F877.

#### PIN DIAGRAM OF PIC 16F877

#### TABLE SPECIFICATIONS

| DEVICE     | PROGRAM FLASH | DATA<br>MEMORY | DATA EEPROM |

|------------|---------------|----------------|-------------|

| PIC 16F877 | 8K            | 368 Bytes      | 256 Bytes   |

#### **CORE FEATURES:**

- High-performance RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two cycle

- Operating speed: DC 20 MHz clock input

DC - 200 ns instruction cycle

• Up to 8K x 14 words of Flash Program Memory,

Up to 368 x 8 bytes of Data Memory (RAM)

Up to 256 x 8 bytes of EEPROM data memory

- Pin out compatible to the PIC16C73/74/76/77

- Interrupt capability (up to 14 internal/external

- Eight level deep hardware stack

- Direct, indirect, and relative addressing modes

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC Oscillator for reliable operation

- Programmable code-protection

- Power saving SLEEP mode

- Selectable oscillator options

- Low-power, high-speed CMOS EPROM/EEPROM technology

- Fully static design

- In-Circuit Serial Programming (ICSP) via two pins

- Only single 5V source needed for programming capability

- In-Circuit Debugging via two pins

- Processor read/write access to program memory

- Wide operating voltage range: 2.5V to 5.5V

- High Sink/Source Current: 25 mA

- Commercial and Industrial temperature ranges

- Low-power consumption:

< 2mA typical @ 5V, 4 MHz

20mA typical @ 3V, 32 kHz

< 1mA typical standby current

#### PERIPHERAL FEATURES:

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during sleep

Via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules

Capture is 16-bit, max resolution is 12.5 ns,

Compare is 16-bit, max resolution is 200 ns,

PWM max. Resolution is 10-bit

- 10-bit multi-channel Analog-to-Digital converter

- Synchronous Serial Port (SSP) with SPI. (Master Mode) and I2C. (Master/Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with

- 9- Bit addresses detection.

- Brown-out detection circuitry for Brown-out Reset (BOR).

# **APPENDIX**

```

TMR1ON=1;count=0;

RC0=0;RC1=1:

while(1)

{

//

PORTB=0x00:

//

while(!count);count=0;

PORTB=0x01;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=~RC3;RC4=~RC4;

PORTB=0x02;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=\sim RC3;RC4=\sim RC4:

PORTB=0x03;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=~RC3;RC4=~RC4;

PORTB=0x04;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=~RC3;RC4=~RC4;

PORTB=0x05;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=\sim RC3;RC4=\sim RC4:

PORTB=0x06;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=\sim RC3;RC4=\sim RC4;

PORTB = 0x07; TMR1H = 0X0f; TMR1L = 0Xaf; count = 0; TMR1ON = 1; while (!count); TMR1DN = 1; while (!count); while (!count); while (!count);

ON=0;RC3=~RC3;RC4=~RC4;

PORTB=0x06;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=\sim RC3;RC4=\sim RC4;

PORTB=0x05;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=\sim RC3;RC4=\sim RC4;

PORTB = 0x04; TMR1H = 0X0f; TMR1L = 0Xaf; count = 0; TMR1ON = 1; while (!count); TMR1DN = 1; while (!count); while (!count); while (!count); while (!count); while (!cou

ON=0;RC3=\sim RC3;RC4=\sim RC4;

PORTB = 0x03; TMR1H = 0X0f; TMR1L = 0Xaf; count = 0; TMR1ON = 1; while (!count); TMR1DN = 1; while (!count); while (!count); TMR1DN = 1; while (!count); while (!count);

```

$ON=0;RC3=\sim RC3;RC4=\sim RC4:$

```

PORTB=0x02;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC3=~RC3;RC4=~RC4;

PORTB=0x01;TMR1H=0X0f;TMR1L=0Xaf;count=0;TMR1ON=1;while(!count);TMR1

ON=0;RC0=~RC0;RC1=~RC1;

}

```

2853.

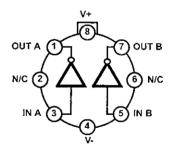

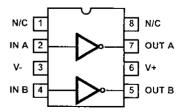

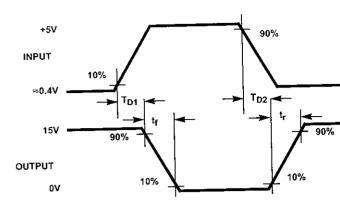

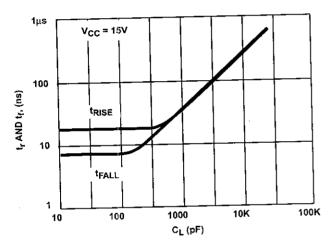

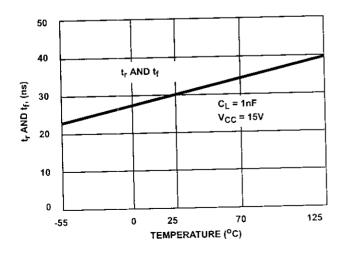

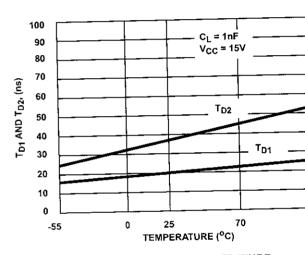

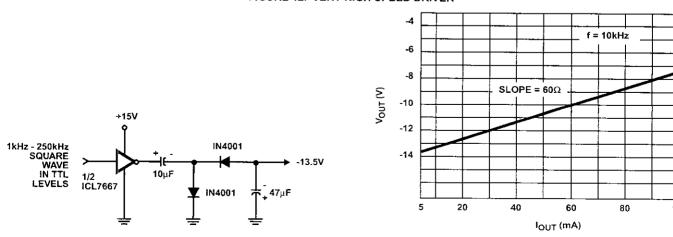

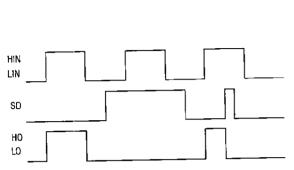

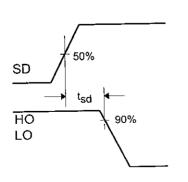

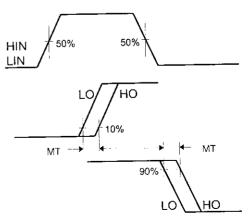

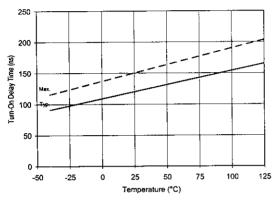

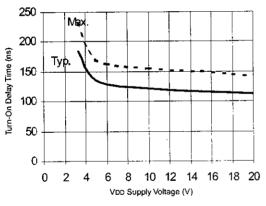

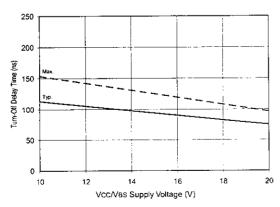

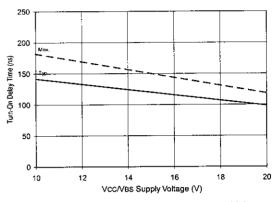

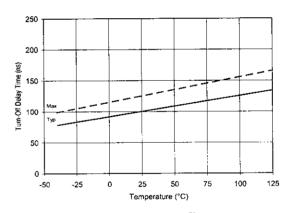

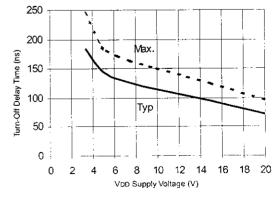

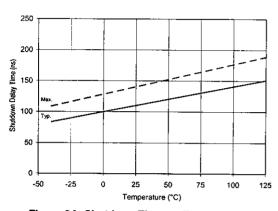

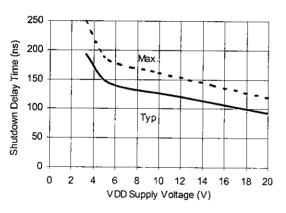

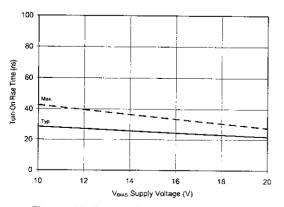

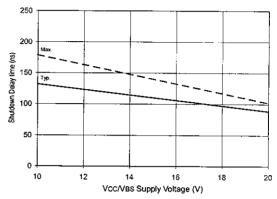

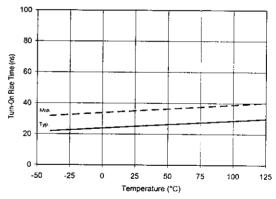

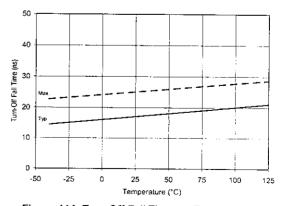

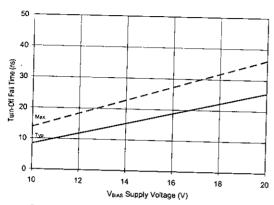

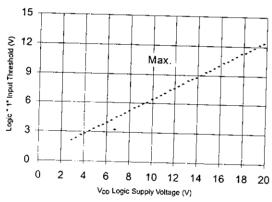

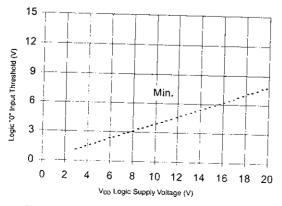

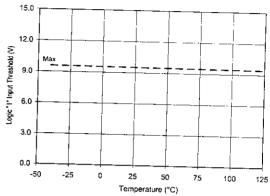

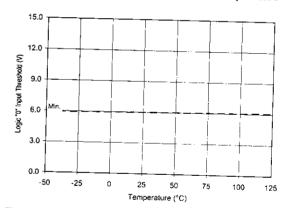

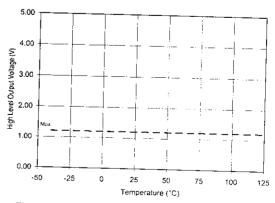

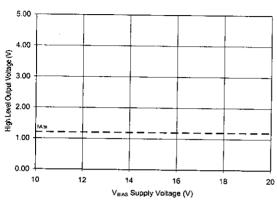

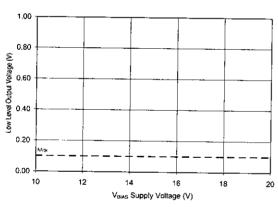

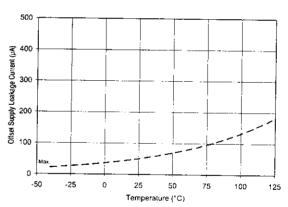

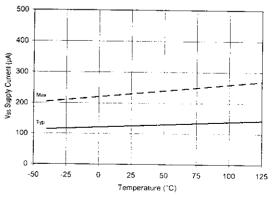

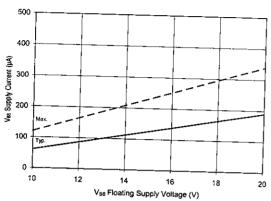

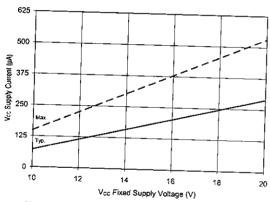

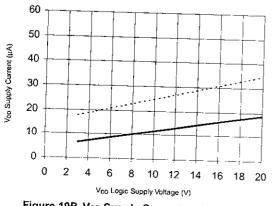

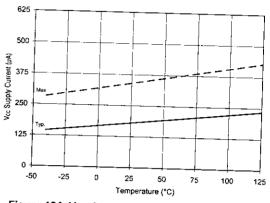

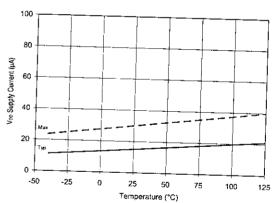

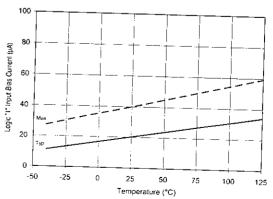

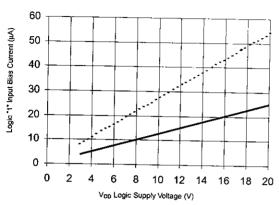

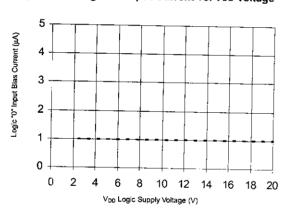

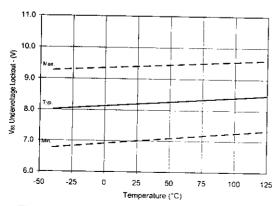

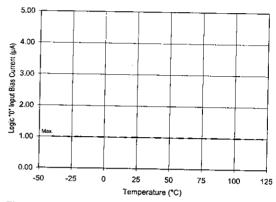

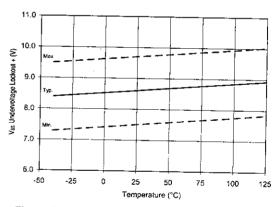

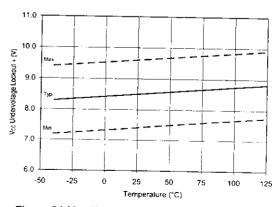

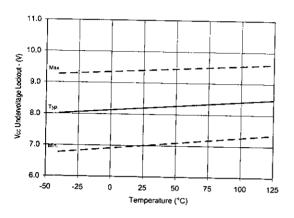

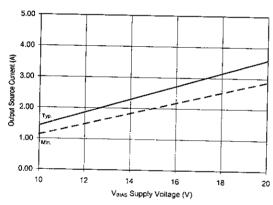

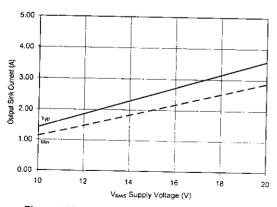

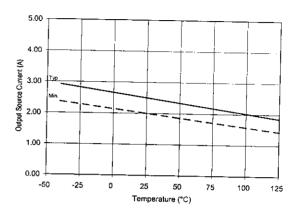

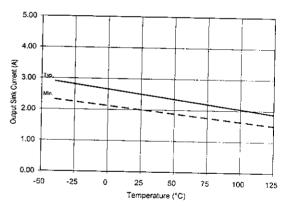

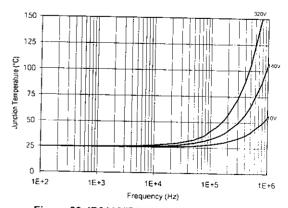

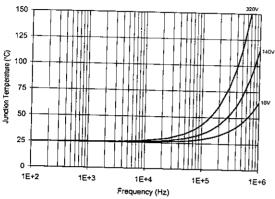

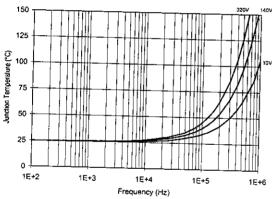

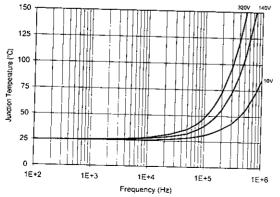

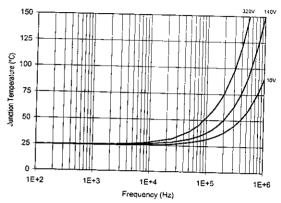

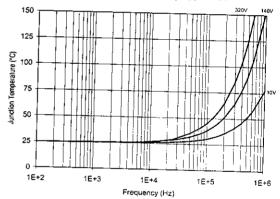

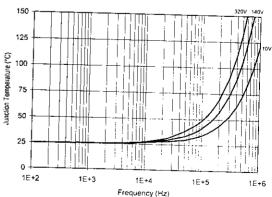

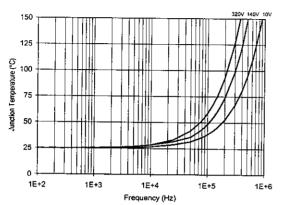

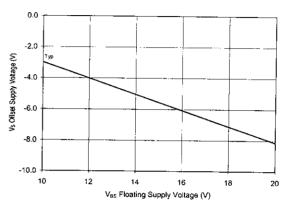

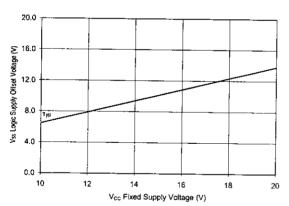

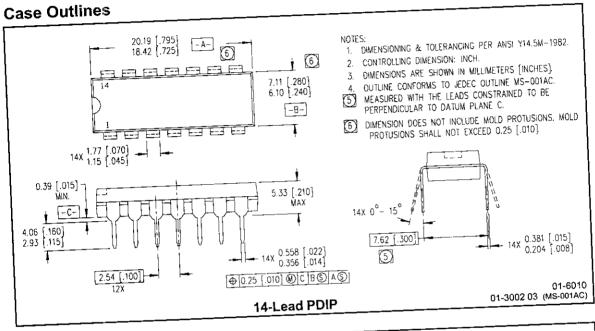

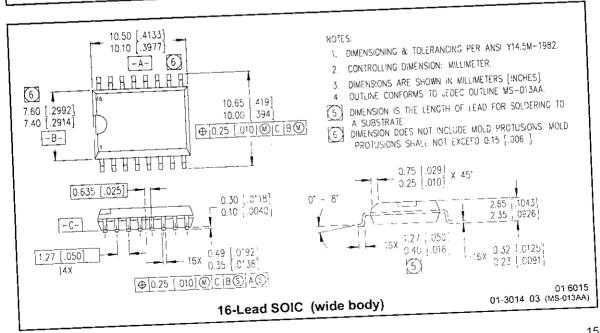

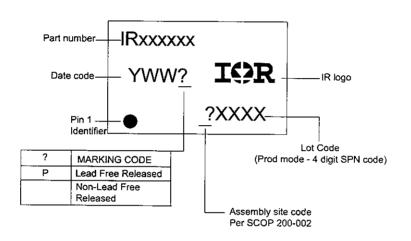

#### Dual Power MOSFET Driver

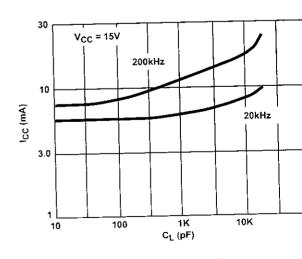

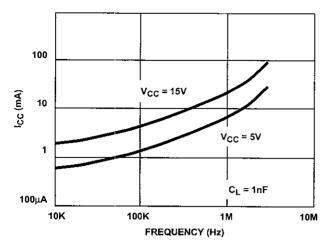

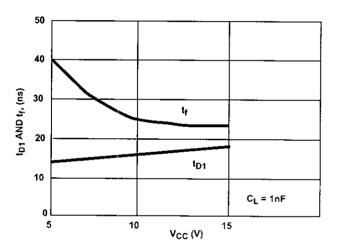

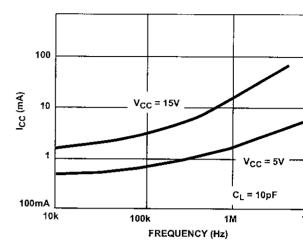

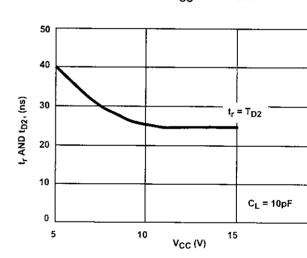

The ICL7667 is a dual monolithic high-speed driver designed to convert TTL level signals into high current outputs at voltages up to 15V. Its high speed and current output enable it to drive large capacitive loads with high slew rates and low propagation delays. With an output voltage swing only millivolts less than the supply voltage and a maximum supply voltage of 15V, the ICL7667 is well suited for driving power MOSFETs in high frequency switched-mode power converters. The ICL7667's high current outputs minimize power losses in the power MOSFETs by rapidly charging and discharging the gate capacitance. The CL7667's inputs are TTL compatible and can be directly driven by common pulse-width modulation control ICs.

#### Ordering Information

| PART<br>NUMBER        | TEMP. RANGE<br>(°C) | PACKAGE         | PKG. NO. |

|-----------------------|---------------------|-----------------|----------|

| CL7667CBA             | 0 to 70             | 8 Ld SOIC (N)   | M8.15    |

| CL7667CPA             | 0 to 70             | 8 Ld PDIP       | E8.3     |

| CL7667CJA             | 0 to 70             | 8 Ld CERDIP     | F8.3A    |

| CL7667CTV             | 0 to 70             | 8 Pin Metal Can | T8.C     |

| CL7667MTV<br>(Note 1) | -55 to 125          | 8 Pin Metal Can | T8.C     |

| CL7667MJA<br>(Note 1) | -55 to 125          | 8 Ld CERDIP     | F8.3A    |

#### NOTE:

1. Add /883B to Part Number for 883B Processing

### Functional Diagram

#### Features

- · Fast Rise and Fall Times

- 30ns with 1000pF Load

- · Wide Supply Voltage Range

- V<sub>CC</sub> = 4.5V to 15V

- · Low Power Consumption

- 4mW with Inputs Low

- 20mW with Inputs High

- · TTL/CMOS Input Compatible Power Driver

- R<sub>OUT</sub> = 7Ω Typ

- · Direct Interface with Common PWM Control ICs

- Pin Equivalent to DS0026/DS0056; TSC426

#### **Applications**

- Switching Power Supplies

- DC/DC Converters

- · Motor Controllers

#### **Pinouts**

TOP VIEW

ICL7667 (PDIP, SOIC, CERDIP)

TOP VIEW

#### ICL7667

#### **Absolute Maximum Ratings**

####

#### **Operating Temperature Range**

| Operating reinperature itange |  |

|-------------------------------|--|

| ICL7667C0°C to 70°C           |  |

| ICL7667M55°C to 125°C         |  |

#### Thermal Information

| Thermal Resistance (Typical, Note 2)                           | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> ( <sup>c</sup> |

|----------------------------------------------------------------|------------------------|--------------------------------|

| PDIP Package                                                   | 150                    | N                              |

| SOIC Package                                                   | 170                    | N                              |

| Metal Can Package                                              | 156                    | 6                              |

| CERDIP Package                                                 | 115                    | 3                              |

| Maximum Storage Temperature Range                              | 65                     | °C to                          |

| Maximum Lead Temperature (Soldering 19 (SOIC - Lead Tips Only) | 0s)                    |                                |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

2.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications**

|                       |                  |                                                                                     | IC                       | L7667C | , M  | 1                              | CL7667N | Л   |          |

|-----------------------|------------------|-------------------------------------------------------------------------------------|--------------------------|--------|------|--------------------------------|---------|-----|----------|

|                       |                  |                                                                                     | T <sub>A</sub> = 25°C    |        |      | -55°C ≤ T <sub>A</sub> ≤ 125°C |         |     | 1        |

| PARAMETER SYME        |                  | TEST CONDITIONS                                                                     |                          | TYP    | MAX  | MIN                            | TYP     | MAX | UN       |

| DC SPECIFICATIONS     |                  |                                                                                     | •                        | •      |      |                                |         | •   |          |

| Logic 1 Input Voltage | V <sub>IH</sub>  | V <sub>CC</sub> = 4.5V                                                              | 2.0                      | -      | -    | 2.0                            | -       | -   |          |

| Logic 1 Input Voltage | V <sub>IH</sub>  | V <sub>CC</sub> = 15V                                                               | 2.0                      | -      | -    | 2.0                            | -       | -   |          |

| Logic 0 Input Voltage | V₁L              | V <sub>CC</sub> = 4.5V                                                              | -                        | -      | 8.0  | -                              | -       | 0.5 |          |

| Logic 0 Input Voltage | V <sub>IL</sub>  | V <sub>CC</sub> = 15V                                                               | -                        | -      | 8.0  | -                              | -       | 0.5 |          |

| Input Current         | I <sub>IE</sub>  | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 0V and 15V                                 | -0.1                     | -      | 0.1  | -0.1                           | -       | 0.1 | ŀ        |

| Output Voltage High   | V <sub>OH</sub>  | V <sub>CC</sub> = 4.5V and 15V                                                      | V <sub>CC</sub><br>-0.05 | Vcc    |      | V <sub>CC</sub><br>-0.1        | Vcc     | -   |          |

| Output Voltage Low    | V <sub>OL</sub>  | V <sub>CC</sub> = 4.5V and 15V                                                      | -                        | 0      | 0.05 | -                              | -       | 0.1 |          |

| Output Resistance     | Rout             | V <sub>IN</sub> = V <sub>IL</sub> , I <sub>OUT</sub> = -10mA, V <sub>CC</sub> = 15V | -                        | 7      | 10   | -                              | -       | 12  |          |

| Output Resistance     | R <sub>OUT</sub> | V <sub>IN</sub> = V <sub>IH</sub> , I <sub>OUT</sub> = 10mA, V <sub>CC</sub> = 15V  | -                        | 8      | 12   | -                              | -       | 13  |          |