### IMPLEMENTATION OF LDPC DECODER IN FPGA

By MAHESH K R

Reg. No. 0920106008

of

### KUMARAGURU COLLEGE OF TECHNOLOGY

( An Autonomous Institution affiliated to Anna University of Technology, Coimbatore)

**COIMBATORE - 641049**

### A PROJECT REPORT

Submitted to the

# FACULTY OF ELECTRONICS AND COMMUNICATION ENGINEERING

In partial fulfillment of the requirements for the award of the degree

of

MASTER OF ENGINEERING

IN

APPLIED ELECTRONICS

APRIL 2011

DOI WILL DE CENTIFICATE

Certified that this project report entitled "IMPLEMENTATION OF

LDPC DECODER IN FPGA" is the bonafide work of Mr. Mahesh K R [Reg. No.

0920106008] who carried out the research under my supervision. Certified further, that to

the best of my knowledge the work reported herein does not form part of any other

project or dissertation on the basis of which a degree or award was conferred on an earlier

occasion on this or any other candidate.

Project Guide

Ms.G.Amirtha Gowri

Head of the Department

Dr. (Ms.) Rajeswari Mariappan

The candidate with university Register no. 0920106008 is examined by us in the project viva-voce examination held on ... 21-4-2011...

nternal Examiner

External Examiner

A project of this nature needs co-operation and support from many for successful completion. In this regard, we are fortunate to express our thanks to **Padmabhusan** Arutselvar Dr.N.Mahalingam B.Sc.,F.I.E., Chairman and Co-Chairman Dr.B.K.Krishnaraj Vanavarayar B.Com, B.L., for providing necessary facilities for the course.

First I would like to express my praise and gratitude to the Lord, who has showered his grace and blessing enabling me to complete this project in an excellent manner. I express my sincere thanks to our beloved Director **Dr.J.Shanmugam**, Kumaraguru College of Technology, for the kind support and necessary facilities to carry out the project work.

I express my sincere thanks to our beloved Principal **Dr.S.Ramachandran**, Kumaraguru College of Technology, who encouraged and supported me the project work.

I would like to express my sincere thanks and deep sense of gratitude to our HOD, **Dr.Rajeswari Mariappan**, Department of Electronics and Communication Engineering, for the valuable suggestions and encouragement which paved way for the successful completion of the project work.

In particular, I wish to thank and everlasting gratitude to the project coordinator Ms.R.Latha (Ph.D)., Associate Professor, Department of Electronics and Communication Engineering for her expert counseling and guidance to make this project to a great deal of success.

I am greatly privileged to express deep sense of gratitude to my guide Ms.G.Amirtha Gowri (Ph.D)., Associate Professor, Department of Electronics and Communication Engineering, for the valuable suggestions and support throughout the course of this project work. I wish to convey my deep sense of gratitude to all the teaching and non-teaching staff of ECE Department for their help and cooperation.

Finally, I thank my parents and my family members for giving me the moral support and abundant blessings in all of my activities and my dear friends who helped me to endure my difficult times with their unfailing support and warm wishes.

Low Density Parity Check (LDPC) codes are promising error correcting codes. The LDPC H matrix is a sparse matrix. So the memory requirement for this code is very less. This will make the decoding of the LDPC codes very efficient and simple compared to the other error correcting methods. The decoding can be easily done with the help of the tanner graph and message passing algorithm. In this project, the two different decoding methods of LDPC codes are studied. The two methods are hard decision decoding and the soft decision decoding. These two decoding method are analyzed and simulation results are taken from model sim soft ware. For hard decision decoding 6 bit code word is given to the decoder and the performance is analyzed. For hard decision decoding 32 bit code word performance is also analyzed. For soft decision 6 bit code performance is analyzed. LDPC codes give good error correction performance approaching Shannon's limit. Applications of this error correcting codes are in Digital Video Broadcasting (DVB-2), Gigabit Ethernet, and Wireless broadband communication etc.

#### RODE OF CONTENT

| CHAPTER | TITLE                                | PAGE |

|---------|--------------------------------------|------|

| NO.     |                                      | NO.  |

|         | ABSTRACT                             | ív   |

|         | LIST OF TABLES                       | vii  |

|         | LIST OF FIGURES                      | viii |

|         | LIST OF ABBREVIATIONS                | ix   |

| 1       | INTRODUCTION                         | 1    |

|         | 1.1 OVER VIEW                        | 1    |

|         | 1.2 PROJECT GOAL                     | 2    |

|         | 1.3 SOFTWARES USED                   | 3    |

|         | 1.4 ORGANIZATION OF THE REPORT       | 3    |

| 2       | LOW DENSITY PARITY CHECK CODES       | 4    |

|         | 2.1 PARITY CHECK CODES               | 4    |

|         | 2.2 LDPC CODES                       | 5    |

|         | 2.3 REPRASENTION OF LDPC CODES       | 5    |

|         | 2.3.1 MATRIX REPRESENTATION          | 5    |

|         | 2.3.2 GRAPHICAL REPRESENTATION       | 6    |

|         | 2.4 REGULAR AND IRREGULAR LDPC CODES | 7    |

|         | 2.5 CONSTRUCTING LDPC CODES          | 8    |

| 3       | ENCODING AND DECODING OF LDPC        |      |

|         | CODES                                | 9    |

|         | 3.1 ENCODING PROCESS                 | 9    |

|         | 3.2 DECODING OF LDPC CODES           | 10   |

|         | 3.3 MESSAGE PASSING ALGORITHM        | 10   |

|         | 3.4 HARD DECISION DECODING           | 12   |

| 4 | INTRODUCTION TO VHDL           | 21 |

|---|--------------------------------|----|

|   | 4.1 STRUCTURAL DESCRIPTION     | 20 |

|   | 4.1.1 BUILDING BLOCKS          | 20 |

|   | 4.2 DATAFLOW DESCRIPTION       | 22 |

|   | 4.2.1 AN EXAMPLE FOR DATA FLOW | 2. |

|   | APPROACH                       |    |

|   | 4.2.2 THE DELAY MODEL          | 23 |

|   | 4.3 BEHAVIOURAL DESCRIPTION    | 23 |

|   | 4.3.1 THE PROCESS STATEMENT    | 23 |

|   | 4.3.2 USING VARIABLES          | 24 |

|   | 4.3.3 SEQUENTIAL STATEMENTS    | 24 |

|   | 4.3.4 SIGNALS AND PROCESSES    | 24 |

|   | 4.3.5 PROGRAM OUTPUT           | 24 |

|   |                                |    |

| 5 | SIMULATION RESULTS             | 25 |

|   |                                |    |

| 6 | CONCLUSION                     | 30 |

|   |                                |    |

|   | REFERENCES                     | 31 |

|   | ·                              |    |

|   | APPENDIX I                     | 34 |

|   | APPENDIX II                    | 37 |

.........

| TABLE | NO                     | CAPTION                                | PAGE NO |

|-------|------------------------|----------------------------------------|---------|

| 5.1   | Synthesis report of 6  | bit code length hard decision algorith | nm 30   |

| 5.2   | Synthesis report of 3. | 2 bit code length hard decision algori | thm 30  |

#### 131 OF FIGURES

| FIGURE | CAPTION                                                    |    |

|--------|------------------------------------------------------------|----|

| NO     |                                                            | NO |

| 2.1    | Tanner graph representation of parity check matrix         | 6  |

| 3.1    | Representation of parity check constrain of LDPC codes     |    |

| 3.2    | Initialization of the bit nodes                            |    |

| 3.3    | Check node message updates                                 |    |

| 3.4    | Variable-node update                                       |    |

| 3.5    | Decision making                                            |    |

| 3.6    | Intrinsic and Extrinsic information transfer between bit   |    |

| -      | nodes and the check nodes                                  | 20 |

| 4.1    | Data flow approach in SR latch                             | 23 |

| 5.1    | Simulated output for the code word [1 0 1 0 1 1]           | 26 |

| 5.2    | Simulated output for code word [0 0 1 0 1 1]               | 27 |

| 5.3    | Simulated output for 32 bit code word length hard decision |    |

|        | decoding                                                   | 28 |

| 5.4    | Simulated output for soft decision decoding                | 29 |

| ВСН  |             | Bose_ Chaudhuri_Hocquenghen    |

|------|-------------|--------------------------------|

| DVB  |             | Digital Video Broadcasting     |

| ECC  | <del></del> | Error Correcting Codes         |

| FPGA |             | Field Programmable Gate Array  |

| LDPC |             | Low Density Parity Check Codes |

| MPA  |             | Message Passing Algorithm      |

| RS   | v           | Reed Solomon                   |

#### CHAPTER 1

### INTRODUCTION

#### 1.1 OVERVIEW

Communication systems transmit data from source to destination through a channel or medium such as air, wire line and optical fiber. Reliability of the received data depends on the channel and external noises that could interface or distort the signal representing the data. Noise introduces errors in the received data. Error detection and correction is achieved by adding redundant symbols to the original data. Forward Error Correction Code (FEC) is used for error correction easily without data need to be retransmitted. Retransmission will result in delay, cost and wastes system throughput. Several error correction codes have been developed to improve the reliability of the data transfer. Forward Error Correction Codes (FEC) includes Viterbi, convolution codes, Bose Chaudhuri Hocquenghen (BCH) codes, Reed Solomon (RS) codes, turbo codes and low density parity check codes (LDPC).

Low Density Parity Check (LDPC) codes are a class of linear block codes, shows good error correcting performance approaching Shannon's limit. Good error correcting performance enables efficient and reliable communication. They were first introduced by Gallager in his Ph.D. thesis in 1960. But due to the computational complexity in implementing encoder and decoder for such codes and the introduction of Reed-Solomon codes, they were mostly ignored until about ten years ago. They remained largely neglected for over 35 years. In the mean time the field of forward error correction was dominated by highly structured algebraic block and convolutional codes. Despite the enormous practical success of these codes, their performance fell well short of the theoretically achievable limits set down by Shannon in his seminal 1948 paper. The relative quiescence of the coding field was utterly transformed by the introduction of turbo codes, proposed by Berrou, Glavieux and Thitimajshima, wherein all the key ingredients of successful error correction codes were replaced: turbo codes involve very little algebra, employ iterative, distributed algorithms, focus on average (rather than worst-case) performance, and rely on soft (or probabilistic) information extracted from the channel.

New generalizations of Gallager's LDPC codes by a number of researchers including Luby, Mitzenmacher, Shokrollahi, Spielman, Richardson and Urbanke, produced new irregular LDPC codes which offer certain practical advantages and an arguably cleaner setup for theoretical results. Today, design techniques for LDPC codes exist which enable the construction of codes which approach the Shannon's capacity to within hundredths of a decibel. The main research interests are low complexity encoding and efficient decoding schemes.

The future wireless standards need different scalable properties like multiple code rates, multiple code lengths, fixed code lengths, different throughputs depending on the applications. LDPC codes can be designed to meet the above requirements. In addition to the strong theoretical interest in LDPC codes, such codes have already been adopted in satellite-based digital video broadcasting and long-haul optical communication standards, are highly likely to be adopted in the IEEE wireless local area network standard, and are under consideration for the long-term evolution of third generation mobile telephony. The idea behind these codes dates back to the sixties, but recently such coding schemes has been given a fresh analysis and it has been shown that they can approach the information theoretical limits at unprecedented low complexity. The name Low Density comes from the characteristic of their parity-check matrix which contains only a few 1's in comparison to the number of 0's. Their main advantage is that they provide a performance which is very close to the capacity for a lot of different channels and linear time algorithms for decoding. Furthermore they are suited for implementations that make heavy use of parallelism. They use parallel decoding and the simple computation operations are the main advantage of the LDPC codes.

### 1.2 PROJECT GOAL

The project aim is to implement the LDPC decoder in FPGA. In this project, hard decision decoding and the Soft decision decoding algorithms are analyzed in detail. Both algorithms are simulated using model sim soft ware. Hard decision decoding algorithm for 6 bit codeword and 32 bit code word are implemented in FPGA

### 1.3 SOFTWARES USED

- ➤ ModelSim PE 5.4e

- ➤ Xilinx ISE 9.2i

- ➤ Matlab R2008b

### 1.4 ORGANIZATION OF THE REPORT

- Chapter 2 discusses about the LDPC codes.

- Chapter 3 deals with the encoding and decoding of LDPC codes

- Chapter 4 gives the introduction to VHDL language

- Chapter 5 presents the simulation results

- Chapter 6 gives the conclusion and future scope

### **CHAPTER 2**

### LOW DENSITY PARITY CHECK CODES

### 2.1 PARITY CHECK CODES

In communication systems the noise are added when the messages are passed over the channel. So different error correcting methods are introduced. Parity check method of error correction is one of the simplest methods. In parity check method we will only consider binary messages and so the transmitted messages consist of strings of 0's and 1's. The essential idea of forward error control coding is to augment these message bits with deliberately introduced redundancy in the form of extra check bits to produce a codeword for the message. These check bits are added in such a way that code words are sufficiently distinct from one another that the transmitted message can be correctly inferred at the receiver, even when some bits in the codeword are corrupted during transmission over the channel.

The simplest possible coding scheme is the single parity check code (SPC). The SPC involves the addition of a single extra bit to the binary message, the value of which depends on the bits in the message. In an even parity code, the additional bit added to each message ensures an even number of 1s in every codeword. More formally, for the 7-bit ASCII plus even parity code we define a codeword c to have the following structure:

$$c = \{c1 \ c2 \ c3 \ c4 \ c5 \ c6 \ c7 \ c8\}$$

(2.1)

Where each ci is either 0 or 1, and every codeword satisfies the constraint

$$c1 \oplus c2 \oplus c3 \oplus c4 \oplus c5 \oplus c6 \oplus c7 \oplus c8 = 0 \tag{2.2}$$

Equation (2.2) is called a parity-check equation, in which the symbol  $\oplus$  represents modulo-2 addition.

While the inversion of a single bit due to channel noise can easily be detected with a single parity check code, this code is not sufficiently powerful to indicate which bit, or indeed bits, were inverted. Moreover, since any even number of bit inversions produces a string

satisfying the constraint (2.2), patterns of even numbers of errors go undetected by this simple code. Detecting more than a single bit error calls for increased redundancy in the form of additional parity bits and more sophisticated codes contain multiple parity-check equations and each codeword must satisfy every one of them.

### 2.2 LDPC CODES

Low Density Parity Check (LDPC) codes are error checking and correcting codes, which show good error correcting performance approaching Shannon's limit. The matrix 'H' is called a parity-check matrix. In LDPC codes the H matrix is sparse. The number of ones in the matrix is lesser compared to the number of zeroes. Each row of H corresponds to a parity-check equation and each column of H corresponds to a bit in the codeword. Thus for a binary code with m parity-check constraints and length n codeword the parity-check matrix is an  $m \times n$  binary matrix

### 2.3 REPRESENTATION OF LDPC CODES

Basically there are two different possibilities to represent LDPC codes. Like all linear block codes they can be described in two ways

- Matrix representation.

- Graphical representation.

#### 2.3.1 Matrix Representation

The parity check constrain can be represented in the form of matrix with 1's and 0's. The matrix given in eqn (2.3) is a parity check matrix with dimension  $n \times m$  for a (6, 2) code. We can now define two numbers describing these matrixes.  $W_r$  (row weight) represent the number of 1's in each row and  $W_c$  (column weight) represent number of ones in each column. For a matrix to be called low-density the two conditions  $W_c \ll n$  and  $W_r \ll m$  must be satisfied.

$$H = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 \end{bmatrix}$$

(2.3)

The matrix H is called a parity-check matrix. Each row of H corresponds to a parity-check equation and each column of H corresponds to a bit in the codeword. Thus for a binary code with 'm' parity-check constraints and length 'n' codeword's the parity-check matrix is an  $m \times n$  binary matrix. The matrix is called sparse since the number of ones in the matrix is less compared to the number of zeroes. In matrix form a string  $y = [c1 \ldots cn]$  is a valid codeword for the code with parity-check matrix H if and only if it satisfies the matrix equation  $Hy^T = 0$ .

Matrix G is called the generator matrix of the code. The message bits are conventionally labeled by u = [u1, u2, ..., uk], where the vector [u] holds the [k] message bits. Thus the codeword c corresponding to the binary message u = [u1u2u3] can be found using the matrix equation c = uG. For a binary code with [k] message bits and length [n] code words the generator matrix, G, is a  $k \times n$  binary matrix. The ratio k/n is called the rate of the code. A code with [k] message bits contains [2] code words. These code words are a subset of the total possible [2] binary vectors of length [n].

### 2.3.2 Graphical Representation

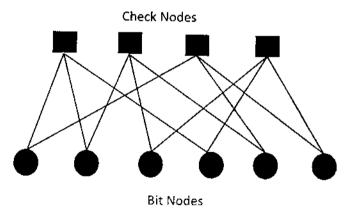

Tanner introduced an effective graphical representation for LDPC codes. This way of representing the codes is called the Tanner graph. Tanner graph methods are very easy in implementing the message passing between the nodes and the LDPC decoding

Figure 2.1: Tanner graph representation of parity check matrix

Tanner graphs are bipartite graphs. That means that the nodes of the graph are separated into two distinctive sets and edges are only connecting nodes of two different types. The two types of nodes in a Tanner graph are called variable nodes (v-nodes) and check nodes (C-nodes). Figure 2.1 is an example for such a Tanner graph and represents the same code as the matrix in (2.3). The creation of such a graph is straight forward. It consists of m check nodes (the number of parity bits) and n variable nodes (the number of bits in a codeword). Check node fi is connected to variable node  $c_i$  if the element  $h_{ii}$  of H is a 1.

The graph representation is analogous to a matrix representation by looking at the adjacency matrix of the graph, let H be a binary m x n matrix in which the entry (i; j) is 1 if and only if the i<sup>th</sup> check node is connected to the j<sup>th</sup> message node in the graph. Then the LDPC code defined by the graph is the set of vectors c = (c1....cn) such that  $H^*c^T = 0$ . The matrix H is called a parity check matrix for the code. Conversely, any binary m x n matrix gives rise to a bipartite graph between 'n' message and 'm' check nodes, and the code defined as the null space of H is precisely the code associated to this graph. Therefore, any linear code has a representation as a code associated to a bipartite graph (note that this graph is not uniquely defined by the code). However, not every binary linear code has a representation by a sparse bipartite graph if it does, then the code is called a low-density parity-check (LDPC) code. The sparsity of the graph structure is key property that allows for the algorithmic efficiency of LDPC codes

### 2.4 REGULAR AND IRREGULAR LDPC CODES

An LDPC code is called regular if  $W_c$  is constant for every column and  $W_c = W_c * (n/m)$  is constant for every row. The example matrix from equation (2.3) is regular with  $W_c = 2$  and  $W_r = 3$ . It's also possible to see the regularity of this code while looking at the graphical representation. There is the same number of incoming edges for every v-node and also for all the c-nodes. If the numbers of 1's in each row or column aren't constant, then the code is called an irregular LDPC code. The parity check matrix of LDPC codes is either regular or irregular. But the irregular LDPC parity check matrix gives better performance.

### 2.5 CONSTRUCTION OF LDPC CODES

Several different algorithms exist to construct suitable LDPC codes. Gallager introduced one. Furthermore MacKay proposed one to semi-randomly generate sparse parity check matrix. This is quite interesting since it indicates that constructing good performing LDPC codes is not a problem. In fact, completely randomly chosen codes are good with a high probability. The problem that will arise is that the encoding complexity of such codes is usually rather high.

LDPC codes can be constructed in two ways they are

- Random construction

- MacKay Constructions

- Bit filling Algorithm

- Progressive Edge-Growth Algorithm

- Structured construction

- Combinatorial Designs

- Finite Geometry Designs

- Algebraic Methods

These are the methods to construct the LDPC codes. In random construction, the H matrix is generated randomly. Therefore the number of ones in the row and the column need not be same. But in the structured construction the numbers of ones are arranged in a structured way. Tregular constructed LDPC codes will give better performance than the regular constructed LDPC codes

### **CHAPTER 3**

## ENCODING AND DECODING OF LDPC CODES

### 1 ENCODING PROCESS

The LDPC encoder transforms each input message block 'u' into a distinct N-tuple (N-bit equence) code word 'c'. The codeword length N, where N > K, is then referred to as the blockingth. And, there are  $2^k$  distinct code words corresponding to the  $2^K$  message blocks. This set of the  $2^K$  code words is termed as a C(N,K) linear block code. The word linear signifies that the hodulo-2 sum of any two or more code words in the code C(N,K) is another valid codeword, the number of non-zero symbols of a codeword 'c' is called the weight, while the number of bit-ositions in which two code words differ is termed as the distance. The minimum distance of a near code is denoted by  $d_{min}$ , and determined by the weight of that codeword in the code C(N,K), which has the minimum weight.

The unique and distinctive nature of the code words implies that there is a one-to-one napping between a K-bit information sequence 'u' and the corresponding N-bit codeword 'c' lescribed by the set of rules of the encoder.

A generator matrix 'G' is determined by performing Gauss-Jordan elimination on 'H' to obtain it in the form:

$$H' = \left[ A, I_{N-K} \right] \tag{3.1}$$

Where 'A' is a (N-K)  $\times$  K binary matrix and  $I_{N-K}$  is the size N-K identity matrix. The generator natrix is then:

$$G = [A, I_{N-K}] \tag{3.2}$$

Since LDPC codes are linear, a codeword is generated by multiplying the input vector with the generator matrix.

$$c = uG (3.3)$$

Where 'c' is the code word and 'u' is the input vector bits. Since 'G' matrix is not sparse, ne matrix multiplication at the encoder will have complexity in the order of n<sup>2</sup> operations.

### 2.2 DECODING OF LDPC CODES

oits.

The class of decoding algorithms used to decode LDPC codes is collectively termed nessage-passing algorithms (MPA) since their operation can be explained by the passing of nessages along the edges of a Tanner graph. Each Tanner graph node works in isolation, only naving access to the information contained in the messages on the edges connected to it. The message-passing algorithms are also known as iterative decoding algorithms as the messages bass back and forward between the bit and check nodes iteratively until a result is achieved (or the process halted). Different message-passing algorithms are named for the type of messages bassed or for the type of operation performed at the nodes. In some algorithms, such as bit-flipping decoding, the messages are binary and in others, such as belief propagation decoding, the messages are probabilities which represent a level of belief about the value of the code word

It is often convenient to represent probability values as log likelihood ratios, and when this is done belief propagation decoding is often called sum-product decoding since the use of log likelihood ratios allows the calculations at the bit and check nodes to be computed using sum and product operations. The decoding algorithms are normally classified in to two they are hard decision algorithm and Soft decision algorithms. Soft decision algorithm which is based on the concept of belief propagation gives better decoding performance and therefore is a preferred method. The decoding can be done iteratively since the parity check matrix is sparse the LDPC codes have less complexity compared with Turbo codes

### 3.3 MESSAGE PASSING ALGORITHM

The messages passed along the Tanner graph edges are straightforward: a bit node sends the same outgoing message M to each of its connected check nodes. This message, labeled Mi. for the i-th bit node, declares the value of the bit '1' or '0'. The check nodes send back different messages to each of their connected bit nodes. This message, labeled  $E_{j,i}$  for the message from

he j-th check node to the i-th bit node, declares the value of the i-bit '1' or '0' as determined by he j-th check node. If the bit node of an erased bit receives an incoming message which is '1' or 0' the bit node changes its value to the value of the incoming message. This process is until some maximum number of decoder iterations has passed and the decoder gives up.

The advantages of LDPC decoding algorithms are that they will use tanner graph and terative decoding methods. They consist of two sets of nodes check nodes and bit nodes. They both are in different levels, Connected each other. Within one level there is no connection so the parallel processing can be done easily. This will speed up the decoding process

$$H = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 \end{bmatrix}$$

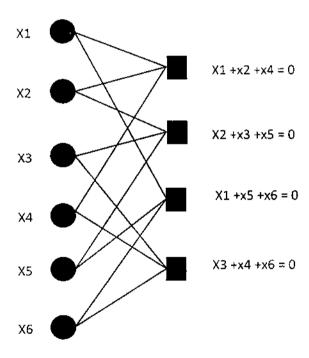

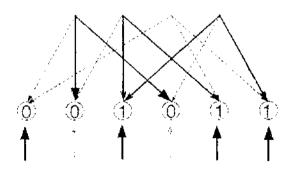

Figure 3.1: Representation of parity check constrain of LDPC codes

The notation  $B_j$  is used to represent the set of bits in the  $j^{th}$  parity-check equation of the code. So for the parity check constrain shown in figure 3.1 we have

$$B_1 = \{1, 2, 4\}$$

$B_2 = \{2, 3, 5\}$   $B_3 = \{1, 5, 6\}$   $B_4 = \{3, 4, 6\}.$

Similarly, we use the notation  $A_i$  to represent the parity-check equations which check on the i<sup>th</sup> bit of the code. So for the parity check constrain shown in figure 3.1 we have

$$A_1 = \{1, 3\}$$

$A_2 = \{1, 2\}$   $A_3 = \{2, 4\}$

$$A_5 = \{1, 4\}$$

$A_5 = \{2, 3\}$   $A_6 = \{3, 4\}.$

Algorithm outlines message-passing decoding on the BEC. Input is the received values from the detector, y = [y1, ..., yn] which can be '1', '0', and output is M = [M1, ..., Mn] which can also take the values '1', '0'.

The datas are sometime send over the erasure channel. The MPA algorithm will help to find the erased bit. Thus the message passing algorithm (MAP) helps to find out the reassured bits at the decoder. This message passing algorithm can be used in erasure channel where the received bits can be '0','1' or x the unknown bit. The specialty of the channel is that it will receive either a receive either a true bit or bit x. It will not produce an error bit. The unknown bit x can be found out by the message passing algorithm by passing of messages between bit nodes and check nodes

### 3.4 HARD DECISION DECODING

The bit-flipping algorithm is a hard-decision message-passing algorithm for LDPC codes. A binary (hard) decision about each received bit is made by the detector and this is passed to the decoder. For the bit-flipping algorithm the messages passed along the Tanner graph edges are also binary. A bit node sends a message declaring if it is a one or a zero, and each check node sends a message to each connected bit node, declaring what value the bit is based on the information available to the check node. The check node determines that its parity-check

quation is satisfied if the modulo-2 sum of the incoming bit values is zero. If the majority of the nessages received by a bit node are different from its received value the bit node changes (flips) ts current value. This process is repeated until all of the parity-check equations are satisfied, or intil some maximum number of decoder iterations has passed and the decoder gives up.

The bit-flipping decoder can be immediately terminated whenever a valid code word has been found by checking if all of the parity-check equations are satisfied. This is true of all nessage-passing decoding of LDPC codes and has two important benefits; firstly additional terations are avoided once a solution has been found, and secondly a failure to converge to a code word is always detected. The bit-flipping algorithm is based on the principle that a code word bit involved in a large number of incorrect check equations is likely to be incorrect itself. The sparseness of H helps spread out the bits into checks so that parity-check equations are inlikely to contain the same set of code word bits. The bit-flipping algorithm applies the hard decision on the received vector,  $y = \{y1, \dots, yn\}$ , and output is  $M = [M1, \dots, Mn]$ .

The steps of the message passing algorithm is given below

Step 1: Initialization

Step 2: Check-node update

Step 3: Variable-node update

Step 4: Decision

#### Step 1: initialization

This is the first phase of MPA. In this phase in tanner graph the bit nodes are assigned the value of the received code word, this can or cannot be true. Then the bit nodes will send the information in to the corresponding check nodes to which they are connected .at the check node exor operations are performed. If all the result of the exor operation is zero then what ever code word we got is the actual code word or else there is an error in the code word which have to be corrected. So messages are passed between the bit nodes and the check nodes

### Initialization

Figure 3.2: Initialization of the bit node

n the case of received bits [101011] the value of the check bits are

$B_0 = 1$

$B_1 = 0$

$B_2 = 1$

$B_3 = 0$

Since all the bits in this case is not zero this is not satisfying the paritycheckequations and this is not the actual code word

Step 2: Check-node update

This is the next step in decoding. The check nodes will send the values they hold to all the bit nodes to which they have connected.  $E_{ij}$  is the value passed from the  $j^{th}$  check node to the  $i^{th}$  bit node. Since one check node is connected to three bit nodes .it will take the incoming value from any two of the bit node and exor in and passed to the third one .this can be summarised in terms of all  $E_{ij}$ 's

$E_{11} = 0$  E31 = 0

$E_{22} = 0$   $E_{12} = 0$

$E_{23} = 1$  E43 = 1

$E_{14} = 1$  E44 = 0

$E_{25} = 1$  E35 = 0

$E_{36} = 0$  E46 = I

Figure 3.3: Check node message updates

Step 3: Variable-node update

The variable node values are up dated by looking the message from the check nodes this will look maximum polling algorithm. That means each bit node will get messages from the two check nodes. That is two bits it can be of four different combinations they are  $\{0,0\}$   $\{0,1\}$   $\{1,0\}$   $\{1,1\}$ , thus if the update from the check nodes are  $\{1,0\}$  or  $\{0,1\}$  whatever we received at the receiver is taken as the correct. But when the received information from the check node are  $\{1,1\}$  by maximum polling algorithm we will take the correct bit as '1' whatever we received. Similarly in the case of  $\{0,0\}$  we will take the error free received bit as '0' for whatever we received

### Bit update

Figure 3.4: Variable-node update

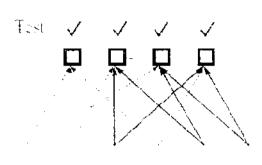

#### Step 4: Decision

In this step the decisions will take. This is that by the new updated value of the received code word will be sending to check nodes again for the checking of correction here we got that all the B values are zero so we represent it by the tic mark. Thus the error correction of the code is done

Figure 3.5: Decision making

Bit-flipping decoding of the received string  $y = [1\ 0\ 1\ 0\ 1\ 1]$ . Each sub-figure indicates the decision made at each step of the decoding algorithm based on the messages from the previous step. A cross represents that the parity check is not satisfied while a tick indicates that it is satisfied. For the messages, a dashed arrow corresponds to the messages "bit = 0" while a solid arrow corresponds to "bit = 1". Thus by repeated message passing between the check nodes and the bit nodes we can finally able to tell the received code word is correct or not. If there is any error in the code word then the algorithm will correct the errors. Since there is no connection with in the bit nodes and the check nodes and only connection between them the iterative decoding is easy in this case

In the previous case the hard decision algorithm is done with 4 x6 parity check matrix. The code word length is 6 bits. Hard decision decoding is extended up to 32 bit code word; the corresponding parity check matrix dimension is  $16 \times 32$ . In the case of LDPC codes as the dimension of the H, the parity check matrix increases, the performance shown by the code is better

### .5 SOFT DECISION DECODING

It is convenient to represent probability values as log likelihood ratios, and when this is one belief propagation decoding is often called sum-product decoding since the use of log kelihood ratios allows the calculations at the bit and check nodes to be computed using sum and troduct operations. Soft decision algorithm which is based on the concept of belief propagation gives better decoding performance and therefore is a preferred method.

The sum-product algorithm is a soft decision message-passing algorithm. It is similar to the bit-flipping algorithm. But with the messages representing each decision (check met, or bit value equal to 1) now probabilities. The sum-product algorithm is a soft decision algorithm which accepts the probability of each received bit as input. The input bit probabilities are called the a priori probabilities for the received bits because they were known in advance before running the LDPC decoder. The bit probabilities returned by the decoder are called the posterior probabilities. In the case of sum-product decoding these probabilities are expressed as log-ikelihood ratios.

For a binary variable x it is easy to find p(x=1) given p(x=0), since p(x=1) = 1-p(x=0) and so we only need to store one probability value for x. Log likelihood ratios are used to represent the metrics for a binary variable by a single value

$$p(x=0) = \frac{p(x=1)/p(x=0)}{1+p(x=1)/p(x=0)} = \frac{e^{-L(x)}}{1+e^{-L(x)}}$$

(3.4)

And

$$p(x=1) = \frac{p(x=0)/p(x=1)}{1+p(x=0)/p(x=1)} = \frac{e^{L(x)}}{1+e^{L(x)}}$$

(3.5)

The benefit of the logarithmic representation of probabilities is that when probabilities and to be multiplied log-likelihood ratios need only be added, reducing implementation omplexity. The sum-product algorithm iteratively computes an approximation of the MAP alue for each code bit. Input is the log likelihood ratios for the a priori message probabilities, the a priori probabilities for the Binary Symmetric channel (BSC) are:

$$ri = \log p/(1-p)$$

if  $y_i = 1$  Or

$$ri = \log(1-p)/(p)$$

if  $y_i = 0$  (3.6)

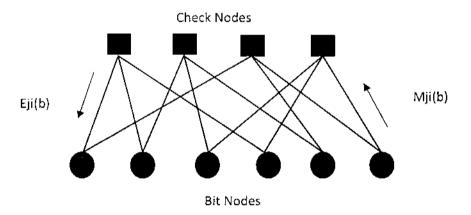

In sum-product decoding the extrinsic message from check node j to bit node i,  $E_{ji}$ , is the LR of the probability that bit i causes parity-check j to be satisfied.

$$E_{j,i} = \log \left( \frac{1 + \prod_{i \in B_j, i \neq i} \tanh(Mj, i/2)}{1 - \prod_{i \in B_j, i \neq i} \tanh(Mj, i/2)} \right)$$

(3.7)

The intrinsic message from check node j to bit node i,  $\mathrm{M_{ji}}$ , is given by,

$$M_{j,i} = \sum_{j \in Ai, j \neq j} E_{j',i} + r_i$$

(3.8)

The total LLR of the bit stream is

$$Li = \sum_{j \in A_i} E_{j,i} + r_i \tag{3.9}$$

The total LLR can be either positive or negative number. The hard decision is taken. When total LLR is positive the decision is '0' else '1'. The code word is z. Then syndrome calculation is done by s=zH'. When s is zero then z is a valid codeword, and the decoding stops, returning z as the decoded word. For an AWGN channel the a priori LLRs are given by

$$r_i = 4y_i(E_s/N_o)$$

(3.10)

The extrinsic LLR and the total LLR calculation are done to find the codeword .

Various steps of Sum Product Decoding algorithm is given below

ocedure DECODE(r)

: 0

ri = 1 : rido

for j = 1: m do

$$M_{j,i} \equiv r_i$$

end for

nd for

epeat

or j = 1 : m do

$\text{for } i \in Bj \text{ do}$

$$E_{j,i} = \log \left( \frac{1 + \prod_{i \in B_j, i \neq i} \tanh \binom{Mj, i}{2}}{1 - \prod_{i \in B_j, i \neq i} \tanh \binom{Mj, i}{2}} \right)$$

end for

end for

for i = 1: n do

$$Li = \sum_{j \in \Lambda i'} E_{j,i} + r_i$$

$$z_i = \begin{cases} 1, L_i \le 0 \\ 0, L_i > 0 \end{cases}$$

end for

for i = 1 : n do

for  $j \in A_i do$

$$M_{j,i} = \sum j' \subseteq A_i, j' \neq j | E_{j',i} + r_i$$

end for

end for

I = I + 1

end if

until Finished

end procedure

Figure 3.6: Intrinsic and Extrinsic information transfer between bit nodes and the check nodes

The figure 3.6 shows the intrinsic and extrinsic information transfer between bit nodes and the check nodes. Finally the total LLR is calculated and the decision is made.

### CHAPTER 4

### INTRODUCTION TO VHDL

VHDL is an acronym which stands for VHSIC Hardware Description Language. VHSIC is yet another acronym which stands for Very High Speed Integrated Circuits. It is being used for documentation, verification, and synthesis of large digital designs. VHDL is a standard (VHDL-1076) developed by IEEE. The different approaches in VHDL are structural, data flow, and behavioral methods of hardware description.

### 4.1 STRUCTURAL DESCRIPTIONS

The structural descriptions are explained below with examples.

### 1.1.1 Building Blocks

An entity declaration, or entity, combined with architecture or body constitutes a VHDL model. VHDL calls the entity-architecture pair a design entity. By describing alternative architectures for an entity, we can configure a VHDL model for a specific level of investigation. The entity contains the interface description common to the alternative architectures. It communicates with other entities and the environment through ports and generics. Generic information particularizes an entity by specifying environment constants such as register size or delay value. For example,

```

entity A is

```

```

port (x, y: in real; z: out real);

generic (delay: time);

```

end A:

The architecture contains declarative and statement sections. Declarations form the region before the reserved word begin and can declare local elements such as signals and components. Statements appear after begin and can contain concurrent statements. For instance,

architecture B of A is

component M

signal a,b,c real := 0.0;

begin

"concurrent statements"

end B;

The variety of concurrent statement types gives VHDL the descriptive power to create and combine models at the structural, dataflow, and behavioral levels into one simulation model. The structural type of description makes use of component instantiation statements to invoke models described elsewhere. After declaring components, we use them in the component instantiation statement, assigning ports to local signals or other ports and giving values to generics. Invert: M port map (j => a; k => c); We can then bind the components to other design entities through configuration specifications in VHDL's architecture declarative section or through separate configuration declarations. The dataflow style makes wide use of a number of types of concurrent signal assignment statements, which associate a target signal with an expression and a delay. The list of signals appearing in the expression is the sensitivity list; the expression must be evaluated for any change on any of these signals. The target signals obtain new values after the delay specified in the signal assignment statement. If no delay is specified, the signal assignment occurs during the next simulation cycle:

$c \le a + b$  after delay;

VHDL also includes conditional and selected signal assignment statements. It uses block statements to group signal assignment statements and makes them synchronous with a guarded condition. Block statements can also contain ports and generics to provide more modularity in the descriptions. We commonly use concurrent process statements when we wish to describe hardware at the behavioral level of abstraction. The process statement consists of declarations and procedural types of statements that make up the sequential program. Wait and assert statements add to the descriptive power of the process statements for modeling concurrent actions:

```

begin

variable i : real := 1.0;

wait on a;

i = b * 3.0;

c <= i after delay;

```

end process:

process

Other concurrent statements include the concurrent assertion statement, concurrent procedure call, and generate statement. Packages are design units that permit types and objects to be shared.

### 4.2 DATA FLOW DESCRIPTIONS

In the data flow approach, circuits are described by indicating how the inputs and outputs of builtin primitive components are connected together.

### 4.2.1 An Example For Data Flow Approach

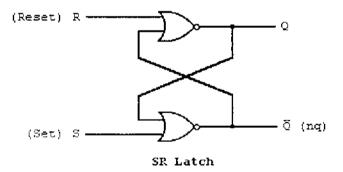

Suppose we were to describe the following SR latch using VHDL as in the following schematic.

Figure 4.1: Data flow approach in SR Latch

entity latch is

```

port (s,r: in bit;

q,nq: out bit);

end latch;

architecture dataflow of latch is

begin

q<=r nor nq:

nq<=s nor q;

end dataflow;</pre>

```

The signal assignment operator in VHDL specifies a relationship between signals, not a transfer of data as in programming languages. The architecture part describes the internal operation of the design. The scheme used to model a VHDL design is called discrete event time simulation. In this the values of signals are only updated when certain events occur and events occur at discrete instances of time. The above mentioned SR latch works with this type of simulation.

### 4.2.2 The Delay Model

This section refers to the delay model. The two models of delay are used in VHDL. The first is called the inertial delay model. The inertial delay model is specified by adding an after clause to the signal assignment statement. The second is called transport delay model.

### 4.3 BEHAVIOURAL DESCRIPTIONS

The behavioural approach to modelling hardware components is different from the other two methods in that it does not necessarily in any way reflect how the design is implemented.

### 4.3.1 The Process Statement

It is basically the black box approach to modeling. It accurately models what happens on the inputs and outputs of the black box, but what is inside the box (how it works) is irrelevant. The behavioral description is usually used in two ways in VHDL. First, it can be used to model complex components.

Behavioral descriptions are supported with the process statement. The process statement can appear in the body of an architecture declaration just as the signal assignment statement

does. The process statement can also contain signal assignments in order to specify the outputs of the process.

### 4.3.2 Using Variables

A variable is used to hold data and also it behaves like you would expect in a software programming language, which is much different than the behavior of a signal. Although variables represent data like the signal, they do not have or cause events and are modified differently. Variables are modified with the variable assignment

### 4.3.3 Sequential Statements

There are several statements that may only be used in the body of a process. These statements are called sequential statements because they are executed sequentially. The types of statements used here are if, if else, for and loop.

### 4.3.4 Signals And Processes

This section is short, but contains important information about the use of signals in the process statement. A signal assignment, if anything, merely schedules an event to occur on a signal and does not have an immediate effect. When a process is resumed, it executes from top to bottom and no events are processed until after the process is complete.

### 4.3.5 Program Output

In most programming languages there is a mechanism for printing text on the monitor and getting input from the user through the keyboard. It can able to give output certain information during simulation. A standard library that comes with every VHDL language system. In VHDL, common code can be put in a separate file to be used by many designs. This common code is called a library. In order to use the library that provides input and output capabilities you must add the statement use textio.all; immediately before every architecture that uses input and output. The write statement can be used to append constant values and the value of variables and signals of the types bit, bit vector, time, integer, and real.

### **CHAPTER 5**

### SIMULATION RESULTS

The message bits are encoded and transmitted over the noisy channel. And at the input of the receiver, the received bits are decoded checked whether they are corrupted or not. The parity check matrix used here is

$$H = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 \end{bmatrix}$$

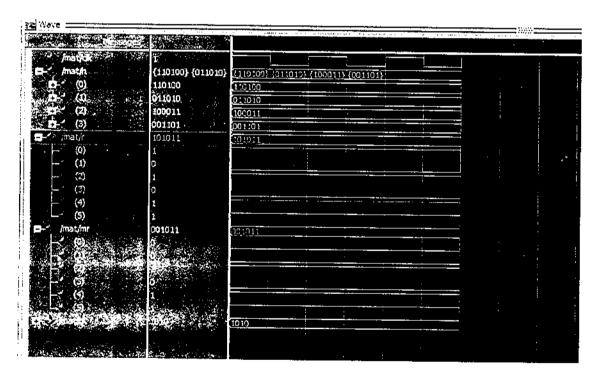

Simulation result for received code word [1 0 1 0 1 1] is shown in figure 5.1. The result shows that this received code word is not correct. It shows that the check node update is initially [1 0 1 0]. And the algorithm will correct the result as [0 0 1 0 1 1], which is the actual code word

Figure 5.1: Simulated output for the code word [1 0 1 0 1 1]

Simulation result for received code word  $[0\ 0\ 1\ 0\ 1\ 1]$  is shown in figure 5.2. The result shows that the check node update here is  $[0\ 0\ 0\ 0]$  so the received code word is correct and it is the actual code word. Here also we are using the same parity check matrix in the above case

$$H = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 \end{bmatrix}$$

Figure 5.2: Simulated output for code word [0 0 1 0 1 1]

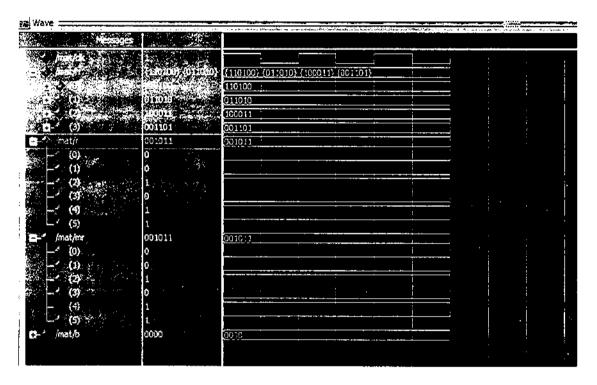

Simulation result of 32 bit code word length hard decision decoding is shown . The parity check matrix used here is of dimension  $16 \times 32$  is shown below

```

010010110100101100001000000000000

01111001011011100000000100000000

01100011010110010000000010000000

01000001100010100000000001000000

01111100100101010100000000000001000

00011010011101110000000000000001

```

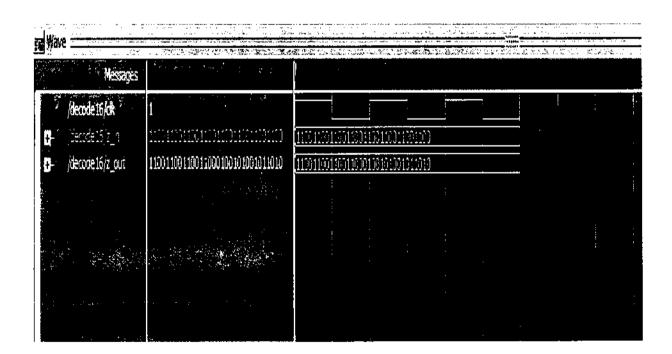

Figure 5.3: Simulated output for 32 bit code word length hard decision decoding

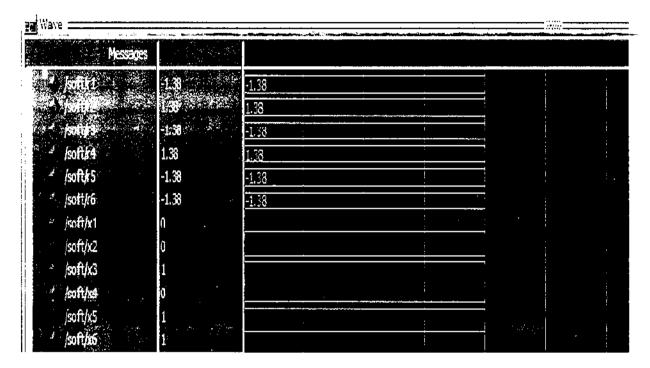

Simulation result of 6 bit soft decision decoding is shown below. The parity check matrix of this is given by

$$H = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 \end{bmatrix}.$$

Figure 5.4: Simulated output for soft decision decoding

Synthesis report of hard decision algorithm is shown below. The first table shows the hard decision algorithm of 6 bit code length and the second table represents the hard decision algorithm of 32 bit code length. Various resources and their utilization is shown in table 5.1 and 5.2.

TABLE 5.1: SYNTHESIS REPORT OF 6 BIT CODE LENGTH HARD DECISION ALGORITHM

| Utilization |

|-------------|

| 27/960= 2%  |

| 22/1960=1%  |

| 46/1920=2%  |

| 37/66=56%   |

| 1/24=4%     |

|             |

TABLE 5.2: SYNTHESIS REPORT OF 32 BIT CODE LENGTH HARD DECISION ALGORITHM

| Resources              | Utilization   |

|------------------------|---------------|

| Number of slices       | 768/1197= 64% |

| Number of 4 input LUTs | 1536/2100=73% |

| Number of bonded IOBs  | 63/64=98%     |

# CHAPTER 6

# **CONCLUSION**

Low density-parity check codes are efficient error correcting codes. These codes can be decoded in iterative way. The iterative decoding approach is already used in turbo codes but the structure of LDPC codes give even better results. In this project, the two different decoding methods of LDPC codes are studied. The two methods are hard decision decoding and the soft decision decoding. These two decoding method are analyzed and simulation results are taken from model sim soft ware. For hard decision decoding both 6 bit code word, of which the parity check dimension  $4 \times 6$  and 32 bit code word of which parity check matrix dimension  $16 \times 32$  are simulated. Usually in case of communication noises are added in between the transmitter and the receiver. So at the receiver the decoding task is very tuff. So at that time priory probability of the received code word is taken as input to the decoder for getting better performance. So we are using soft decision decoding algorithm. In this project 6 bit code word is given to soft decision decoder and performance is analyzed.

# REFERENCES

- 1. Gallager, "Low-density parity-check codes," IRE Transactions on Information Theory, vol. IT-8, no.1, pp. 21–28, January 1962

- 2. R. G. Gallager, "Low-Density Parity-Check Codes". Cambridge, MA:MIT Press, 1963.

- 3. Daesun, "Low Complexity Switch Network for Reconfigurable LDPC Decoder" IEEE Trans. vol.18, no.1, January 2010

- 4. Jin sha, "Multi Gb/s LDPC Code design and implementation" IEEE Trans vol.17. no 2 February 2009

- 5. Chen, "Reduced complexity decoding of LDPC codes" IEEE Trans.commun, vol 53, aug.2005

- 6. T. J. Richardson and R. L. Urbanke, "*The capacity of low-density parity check codes under message passing decoding*," IEEE Trans. Inform. Theory, vol. 47, no. 2, pp. 599–618, February 2001.

- 7. T. J. Richardson and R. L. Urbanke, "Efficient encoding of low-density parity-check codes." IEEE Trans. Inform. Theory, vol. 47, no. 2, pp. 638–656, February 2001.

- 8. D. J. C. MacKay and R. M. Neal, "Near Shannon limit performance of low density parity check codes," Electron. Lett., vol. 32, no. 18, pp. 1645–1646, March 1996, reprinted Electron. Lett, vol. 33(6), pp.457–458, March 1997.

- 9. M. Yang, Y. Li, and W. E. Ryan, "Design of efficiently encodable moderate-length high-rate irregular LDPC codes," IEEE Trans. Commun., vol. 52, pp. 564-571, Apr. 2004

- 10. F.R. Kschischang, B.J. Frey and H.-A. Loeliger, "Factor graphs and the sum-product algorithm", IEEE Trans. Inform. Theory, vol 47, pp. 498-519, Feb. 2001.

- M. Chiani and A. Ventura, "Design and performance evaluation of some high-rate irregular low-density parity-check codes," in IEEE GLOBECOM, 2001, vol. 2, pp. 990-994.

- M.P.C. Fossorier and M. Mihaljevic, "Reduced complexity iterative decoding of lowdensity parity-check codes based on belief propagation," IEEE Trans. Commun., vol. 47, May 1999.

- 13. S. Ten Brink, G. Kramer and A. Ashikhmin. "Design of low-density parity-check codes for modulation and detection", IEEE Trans. Commun., vol. 52, pp. 670-678, April 2004.

- 14. R. Narayanaswami, "Coded modulation with low-density parity-check codes," Master's thesis, Dept. Elect. Eng., Texas A&M Univ., College Station, TX, 2001.

- 15. R. M. Tanner, "A recursive approach to low complexity codes," IEEE Trans. Inform. Theory, vol. IT-27, no. 5, pp. 533-547, September 1981.

- Todd K. Moon, "Error Correction Coding, Mathematical Methods and Algorithms", A John Wiley & Sons, Inc., Publication, New Delhi, India, Ed.2006.

- M. G. Luby, M. Mitzenmacher, A. Shokrollahi, and D. A. Spielman, "Improved low-density parity-check codes using irregular graphs and belief propagation", Technical Report TR-97-044, Berkeley, CA, 1997.

TO THE SECOND PROPERTY OF THE PARTY OF THE PARTY OF

# ModelSim Designer

ModelSun Designer combines case, in use, flexible erration with a powerful contication and deline environment

The Easy to Use Solution for the FPGA Designer

ModelSin.\* Designer is a Windows\*-based design environment for FPGAs, it provides an easy to use, advanced-feeture tool at an entry-level price. The complete process of creation, management, simulation, and implementation are controlled from a single user interface, facilitating the design and verification flow and providing significant productivity gains.

ModelSim Designer combines the industry-leading capabilities of the ModelSim simulator with a built-in design creation engine. To support synthesis and place-and-runte. ModelSim Designer is plug-in ready for the synthesis and place-and-runte tools of your closice. Connection of these additional tools is easy, eiving FPCA designers control of design creation, simulation, synthesis, and place-and route from a single cockpit.

A flexible methodology conforms to existing design thows, Designers can freely mix text entry of VITOL and Verifogessle with graphical entry using block and state diagram editors. A single design unit can be represented in multiple views, and the management of compilation and simulation at all levels of abstraction is a single click away.

Missi moduli fratnissi.

- Project manager is design control, and source code templates and wazards

- · Block and disc frames (2004)

- Intuitive graphical wavetorn, adian

- · Automated texthench creation

- Text to graphic rendering facilitates analysis

- · HERME Decomputation option

- VHOL, Veillog, and reixedlanguage significant

- Optimized native compiled architecture

- Single Kernel Simulator technology

- Advanced debug including Signal Spy\*\*

- · Memory window

- Easy-to-use GUI with Tell interface

- Support for all major synthesis tools and the Actel, Aftera, Lattice, and Xilinx place-and-route flows

- Built-in FPGA vendor fibrary compiler

- Full support for Verilog 2001

- Windows platform support

Options: SWIFT Interpree support, graphics-hosed Dataflew window, Waveform Compare, outograted code coverage, and Profiler (for more details on options, please see the ModelSin SE, datasheet)

www.model.com/modelsimdesigner

In plan antale in their act and development from the prost popular TP to visit the second place can be more than 175 to visit the second place can be more that in the materials. More thanks Designed can either north our tracks. If there was, the docimental of the most one according to the most one accor

#### Project Manager

The leader and power hippings to manager feature allows easy navigation. through a design in order a understand design or manu and execute all necessary tasks. The project manager provides desy access to all design data for each individual festiva onto the noticut tax design process. Exhibite siste suit a place-and-name results, back amounted netlists, and SDF files ere associated. with the relevant design unit. Project ambiy no is a few simple clicks away. allowing complete various outful management at designs. The protect manager also stores user-generated design documents, such as Word. PewerPoint, and PDFs.

#### Templates and Wizards

Creation wizards walk users through the creation of VHOL and Verlog designants as incompetitive factor graphics. In the case of the graphical editor, HDL code is generated from the graphical diagrams created. For text-based design, VHDL and Verlog templates and wizar is help engineers quickly description. HOL case without having to remember the exact tanguage syntax. The wizards show how to create perameterizable logic blocks, estbench it mall, and design objects, Novice and advanced UDL developers both hencius from time giving shortents.

For Block Diagram editor is a consequent was treatmette postation your design and have the IIII code automatically generated

#### Intuitive Graphical Ecitors

ModelSim Designer includes black diagram and state orachine editors that ensure a consistent coding style, facilitating design reaso and maintenance. These editors are an intuitive, graphical nethodology that flattens the learning curve. This sheatens the time to productivity for designers who are migrating to HDL methodologies or changing their primary design language.

Designers can automatically view or render diagrams from HDL code in Is ook diagrams or state machines. When the code charges, the diagram can be updated insteadly with its acoustics, control. This helps designers understand legacy designs and aids in the designing of current designs.

#### Automated Testbanch Creation

Alexle ISin: Designer offers on unton and machanism for textle nell generaltion. The testbench wizard generates VITOL or Veritag code through a graphical waveform editor, with ou put in either HDL or a TCL script. Users can manually define signals in the waveform editor or use the bulls-in wizard a define the waveforms, bither way, it is intuitive and easy to use and saves considerable time.

## Active Design Visual zation Enhances Simulation Debugging

During live simulation, design analysis capabilities are enhanced through graphical design views. From any diagram window, simulations can be fully executed and controlled. Fuhanced debugging features method graphical breakpoints, signal probing, graphica-to-text-source cross-highlighting animation, and cause malysis. The ability to overlay live simulation results in a graphical context speeds up the debug process by allowing faster problem discovery and source design iterations.

#### HTM - Obsessor assessment

The HTML (Hyperflex, Merkop Limane). The amount of the application with the pile of glows the mental HTML mercha. The offers the emphres. (IDL) is some two decimes the emphres. (IDL) is some two decimes Medicand decimes an ITTSH brower index decimes an ITTSH brower Design Hamilton and decimes an HTML brower and manifested in case HTML brower and manifested in case HTML brower and mercan more standards and decimes and decime and decimes and decime and d

#### Memory Windlew

The man, as window enables fless lible slowing and witching of neurons locations. VIDD and Viniting men stress a glacus extended in the CVT, delivening proverted segrelicial load, and save functionality. The memory window allows pre-landing of memories, thus saving the lines, consuming step of in tiglizing sections of the finalition to taid memories. All functions are available via the engaging line, making them avoilable for scripting.

#### Intelligent GO:

Ar intelligently engineered CCC trakes efficient use or descripted estate. Model Sim Designer's intuitive toxons of enaphied believents (windows, teelbars, nerus, etc.) makes it easy to step through the design flow. There are also wizards in place which help set up the design environment and make using through the design process searcless and efficient.

The State Dilagram Editor used intermetion arimaness were a knowledge through the war one from and to the kither all states were seen best.

# Synthesis and Place-and-Route Integration

The industry's popular FPGA asynthesis tools, such as Meritar Craphies Precision-RTL and most FPGA vendor synthesis tools, can be interrated into ModelSin Designer wit (push butten convenience, Actal Designer and Libero, Altera Quartus, Latice (spf. BVBC), and Xilins ISE place-and-route software are similarly integrated. Place-and-route results, together with SDF information, are automatically managed by ModelSin

Destruer after the process is complete, in aking their reasy for post-place and rente gats-ferel amountion.

#### FPGA Vendor Library Compiler

MisdelSin. Designer provides an inmitive mechanism is compile the necessary verdor fibratics for post-places and-rise te simulation. The compiler detects which TPGA vendor tools have been installed and compiles the necessary libraries as soon as the tool is faunched, taking care of this step one and for all.

Visit our web iste at www.model.com/mousteindesigner for more information.

suggested 2015 Mercul to place a regulation

Committee and an administrative and Memorial episocome of contract and action theory is a food or consistent. As a loss that are to recover to the contract and action to the contract

# APPENDIX II

# Spartan-3 FPGA Family Data Sheet

DS099 Depember 4, 2009

Product Specification

This accument includes at four modules of the Sparranike APBA bywilleneet

#### Module 1:

Spartan-3 FPGA Family: Introduction and Ordering Information

#### DS099-1 (v2.5) December 4, 2009

- Introduction

- Fentures

- Architectural Overview

- Array Sizes and Resources

- User 10 Chart

- Ordering Information

### Module 2:

Spartan-3 FPGA Family: Functional Description

#### DS099-2 (v2.5) December 4, 2009

- Input'Output Blocks (IOBs).

- 03 Overview

- Select O™ Interface /O Standards

- Configurable Logic Blooks (CLBs);

- Black BAM

- Dedicated Vultaliers

- Digital Clock Manager (DCM)

- Clock Network

- Configuration.

Module 3:

Spartable SPGA Faculty: DC site: Switching Characteristics

#### DS099-3 (v2.5) December 4, 2009

- DO Electrical Characteristics

- Accoute Maximum Batings

- Supply Voltage Specifications

- Recommended Operating Conditions

- DC Characteristics

- Switching Characteristics

- Offmag

- nternal Lagic Timing

- DOM Timing.

- Configuration and UTAG Timing.

#### Module 4:

Spartan-3 FPGA Family: Pinout Descriptions

#### DS099-4 (v2.5) December 4, 2009

- Pin Descriptions

- Pin Behavior During Configuration

- Package Overview

- Pinout Tables

- Postarints

MPOFTANT NOTE: Each module has its own Revision History at the end. Use the PDF 'Bookmarks' for easy navigation in this volume.

2009-2009 Xihix, no. Xil NX, the Xilinx kidd. Videx, Sedictin, ISS, and other designated branch included here the inderticate of Xilinx in the United States and other backtives. All other materialists say the property of their respective switch.

DS099 December 4, 2009 Product Specification www.xltinx.com

DS099-1 (v2,5) December 4, 2009

# Spartan-3 FPGA Family: introduction and Ordering Information

Product Specification

#### introduction

The Spartantist family of Fields Eugli, mindae Gote Aireya is specifically designed to meet the riveds of aight volume. aget-sensitive consumer electricitic capitations ( eigntwirember family offers denoties ranging from 50,000 for tive million gystera pased, an sacwa in 📆

The Spartanis family builds in the success of me earner Spartan-IIE family by noreasing the amount of ogloresources, the capabity of internal RAM, the total number of JOs, and the overall level of performance as well as by improving clock management functions. Numerous enhancements derive from the Virtex\*- I plaform technick egy. These Spartabrid TPGA enhancements, combined with advanced process technology, celiver more functionality and bandwiath periodian than was previously possible, setting new standards in the programmable logic industry.

Because of their exceptionally low cost. Spartam3 PDGAs are ideally suited to a wide range of consumer electroniss applications, including breadband access, home networking, display/projection and digital television equipment.

the Spartan-3 family is a superior atternative to mask programmed ASIDs. FPGAs avoid the high initial cost the lengthy development cycles, and the inherent inflexibility of conventional ASICs. Also FFGA programmability permits design apprades in the field with no hardware replacement necessary, on impossibility with ASICs

#### Features

- us wilcost in yr is dag menes, lagai ktilut on tar twit lor ur un d con tu melvo. Kritos apolitos pro Dien timos kipi te 74 890 felgo kali t

- Delices Di Milerenta colorge avit g

- us to 601 . Opinal

- 16924 Mb/s bata transfer rate par 1/2

- 19 anglown tod agna strndarts

- signification (kO standards including LVDS, RSDS

- Teemin abon by Britishy Control 40 Intercoores

- Signal owing ranging from 1,14V to 9,465V Dougle Bata Rate (DOP) support

- DDR DDR2 SDRAM SUPPORT UP TO 333 MOES

- usig e raispureas

- Abundent logic balls with split logister capability wilds rost municipates

- Rest (sekvangad carry logic

- Daglastod 19 x 18 multipliars

- LTAR (tigo competible with FEEE 1849 tin 552

- Salast RAUTY hieratchical memory

- บอ ๒ 1 872 Kbits of total clock RAM

- Up to 520 Kars or fato distributed RAM

- Dieta, Cleak Manager (up to four DCMs)

- Glock skew atmination

- Prequency synthesis

- High resolution phase shifting

- Bight global block lines and abundent feuting

- Fully supported by Xillinx ISE® and WebPACK™ settware development systems

- MicroBloze<sup>th</sup> and <u>PiccBloze<sup>th</sup></u> processor <u>POI<sup>th</sup></u>, <u>PCI</u> Expressi PIPE Endopint, and other IP cores

- Pb-free packaging options

- Automotive Spartan-3 XA Family regiont

Table 1: Summary of Spartan-3 FPGA Attributes

|                       |                 | Eggivalent        | (One       | CLB Array |               | Distributed          | Stock FIAM       |                          |          |                    | Maximum                   |

|-----------------------|-----------------|-------------------|------------|-----------|---------------|----------------------|------------------|--------------------------|----------|--------------------|---------------------------|

| Dovice                | System<br>Cates | Logic<br>Celle(*) | Rows       | Columns   | Total<br>CLB+ | RAN Bits<br>(K-+024) | Eits<br>(K-1024) | Ded cated<br>Multipliers | DC Me    | Maximum<br>User VO | Ditterential<br>I/O Paire |

| XC3S50(2)             | 50K             | 1.728             | 4€         | 12        | 192           | 12K                  | 72K              | 4                        | . 5      | 124                | 56                        |

| XC3S200 <sup>-2</sup> | 200K            | 4,320             | 24         | 20        | -80           | 30K                  | 216K             | 2                        | 4        | 173                | 76                        |

| XC3S400/2             | 400K            | 8 064             | 32         | 29        | 996           | 56K                  | 288K             | 16                       | 4        | 264                | 118                       |

| XC3510000             | * N****         | 17 281            | <u>∸</u> 8 | - 2;      | 1 920         | 120K                 | 43250            | 24                       | -        | 19"                | 175                       |

| X6301500              | 1.59            | 29 952            | -34        | 52        | 3 522         | 200K                 | 570K             | 52                       | <u> </u> | 407                | 221                       |

| XC352000              | 2M              | 43,080            | 30         | - £4      | 5 120         | 320K                 | 720K             | 40                       | - 4      | 565                | 270                       |

| XC3S4000              | 465             | 62,208            | 98         | 72        | 6912          | 492K                 | 728K             | 96                       | 1 4      | 693                | 300                       |

| XC255000              | 5M              | 74 980            | 1-04       | 90        | 5920          | \$20K                | 1 972K           | 104                      | 1 4      | 823                | <b>5</b> 00               |

Notes:

Come Call a compart of the Table (1997) this a D'Electro Equivator Login Calls, aguas Total C. Be' y A Logis Callson R. & 1995 affinir vanos

These devices are available in Ximx Automotive versions as described in DS312. Spartan-3 Automotive XA : PGA Family

© 2005-2009 More for XII NX the Xibbelogs when Squaren SA who hear resign part trains not have a remanded execution from a Little Abstract and the Abstract bases are remanded execution from a Little Abstract bases are remainded to the property of their respective owners.

OS099-1 (v2.5) December 4, 2009 Product Specification

WWW.XLIBX.CODE

# Architectural Overview

The Sparian-3 family aromeoture consists of live fundamental programmable fundational elements:

- Canfigurable Logic Biooks (CLBs) contain RAM-based Locativity Tables (LUTs) to implement logic and storage elements into local services as fileshood or lottched CLBs can be programmed to be form a wide vallety of logical functions as well to storage data.

- Input-Output Bisece : OBs) control the field of data between the IrO and and the internal ratio of the device Each IOB cupports distrect and data flow plus arate operation. Twenty-six differential grial standards, including a gift high-performance differential standards are available as shown in the Iro Digitally Controlled Impedance (DOI) feature provides automatic en-chip terminations, simplifying board designs.

- Block RAM provides data storage in the form of 18-Kb til dual-port blocks.

- Multiplier blocks accept two 16-bit bind y numbers as inputs and calculate the product.

Bigital Cleak Manager (DCM) placks provide self-callerating fully digital solutions for distributing, relaying multiplying, dividing and phase distring cleak agnotic

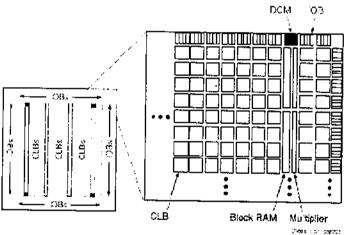

These Hements are proported as they mile 10.1 Air or of OBs surrounds a regular pray of OBs. The XOSSSI had a single column of block RAM embedded in the stroy. Those sewiced ranging nor the XOSSSID to the XOSSSID of the XOSSSID as the XOSSSID of the XOSSID of the XOSSID of the two columns of block RAM. The XOSSID of the column is those up of several 16-Kb t RAM documes. Each column is those up of several 16-Kb t RAM blocks reach block is assistated with a ded cated multiplier. The DOMs are positioned by the each of the pager block RAM columns.

The Sportan-3 family features a rich network of traces and switches that interconnect all time functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

#### Notes:

The two additional block RAM columns of the XC3S4000 and XC3S5000 coxides are shown with dashed thes the XC3S50 has dray the block HAM column contine for left.

Figure 1. Spartan-3 Family Architecture

# Configuration

Spartan-3 FPGAs are programmed by idading penfiguration data into report, repreprendictle, static CMOS configuration latenes. CQLs into delectively control all functional elements and louting resources. Before dowering counteffed appropriation data is one elements yind PROM or some other rows able medium either on or off the poord Attendary in prover the uprhylation data is antitionate. PRGA acting any or one different indext. Moster Facalle Slave Parallet, Moster Seral, Slave Serial, and Boundary Span (TAG). The Macter and Slave Parallet impossible an 8-bitwide SelectMAP port.

The recommended memory for storing the configuration data is the low-post Xilinx Praform Flash PROM family, which includes the XCF00S PROMs for serial configuration and the higher density XCF00P PROMs for parallel or serial configuration.

# 50 Copabilities

The Getect/O feature of Spartan-3 devices subsparts 18 participations of standards and 8 outerent all standards as light on a Many standards outpoint the DC inequality, which uses integrated terminations to eliminate unwanted signal reflections.

Table 2 Signal Standards Supported by the Spartan-3 Family

| Standard<br>Category | Description                                      | <b>∀</b> cco - (V) | Class                 | Symbol<br>(IOSTANDARD) | DCI<br>Option |

|----------------------|--------------------------------------------------|--------------------|-----------------------|------------------------|---------------|

| Single-Ended         |                                                  |                    |                       |                        |               |

| GTL                  | Gunning Transpower Logic                         | NA.                | Tarminatoc            | GTL                    | Vos           |

|                      |                                                  | Γ                  | 위신하                   | GTLP                   | Yas           |

| HST_                 | High-Speed Transpolys ( Dogia                    | 1.5                |                       | ≓S <sup>™</sup> L      | Yos           |

|                      |                                                  | ľ                  | ;                     | ⊣STL I                 | 1708          |

|                      | ·                                                | 1.9                | I                     | ÷STL : 18              | Yea           |

|                      |                                                  | Ţ                  |                       | ≓87L . 13              | Yes           |

|                      |                                                  | ľ                  | Т                     | ∺5TLll_:8              | Yes           |

| EVOMOS               | Low-Voltage CMOS                                 | 1.2                | NA                    | EVCMOS12               | No            |

|                      |                                                  | 1.5                | N/A                   | EVCMOS15               | Yes           |

|                      | ĺ                                                | 1.2                | N/A                   | LVCMOS18               | Yes           |

|                      |                                                  | 2.5                | N'A                   | LVCMOS28               | Yes           |

|                      | ]                                                | 3.3                | N'A                   | LVCMOSSS               | Yas           |

| EVITE                | Low-Voltage Transistor-Transistor Logic          | 9.3                | NA                    | ĻV—L                   | No            |

| PG:                  | Peripheral Component Intersponset                | 9.0                | 35 M≓z <sup>(t)</sup> | PC 33 3                | No            |

| SSTL                 | Stud Series Terminated Logic                     | 1.9                | N/A (35.7 ttA)        | SSTL18 I               | Yes           |

|                      |                                                  | F                  | N'A (±19.4 mA)        | SSTL18                 | No.           |

|                      | i                                                | 2.5                |                       | SSTL2_I                | Yes           |

|                      |                                                  |                    | ij                    | \$STL2_D               | Yes           |

| Differential         | <u></u>                                          |                    |                       |                        |               |

| LDT<br>(ULVDS)       | Lightning Data Transport (HyperTransport™) Logic | 2.5                | N'A                   | LD?_25                 | No            |

| LVOS                 | Low-Voltage Differential Signaling               |                    | Stanicard             | LVDS 25                | Yes           |

|                      | 1                                                |                    | 528                   | EWOS 25                | No            |

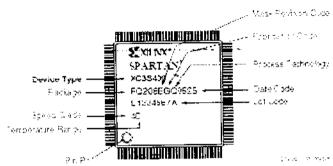

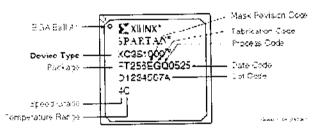

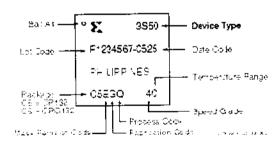

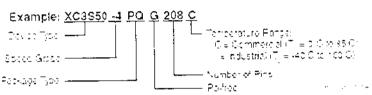

|                      |                                                  | Ţ                  | Extended Mode         | LVDSEXT 25             | Yes           |