# FPGA IMPLEMENTATION OF MODULAR ACTIVE NOISE CONTROL

By

TAMILARASAN.P

Reg. No. 1020106018

of

## KUMARAGURU COLLEGE OF TECHNOLOGY

(An Autonomous Institution affiliated to Anna University, Coimbatoge)

**COIMBATORE - 641049**

## A MINI PROJECT REPORT

Submitted to the

# FACULTY OF ELECTRONICS AND COMMUNICATION ENGINEERING

In partial fulfillment of the requirements for the award of the degree

of

MASTER OF ENGINEERING

IN

APPLIED ELECTRONICS

**MAY 2011**

## **BONAFIDE CERTIFICATE**

Certified that this project report entitled "FPGA IMPLEMENTATION OF MODULAR ACTIVE NOISE CONTROL" is the bonafide work of TAMILARASAN.P [Reg. no. 1020106018] who carried out the research under my supervision. Certified further, that to the best of my knowledge the work reported herein does not form part of any other project or dissertation on the basis of which a degree or award was conferred on an earlier occasion on this or any other candidate.

Project Guide

Mr.S. Venkatesh M.E.,

She tatt.

Head of the Department

Dr. Mrs. Rajeswari Mariappan Ph.D.,

The candidate with university Register no. 1020106018 is examined by us in the project viva-voce examination held on 23.7.95. 2011......

Internal Examiner h

External Examiner

#### **ACKNOWLEDGEMENT**

I express my profound gratitude to our chairman Padmabhusan Arutselvar Dr.N.Mahalingam B.Sc., F.I.E., for giving this opportunity to pursue this course.

At this pleasing moment of having successfully completed the project work. I wish to acknowledge my sincere gratitude and heartfelt thanks to our beloved Principal **Dr.S.Ramachandran**, **Ph.D.**, for having given me the adequate support and opportunity for completing this project work successfully.

I express my sincere thanks to Dr.Ms.Rajeswari Mariappan, Ph.D., Head of the Department of Electronics and Communication Engineering, who rendering us all the time by helps throughout this project

In particular, I wish to thank and everlasting gratitude to the project coordinator Ms.R.Hemalatha, M.E., Asst. professor(SRG). Department of Electronics and Communication Engineering for her expert counseling and guidance to make this project to a great deal of success. With her careful supervision and ensured me in the attaining perfection of work.

I extend my heartfelt thanks to my internal guide Mr S.Venkatesh, M.E., Asst.Professor(SRG) for his ideas and suggestion, which have been very helpful for the completion of this project work.

Last, but not the least, I would like to express my gratitude to my family members, friends and to all my staff members of Electronics and Communication Engineering department for their encouragement and support throughout the course of this project.

## **ABSTRACT**

This project presents the High-speed field programmable gate array (FPGA) implementation of a modular architecture of the Active Noise Control (ANC) system with online secondary path modelling. The clock frequency that is obtained for this FPGA implementation is 120MHz. A comparision of this implementation to other FPGA and DSP implementations of an ANC system shows a better speed up and convergence time for the proposed design.

This innovative modular implementation of the ANC system results in a fast design and fast convergence with capability to expand the four adaptive filters and data bus when higher speed for ANC system. Considering the modularity of the design and reconfigurability of FPGA, one can expand an ANC system for different accuracies and require convergence times.

## TABLE OF CONTENT

| CHAPTER | TITLE                           | PAGE |

|---------|---------------------------------|------|

| NO      |                                 | NO   |

|         | ABSTRACT                        | įv   |

|         | LIST OF FIGURES                 | vi   |

| 1       | INTRODUCTION                    |      |

|         | 1.1 Project Goal                | į    |

|         | 1.2 Overview                    | 1    |

|         | 1.3 Software's Used             | 2    |

|         | 1.4 Organization of the Chapter | 2    |

| 2       | A SUMMARY OF MODULAR ANC SYSTEM | 3    |

| 3       | IMPLEMENTATION                  | 7    |

| 4       | ANC CYSTEM                      | 8    |

| 5       | LMS ALGORITHM                   | 9    |

| 6       | COMPARISION                     | (    |

| 7       | RESULTS & DISCUSSION            | 13   |

| 8       | CONCLUSION                      | 17   |

|         | RIRI IOCDAPHV                   | 15:  |

## LIST OF FIGURES

| FIGURE | CAPTION                                          | PAGE |

|--------|--------------------------------------------------|------|

| NO     |                                                  | NO   |

|        |                                                  |      |

| 2.1    | Architecture of ANC system with online secondary | 4    |

|        | path modeling using four M modules               |      |

| 2.2    | Block diagram of module M                        | 5    |

| 4.1    | ANC system                                       | 8    |

| 5.1    | Flow chart of the LMS Algorithm                  | 9    |

| 5.2    | Flow chart of the FPGA Implementation            | 10   |

| 6.1    | Noise signal                                     | 11   |

| 6.2    | System Performance                               | 12   |

| 7.1    | Simulation Result of the output waveform         | 14   |

| 7.2    | Simulation Result showing gate count used        | 15   |

| 7.3    | Simulation Result of the power used              | 16   |

## INTRODUCTION

The reduction of Acoustic noise has become a serious problem as the number of industrial equipment such as engines, blowers, fans, compressors and transformers are increased. In recent years powerful digital signal processing (DSP) devices have made possible the development of real time ANC systems with a wide range of applications. DSP algorithms have been developed for single and multiple channel ANC systems in branches of broadband, narrowband and adaptive feed-forward control.

## 1.1. PROJECT GOAL

This project proposes the FPGA implementation of the modular architecture of the ANC system. This new modular implementation of the ANC system results in a fast design and fast convergence with capability to expand the four adaptive filters and data bus when higher speed for ANC system is desired.

## 1.2 OVERVIEW

However, with its growing die size as well as incorporating the embedded digital signal processing blocks, the FPGA devices have become a serious contender in the signal processing market. The processor in a DSP approach needs some time to execute the software program. The FPGA approach, in the other hand, performs the tasks on a hardware base and it is faster than the DSP approach. Because of the need for much speed in these systems, FPGA devices are good candidates for these applications.

### 1.3 SOFTWARE USED

- ModelSim XE 111 6.2g

- Xilinx ISE 9.2i

## 1.4 ORGANIZATION OF THE REPORT

- > Chapter 2 discusses about summary of ANC system.

- **Chapter 3** discusses about implemention.

- > Chapter 4 discusses the ANC System.

- > Chapter 5 discusses the LMS Algorithm.

- > Chapter 6 discusses the comparision.

- **Chapter7** discusses the simulation results.

- > Chapter 8 shows the conclusion of the project.

## A Summary of Modular Design of an ANC System

This ANC system has three inputs and one output. The inputs of this ANC system are the reference noise signal, x(n), the injected noise signal, v(n), and the error microphone output, c(n), inputted to the ANC system. The output of this system is the anti-noise signal, which is propagated by the loudspeaker and combines with the primary noise signal to reduce the noise pressure around the error microphone.

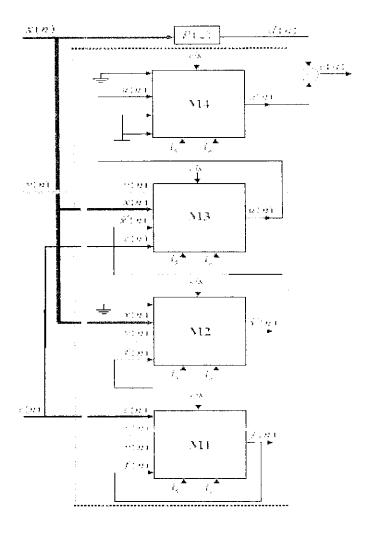

The modular design for this ANC system consists of four similar modules. The architecture of these modules is the same, but their inputs and outputs are different. These four modules are composed to form an ANC system with online secondary path modeling. The detail of this ANC system using the four M modules is shown in Figure 2.1.

In this Figure, P(z) is the primary acoustic path between the reference noise source and the error microphone. The reference noise signal, x(n), is filtered through P(z) and appears as a primary noise signal at the error microphone. The output of the primary path filter, d(n), is the desired output of the ANC system which is the convolution of the reference signal, x(n) and the tap-weights of the primary path FIR filter, P(n), i.e.

$$d(n) = \sum_{k=0}^{N-1} p_k(n) x(n-k)$$

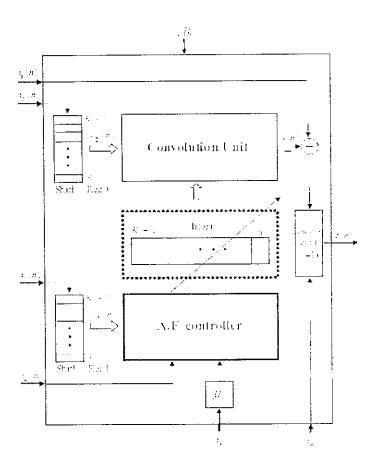

where N, is the length of the primary path FIR filter. The objective of the ANC system is to generate an appropriate anti-noise signal, a(n), propagated by the loudspeaker to create a zone of silence in the vicinity of the error microphone. The module M used in this design has six inputs and one output. The block diagram of this module is shown in Figure 2.2.

Figure 2.1 Architecture of the ANC system with online secondary path modeling using four M modules

Each module consists of two shift registers, a convolution unit, an adaptive filter controller, a 2's complementer, and an adder.

The first input to the module, iI(n), represents the desired output of the adaptive filter at time n. The second input, i2(n), represents the input data to the adaptive filter at time n. The third input, i3(n), represents the modified input data to the adaptive filter at time n. The forth input, i4(n), represents the error data at time n. The fifth input, i5, is the input data to the step size parameter register. The sixth input, i6, is a control signal to negate the output of the module.

The output of the module, z(n), is the difference between the adaptive filter's output and the desired output at time n. Two shift registers with the length of K are installed in the inputs of the block to save and shift the input data and the modified input data at each time n.

Figure 2.2 Block diagram of the module M

The digital filter H(z) contains K tap-weights. The output of this unit at time n is the convolution of the input vector, i2(n) and the tap-weight vector of the filter, h(n).

$$y(n) = \sum_{j=0}^{K-1} h_j(n) i_2(n-j)$$

The tap-weights of this digital filter, hi(n), are updated at each time using the Least Mean Square (LMS) algorithm, i.e.

$$h_k(n+1) = h_k(n) + \mu i_3(n)i_4(n-k), \quad k = 0,...,K-1$$

Where  $\mu$  is the step size in the LMS algorithm, and i3(n) and i4(n) are the input values to the module at time n. If the control input to 2's complementer unit, i6, is one, then the 2's complement of the data input is obtained in the output. The adder in the module subtract the value of the output of the adaptive filter and the input i1(n), i.e.

$$z(n) = i_1(n) - y(n)$$

The output of the adder is the output of the module. Four of these modules are used to form an ANC system with online secondary path modeling as shown in Figure 2.1.

The inputs, output and computations of these four modules are depicted in Table 2.1.

TABLE 2.1: Inputs, output and computations of four modules

|    | i <sub>I</sub> (n) | i <sub>2</sub> (n) | i <sub>3</sub> (n) | i <sub>4</sub> (n) | İ <sub>5</sub> | İ6  | z(n)                                | Con. unit                                                                   | Adaptation                                         |

|----|--------------------|--------------------|--------------------|--------------------|----------------|-----|-------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------|

| M1 | e(x)               | ψ <sub>λ</sub> ,1  | ()                 | Ū                  |                | Û   | $\hat{f}(z) = \rho(z) - \hat{y}(z)$ | $\widehat{Y}(s) = \sum_{n=1}^{M-1} \widehat{S}_n(s) y(n-m)$                 |                                                    |

| M2 | (,)                | 1/8/               | v(સ)               | fhy                | 9              | )   | î'(z)                               | $\hat{X}'(S) = \sum_{m=0}^{M+1} \hat{\mathcal{I}}_{m}(S) \mathbb{E}[(S-S)]$ | 8(n+1) = 8(n)+ д <sub>е</sub> finix(n)             |

| M3 | v(n)               | T(X)               | i(þ                | e(x)               | ·              | 6.5 | y(z) = y(z) + y(z)                  | y(r) = Tw <sub>i</sub> (r sis = ii<br>O                                     | क्षांत्रम् । = क्वर्णम् <sub>(स</sub> ्वर्शात्रीत् |

| M4 | Ú                  | u(n)               | į,                 |                    | Ĵ              | Ū   | a(x) = 1 + a'(x)                    | 4 (n) = 7,5, (n u(n - 1)<br>4 (n) = 7,5, (n u(n - 1)                        | _                                                  |

# CHAPTER 3 IMPLEMENTATION

In this section the modular ANC system with online secondary path modeling is implemented on FPGA

These FPGAs have dedicated multiplier, pipeline and accumulator circuitries. With the embedded DSP blocks, these FPGAs can perform high speed calculations, therefore are useful devices for digital signal processing designs, as well as adaptive filters. The step size parameters of the adaptive control filter,  $\mu w$ , and the adaptive modeling filter,  $\mu_{-}$ , are considered to be 2-11 and 2-6, respectively. All the signals in ANC processor are considered to be floating point numbers with 32 bit length that comprises 11 accuracy bits. The number of used DSP blocks for implementing the ANC system on FPGA is 736 blocks. The clock frequency is 120MHz. A summary of implementation results is shown in Table 3.1.

TABLE 3.1: The number of elements used on Stratix FPGA,  $\mu\nu=2-11$ ,  $\mu=2-6$

| Resource              | Used  | Avail   | Utilization    |

|-----------------------|-------|---------|----------------|

| IOs                   | 103   | 1,171   | 8 ° 5          |

| Registers             | 4.050 | 150,386 | 2 %            |

| ALUT                  | 6.344 | 143,520 | <del>-11</del> |

| DSP block 9-bit clems | 736   | 768     | 95%            |

#### ANC SYSTEM

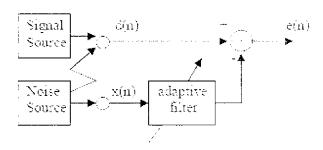

ANC is a technique used to remove an unwanted noise from a received signal, the operation is controlled in an adaptive way in order to obtain an improved signal-to-noise ratio (SNR). As shown in Fig4.1, an ANC is typically a dual-input, closed-loop adaptive feedback system. The two inputsare: the primary input signal d(n) (the desired signal corrupted by the noise) and the reference signal x(n) (an interfering noise supposed to be uncorrelated with the desired signal but correlated with the noise affecting the desired signal in an unknown way). The adaptive filtering operation achieved the best results when the system output is noise free, which means that the output SNR is infinitely large. Therefore, in the application, on obtaining the best result, we should put the reference sensor into the most appropriate place where the signal component of the primary sensor output is undetectable in the reference sensor output and the noise component of the primary sensor output is highly correlated with the reference sensor output.

ANC technique has been successfully applied to many applications, such as acoustic noise reduction, adaptive speech enhancement and channel equalization. In these cases and other related high speed required applications, pure software implementation would bring about long processing time, as shown in the last part of section IV, thus can not meet the requirement. An effective way can be represented by a hardware implementation on FPGA

Figure 4.1 ANC system

## LMS ALGORITHM

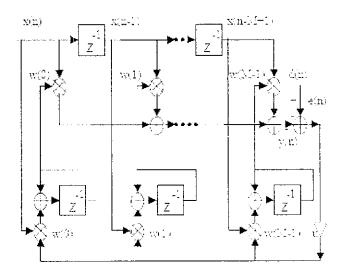

The LMS algorithm is a widely used algorithm for adaptive filtering. The algorithm is described by the following equations:

$$\begin{aligned} y(n) &= \sum_{i=0}^{M-1} |wi(n)|^* |x(n-i)| \\ e(n) &= \dot{c}(n) + y(n) \\ |w_1(n-1)| &= |wi(n)| + 2ne(n)x(n-i), \end{aligned}$$

In these equations, the tap inputs x(n), x(n-1),....,x(n-M+1) form the elements of the reference signal x(n), where M-1 is the number of delay elements. d(n) denotes the primary input signal, e(n) denotes the error signal and constitutes the overall system output. e(n) denotes the tap weight at the nth iteration, the tap weights update in accordance with the estimation error. And the scaling factor u is the step-size parameter, u controls the stability and convergence speed of the LMS algorithm.

Figure 5.1 Flowchart of the LMS Algorithm

The LMS algorithm is convergent in the mean square if and only if  $\boldsymbol{\epsilon}$  satisfies the condition:

$0 \le u \le 2$  / tap-input power where tap-input power,

$$=\sum_{k=0}^{M-1}E\left[\left|H(n-k)\right|^{2}\right]$$

There are usually two ways to implement the LMS algorithm, hardware implementation and software implementation. The hardware implementation of the algorithm in an FPGA has good real-time ability, but requires large resources. From Fig.5.1, we can see that an N-tap adaptive filter requires at least 2N multipliers and 2N adders. The software implementation consumes trivial amount of resources, however, the low speed of which makes it uncommonly used.

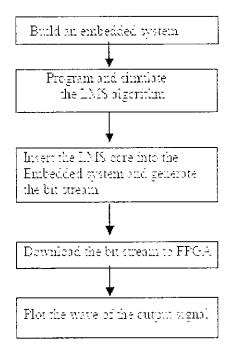

Figure 5.2 Flowchart of the FPGA Implementation Process

## CHAPTER 6 COMPARISION

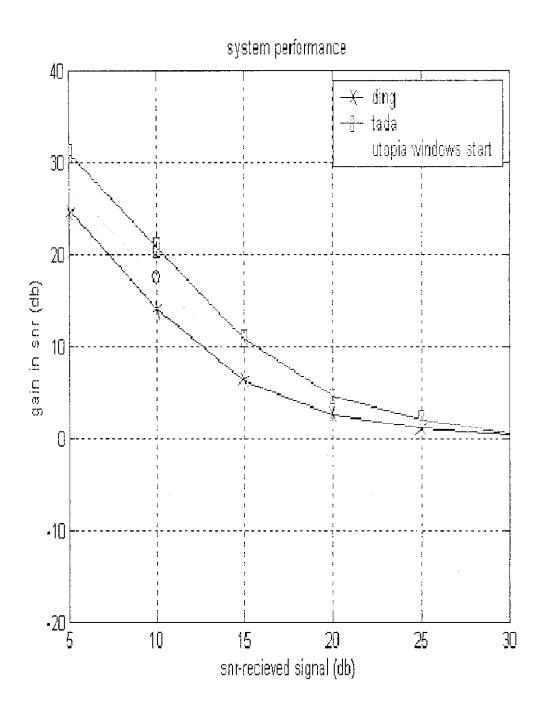

To evaluate the proposed implementation, the results were compared with the results of implementations. The ANC systems in these researches have no secondary path, where, our ANC system has secondary path modelling filter.

The digital signal processors uses a programmable, 16-bit, fixed-point format with the clock frequency of 40MHz. The computational time needed to execute an iteration of the ANC system on this DSP processor is about 78.1 usec. The acceptable convergence, 350 iterations is needed, leads to a total convergence time of about 27.3ms (=350\*78.1 us).

The proposed FPGA implementation of the modular ANC system in this paper uses a 32-bit fixed pointformat. The adaptive control filter and the adaptive modeling filter have 32 tap eights. The clock frequency that obtained for this FPGA implementation is 120 MHz. The system needs 66.7 ns to execute an iteration. The design needs 190 iterations for an acceptable convergence. This results lead to a total convergence time of about 12.67us (= 190\*65.7ns).

Figure 6.1 Noise Signals

Figure 6.2 System Performance

## CHAPTER 7 RESULTS AND DISCUSSION

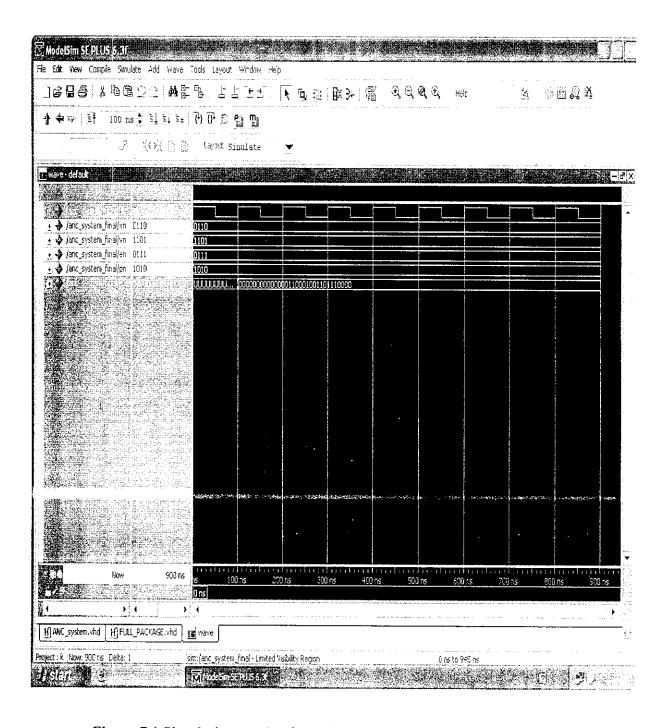

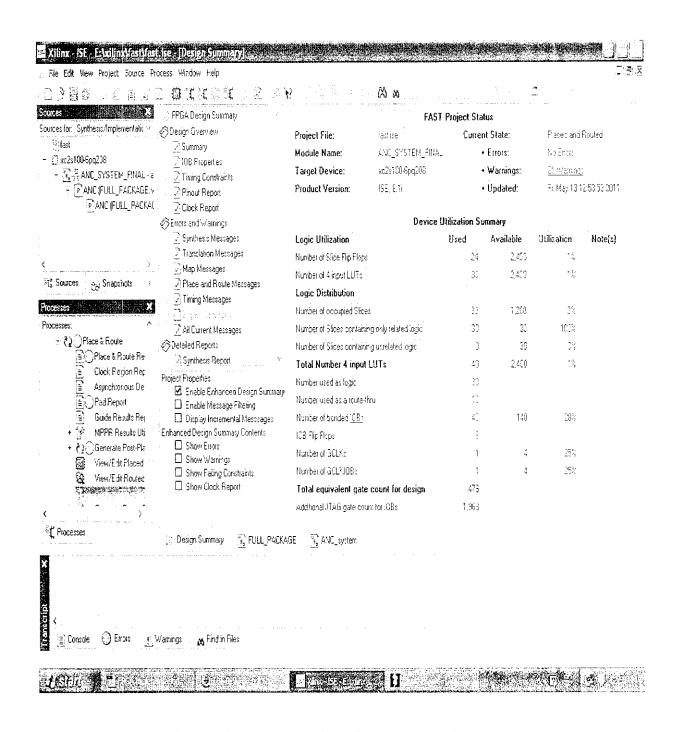

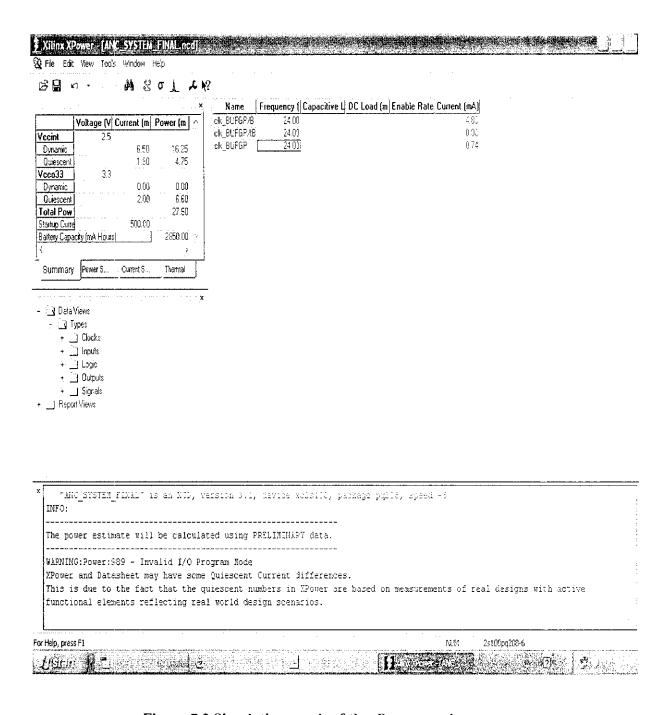

The simulation of this project has been done using MODELSIM XE111 6.2g and XILINX ISE 9.2i.

Modelsim is a simulation tool for programming {VLSI} {ASIC}s, {FPGA}s, {CPLD}s, and {SoC}s. Modelsim provides a comprehensive simulation and debug environment for complex ASIC and FPGA designs. Support is provided for multiple languages including Verilog, SystemVerilog, VHDL and SystemC.

Xilinx was founded in 1984 by two semiconductor engineers, Ross Freeman and Bernard Vonderschmitt, who were both working for integrated circuit and solid-state device manufacturer Zilog Corp. The Virtex-II Pro, Virtex-4, Virtex-5, and Virtex-6 FPGA families are particularly focused on system-on-chip (SOC) designers because they include up to two embedded IBM PowerPC cores The ISE Design Suite is the central electronic design automation (EDA) product family sold by Xilinx. The ISE Design Suite features include design entry and synthesis supporting Verilog or VHDL, place-and-route (PAR), completed verification and debug using Chip Scope Pro tools, and creation of the bit files that are used to configure the chip.

The simulation results showing the FPGA implementation of modula: active noise control system are attached here.

Figure 7.1 Simulation result of the Output Waveform

Figure 7.2 Simulation result showing Gate count used

Figure 7.3 Simulation result of the Power used

## **CONCLUSION**

In this project a hardware implementation of the modular ANC system with online secondary path modeling was presented. This ANC system contains four similar modules to reduce the unwanted primary noise. Each module consists of two shift registers, a convolution unit, an adaptive filter controller, an adder, and a two's complementer. One of these modules per forms as the main adaptive control filter that uses an FxLMS algorithm to converge the tap-weights. Two modules work as the adaptive modeling filters, used LMS algorithm to model the secondary path filter. The last module works as a digital filter to produce the anti-noise output signal.

The ANC system was implemented on the Altera FPGA. The current FPGA implementation of the ANC system uses a 32- bit fixed point format. The adaptive control filter and the adaptive modeling filter have 32 tapweights. The clock frequency that obtained for this FPGA implementation is 120 MHz. The system needs 66.7 ns to execute an iteration. The proposed design needs 190 iterations for an acceptable convergence. This results lead to a total convergence time of about 12.67us (=190\*66.7ns).

### **BIBLIOGRAPHY**

- [1] F. Nagi, J. Low, S. Li, "Active Noise Cancellation with TMS320C5402 DSP Starter Kit," *IEEE Signal processing*, 2004.

- [2] A. D. Stefano, A. Scaglione, C. Giaconia, "Efficient FPGA Implementation of an Adaptive Noise Canceller," in *Proc. IEEE 2005, CAMP'05*, vol. 00, 2005, pp. 87-89.

- [3] A. Jalali, Sh. Gholami Borouj and M. Eshghi, "Design and Implementation of a Fast Active Noise Control System on FPGA," in *Proc. IEEE MED* '07. Athens, Greece, 2007.

- [4] M. Eshghi, Sh. Gholami Boroujeny and A. Jalali, "A Hardware Design for an Online Active Noise Control System," *IEEE MED '07 Conference*, Athens, Greece, 2007.

- [5] M. T. Akhtar, M. Abe, and M. Kawamata, "A New Structure for Feedforward Active Noise Control Systems With Improved Online Secondary Path Modeling," IEEE Trans. Speech Audio Process., vol. 13, 2003, pp. 155-158.

- [6] M. Zhang, H. Lan. and W. Ser, "Cross-updated active noise control system with online secondary path modeling," *IEEE Trans.Speech Audio Process.*, vol. 9, pp. 598–602, July 2001.

- [7] A. Carini, S. Malatini and G. Sicuranza, "Optimal Variable Step-Size NLMS Algorithms for Feedforward Active Noise Control," In *Proc EUSIPCO 2008*, Lausanne Switzerland, August 25-29, 2008.

- [8] Sh. Gholami Boroujeny, M. Eshghi, "A Modular Design for an Active Noise Control System," *IEEE TENCON Conference*, Hyderabad, India, November 2008.

- [9] A. Elhossini, S. Areibi and R. Dony, "An FPGA Implementation of the LMS Adaptive Filter for Audio Processing," in *Proc. IEEE International Conference on Reconfigurable Computing and FPGAs*, Sept. 2006,