# IMPROVED DESIGN OF HIGH-PERFORMANCE

# PARALLEL DECIMAL MULTIPLIERS

By

MANEESHA.V.P Reg. No. 1020106012 of

KUMARAGURU COLLEGE OF TECHNOLOGY

(An Autonomous Institution affiliated to Anna University, Coimbatore) COIMBATORE - 641049

A PROJECT REPORT

Submitted to the FACULTY OF ELECTRONICS AND COMMUNICATION ENGINEERING

> In partial fulfillment of the requirements for the award of the degree of MASTER OF ENGINEERING IN APPLIED ELECTRONICS APRIL 2012

> > i

## BONAFIDE CERTIFICATE

Certified that, this project report entitled "DESIGN OF HIGH-PERFOMANCE PARALLEL DECIMAL MULTIPLIERS" is the bonafide work of Mrs.Maneesha.V.P [Reg. no. 1020106012] who carried out the project under my supervision. Certified further, that to the best of my knowledge the work reported herein does not form part of any other project or dissertation on the basis of which a degree or award was conferred on an earlier occasion on this or any other candidate.

Project Guide Prof.K.Ramprakash Head of the Department Dr. Ms. Rajeswari Mariappan

The candidate with university Register no. 1020106012 is examined by us in the project viva-voce examination held on .....

ii

Internal Examiner

External Examiner

# ACKNOWLEDGEMENT

I express my profound gratitude to our director **J.Shanmugham.** for giving this opportunity to pursue this course

At this pleasing moment of having successfully completed the project work, I wish to acknowledge my sincere gratitude and heartfelt thanks to our beloved Principal **Prof.Ramachandran**, for having given me the adequate support and opportunity for completing this project work successfully.

I extend my heartfelt thanks to my internal guide **Prof.K.Ramprakash**, for his ideas and suggestion, which have been very helpful for the completion of this project work. His careful supervision has ensured me in the attaining perfection of work.

I express my sincere thanks to **Dr.Rajeswari Mariyappan Ph.D.**, the ever active, Head of the Department of Electronics and Communication Engineering, who rendering us all the time by helps throughout this project

In particular, I wish to thank and everlasting gratitude to the project coordinator Asst.Prof.R.Hemlatha, Department of Electronics and Communication Engineering for her expert counseling and guidance to make this project to a great deal of success.

Last, but not the least, I would like to express my gratitude to my family members, friends and to all my staff members of Electronics and Communication Engineering department for their encouragement and support throughout the course of this project. ABSTRACT

The new generation of high-performance decimal floating-point units demands efficient implementations of parallel decimal multipliers. In this paper we discuss about the implementation of the decimal parallel multipliers used in the decimal floating-point units. Here we discuss two architectures using SD radix-5 and SD radix-10 encoding of the multiplier with which the partial products are generated and a multioperand carry save algorithm is used for the reduction of the partial products. The proposed method allows the reuse of the binary CSA for computing the sum of BCD operands. Corrections required for decimal operands are done in parallel, separately from the calculation of the binary sum such that the layout of the binary carry save adder is not rearranged. 16 digit adders while implemented using the proposed architectures gives excellent are area-delay values when compared with the conventional binary multipliers.

| CHAPTER | TITLE                                     | PAGE |

|---------|-------------------------------------------|------|

| NO      |                                           | NO   |

|         | ABSTRACT                                  | iv   |

|         | LIST OF FIGURES                           | viii |

|         | LIST OF TABLES                            | х    |

|         | LIST OF ABBREVIATIONS                     | xi   |

| 1       | INTRODUCTION                              | 1    |

|         | 1.1 Project Goal                          | 1    |

|         | 1.2 Overview                              | 2    |

|         | 1.3 Software's Used                       | 3    |

|         | 1.4 Organization of the Chapter           | 3    |

| 2       | FIXED POINT DECIMAL MULTIPLICATION        | 4    |

|         | 2.1 An Overview of Decimal Multiplication | 4    |

|         | 2.2 Existing Methods                      | 5    |

| 3       | DECIMAL FIXED POINT ARCHITECTURES         | 8    |

|         | 3.1 Signed Digit Radix-10 Architecture    | 8    |

|         | 3.2 Signed Digit Radix-5 Architecture     | 9    |

| 4       | DECIMAL PARTIAL PRODUCT GENERATION        | 11   |

|         | 4.1 SD Radix-10 Recoding                  | 11   |

|         | 4.2 SD Radix-5 Recoding                   | 14   |

|         | 4.3 Generation of Multiplicand Multiples  | 16   |

|         | 4.4 Implementation of Digit Recoders      | 18   |

| 5       | PARIAL PRODUCT REDUCTION                  | 20   |

|         | v                                         |      |

|   | 5.1 Partial Product Arrays                           | 20 |

|---|------------------------------------------------------|----|

|   | 5.2 Method for Decimal Carry-Save Addition           | 22 |

|   | 5.3 Alternative Decimal Digit Encodings              | 24 |

|   | 5.4 Algorithm                                        | 25 |

|   | 5.5 Decimal 3:2 and 4:2 CSAs                         | 26 |

|   | 5.5.1 4:2 Compressors                                | 27 |

|   | 5.5.2 Gate level implementation                      | 28 |

|   | 5.5.3 Implementation of digit recoders               | 31 |

| 6 | PROPOSED ARCHITECTURE- COMBINED                      | 35 |

|   | DECIMAL/BINARY CARRY SAVE ADDER                      |    |

|   | 6.1 Algorithm                                        | 35 |

|   | 6.2 Implementation of combined decimal/binary carry- | 39 |

|   | save adder                                           |    |

| 7 | HIGH-PERFORMANCE RADIX-4 MULTIPLIER                  | 41 |

|   | USING THE PASS TRANSISTOR LOGIC                      |    |

|   | 7.1 Adder Architecture Using The CPL Technique       | 41 |

|   | 7.2 Architecture of Radix-4 Multiplier               | 43 |

| 8 | EVALUATION RESULTS                                   | 46 |

|   | 8.1 Simulation Results                               | 48 |

|   | 8.1.1 SD Radix-10 Architecture                       | 48 |

|   | 8.1.2 SD Radix-5 Architecture                        | 49 |

|   | 8.1.3 SD Radix-10 Architecture using Combined        | 50 |

|   | Decimal/Binary CSA                                   |    |

|   | 8.1.4 SD Radix-10 Architecture using Combined        | 51 |

|   | Decimal/Binary CSA                                   |    |

|   | 8.1.5 Radix-4 Binary Multiplier                      | 52 |

|   | 8.2 Synthesis Results                                | 53 |

|   | 8.2.1 Power Report                                   | 53 |

|   | vi                                                   |    |

| 8.2.1.1 SD Radix-10 Architecture       | 53 |  |

|----------------------------------------|----|--|

| 8.2.1.2 SD Radix-5 Architecture        | 53 |  |

| 8.2.1.3 SD Radix-10 Architecture using | 54 |  |

| Combined Decimal/Binary CSA            |    |  |

| 8.2.1.4 SD Radix-10 Architecture using | 54 |  |

| Combined Decimal/Binary CSA            |    |  |

| 8.2.1.5 Radix-4 Binary Multiplier      | 55 |  |

| 8.2.2 Xilinx Synthesis Report          | 55 |  |

| 8.2.2.1 SD Radix-10 Architecture       | 55 |  |

| 8.2.2.2 SD Radix-5 Architecture        | 56 |  |

| 8.2.2.3 SD Radix-10 Architecture using | 57 |  |

| Combined Decimal/Binary CSA            |    |  |

| 8.2.2.4 SD Radix-10 Architecture using | 58 |  |

| Combined Decimal/Binary CSA            |    |  |

| 8.2.2.5 Radix-4 Binary Multiplier      | 59 |  |

| 8.3 Comparison                         | 60 |  |

| CONCLUSION & FUTURE WORK               | 63 |  |

| REFERENCES                             | 64 |  |

|                                        |    |  |

| FIGURE | CAPTION                                                            |       |  |  |  |

|--------|--------------------------------------------------------------------|-------|--|--|--|

| 110    |                                                                    | NO    |  |  |  |

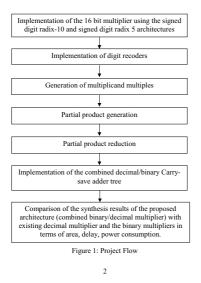

| 1      | Project Flow                                                       | 2     |  |  |  |

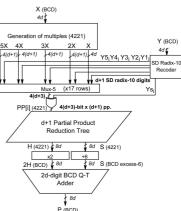

| 2      | Combinational SD radix-10 architecture.                            | 9     |  |  |  |

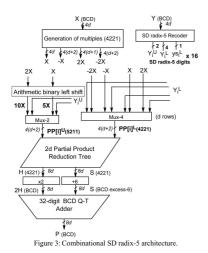

| 3      | Combinational SD radix-5 architecture                              | 10    |  |  |  |

| 4      | Partial product generation for SD radix-10                         | 11    |  |  |  |

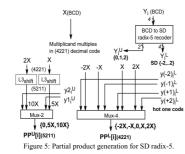

| 5      | Partial product generation for SD radix-5                          | 14    |  |  |  |

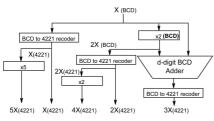

| 6      | Generation of multiplicand multiples for SD radix-10               | 16    |  |  |  |

| 7      | Calculation of ×5 for decimal operands coded in (4221)             | 17    |  |  |  |

| 8      | Generation of multiplicand multiples for SD radix-5                | 18    |  |  |  |

| 9      | Partial product arrays generated for 16-digit operands in the      | 21    |  |  |  |

|        | case of SD Radix-10 architecture                                   |       |  |  |  |

| 10     | Partial product arrays generated for 16-digit operands in the      | 22    |  |  |  |

|        | case of SD Radix-5 architecture                                    |       |  |  |  |

| 11     | BCD carry-save addition using a 4-bit 3:2 CSA                      | 24    |  |  |  |

| 12     | Calculation of $\times 2$ for decimal operands coded in (4221) and | 26    |  |  |  |

|        | (5211)                                                             |       |  |  |  |

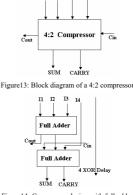

| 13     | Block diagram of a 4:2 compressor                                  | 27    |  |  |  |

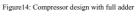

| 14     | Compressor design with full adder                                  | 27    |  |  |  |

| 15     | Alternative Implementation of 4:2 Compressor with 3 XOR            | 28    |  |  |  |

|        | Delay                                                              |       |  |  |  |

| 16     | Proposed decimal digit (4-bit) 3:2 CSAs                            | 28-29 |  |  |  |

| 17     | Proposed decimal (1-digit slice) 4:2 CSAs                          | 31    |  |  |  |

| 18     | Gate level implementation of the (4221) to (5211) digit            | 33    |  |  |  |

|        | recoders                                                           |       |  |  |  |

| 19     | Implementation of a (5211) to (4221) digit recoder                 | 34    |  |  |  |

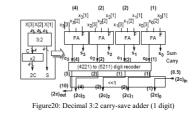

| 20     | Decimal 3:2 carry-save adder (1 digit)                             | 35    |  |  |  |

|        |                                                                    |       |  |  |  |

LIST OF FIGURES

9

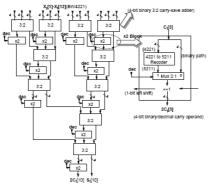

| 21 | Combined multi-operand adder tree: (1 digit/4-bit column) | 36 |

|----|-----------------------------------------------------------|----|

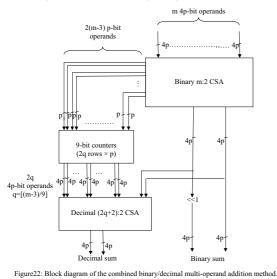

|    | Block diagram of the combined binary/decimal multi-       | 38 |

| 22 | operand addition method                                   |    |

| 23 | Multi-operand adder tree                                  | 40 |

| 24 | Full adder circuit                                        | 42 |

| 25 | $4 \times 4$ bit radix-4 multiplier circuit               | 43 |

| 26 | Generation of multiples in a radix-4 multiplier           | 44 |

| 27 | Conceptual Overview of Modelsim                           | 46 |

| 28 | Simulation result of SD Radix-10 architecture             | 48 |

| 29 | Simulation result of SD Radix-5 architecture              | 49 |

| 30 | Simulation result of SD Radix-10 architecture using       | 50 |

|    | combined decimal/binary CSA                               |    |

| 31 | Simulation result of SD Radix-5 architecture using        | 51 |

|    | combined decimal/binary CSA                               |    |

| 32 | Simulation result of radix-4 binary multiplier            | 52 |

| 33 | Power report of SD Radix-10 architecture                  | 53 |

| 34 | Power report of SD Radix-5 architecture                   | 53 |

| 35 | Power report of SD Radix-10 architecture using combined   | 54 |

|    | decimal/binary CSA                                        |    |

| 36 | Power report of SD Radix-5 architecture using combined    | 54 |

|    | decimal/binary CSA                                        |    |

| 37 | Power report of radix-4 binary multiplier                 | 55 |

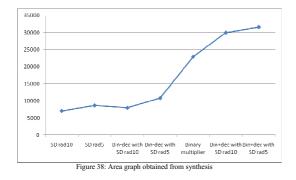

| 38 | Area graph obtained from synthesis                        | 62 |

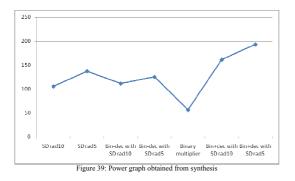

| 39 | Power graph obtained from synthesis                       | 62 |

|    |                                                           |    |

# LIST OF TABLES

| TABLE<br>NO | CAPTION                                        | PAGE<br>NO |

|-------------|------------------------------------------------|------------|

| 1           | Decimal Codings                                | 5          |

| 2           | SD radix-10 selection signals                  | 12         |

| 3           | SD radix-5 selection signals                   | 15         |

| 4           | Selected Decimal Codes for the Recoded Digits  | 19         |

| 5           | Selected decimal codes for the recoded digits  | 32         |

| 6           | Comparison of various multiplier architectures | 61         |

ix

# LIST OF ABBREVIATIONS

| DFP  | <br>Digital Floating Point                      |

|------|-------------------------------------------------|

| SD   | <br>Signed Digit                                |

| BCD  | <br>Binary Coded Decimal                        |

| CSA  | <br>Carry Save Adder                            |

| CLA  | <br>Carry Look-ahead Adder                      |

| CPL  | <br>Complementary Pass-transistor Logic         |

| NMOS | <br>N-type Metal Oxide Semiconductor            |

| PMOS | <br>P-type Metal Oxide Semiconductor            |

| MCIT | <br>Multiplexing Control Input Technique        |

| VLSI | <br>Very Large Scale Integration                |

| FPGA | <br>Field Programmable Gate Array               |

| ASIC | <br>Application Specific Integrated Circuits    |

| CPLD | <br>Complex Programmable Logic Device           |

| SoC  | <br>System-On-Chip                              |

| VHDL | <br>Very High Speed Integrated Circuit Hardware |

|      | Description Language                            |

# CHAPTER 1

х

## INTRODUCTION

The microprocessor manufacturers include decimal floating–point units in their products, oriented to mainframe servers, to satisfy the high performance demands of current financial, commercial and user–oriented applications. Providing hardware support for decimal floating-point (DFP) arithmetic is becoming a topic of interest. Although software DFP implementations satisfy the precision requirements, they are about an order of magnitude slower than hardware implementations and could not satisfy the highperformance demands. Specifically, the revision of the IEEE 754 Standard for Floating-Point Arithmetic (IEEE 754-2008) incorporates specifications for DFP arithmetic that can be implemented in software, hardware, or in a combination of both. An important and frequent operation in decimal computations is multiplication. However, due to the inherent in-efficiency of decimal arithmetic implementations in binary logic, practically most of the proposed decimal multipliers are used extensively in most of the binary floating–point units and are of interest for decimal applications to scale performance.

## 1.1 PROJECT GOAL

An important and frequent operation in decimal computations is multiplication. However, decimal multiplication is more difficult to implement due to the complexity in the generation of multiplicand multiples and the inefficiency of representing decimal values in systems based on binary signals. These issues complicate the generation and reduction of partial products. Thus, while decimal adders are implemented in a parallel fashion and are almost as efficient as binary ones, commercial implementations of decimal multipliers are sequential. The goal of this project is to introduce two novel architectures which are fully combinational for fixed point parallel decimal multipliers. We also describe new techniques for partial product generation and reduction that can be implemented in combined binary/decimal floating point units so as to reduce the latency and the hardware complexity of the previous designs

## 1.2 OVERVIEW

In this project, we describe the architectures of two parallel decimal multipliers. The parallel generation of partial products is performed using signed-digit radix-10 or radix-5 recodings of the multiplier and a simplified set of multiplicand multiples. The reduction of partial products is implemented in a tree structure based on a combined decimal/binary multioperand carry-save addition algorithm that uses unconventional (non BCD) decimal-coded number systems. The synthesis results of the 16 bit operands of the proposed architecture (combined binary/decimal multiplier) will be compared with existing decimal multiplier architectures (SD radix-10 and SD radix-5) and the binary multipliers in terms of area, delay, power consumption.

# 1.3 SOFTWARE USED

- ➤ ModelSim XE 111 6.2g

- Xilinx ISE 9.2i

## 1.4 ORGANIZATION OF THE REPORT

- > Chapter 2 discusses about fixed point decimal multiplication

- Chapter 3 briefs about fixed point decimal architectures.

- Chapter 4 explains about partial product generation.

- > Chapter 5 discusses about partial product reduction.

- Chapter 6 describes in detail about the proposed architecture.

- Chapter 7 mentions about the radix-4 binary multiplier

- Chapter 8 shows the evaluation results.

- > Chapter 9 provides the conclusion and future scope.

# CHAPTER 2

## FIXED-POINT DECIMAL MULTIPLICATION

Multiplication consists of three stages: generation of partial products, fast reduction (addition) of partial products to a two operand and a final carry propagate addition. Decimal multiplication is more complex than binary multiplication mainly for two reasons: the higher range of decimal digits ([0, 9]), which increments the number of multiplicand multiples and the inefficiency of representing decimal values in systems based on binary logic using BCD–8421 (since only 9 out of the 16 possible 4–bit combinations represent a valid decimal digit). These issues complicate the generation and reduction of partial products

# 2.1 AN OVERVIEW OF DECIMAL MULTIPLICATION

A digit  $Z_i$  of a decimal integer operand  $\mathbf{Z} = \sum_{i=0}^{d-1} Z_i \ 10^i$  is coded as a positive weighted 4-bit vector as

# $Z_i = \sum_{i=1}^{n} z_{i,j}r_j$

(1)

Where,  $Zi \in [0,9]$  is the i<sup>th</sup> decimal digit and  $z_{i,j}$  is the j<sup>th</sup> bit of the i<sup>th</sup> digit, and  $r_j \ge 1$ 1 is the weight of the j<sup>th</sup> bit. The previous expression represents a set of coded decimal number systems that includes BCD (with  $r_j = 2^j$ ), shown in Table 1. The other decimal codes shown in Table 1 are also used for representing different decimal operands as required by the methods used in the project. These codes are represented by their weight bits as  $(r_3r_2r_1r_0)$ . The 4-bit vector that represents the decimal digit  $Z_i$  in a decimal code  $(r_3r_2r_1r_0)$  is denoted by  $Z_i(r_3r_2r_1r_0)$ .

The multiplicand  $X = \sum_{i=1}^{d-1} X_i |0^i|$  and multiplier  $Y = \sum_{i=1}^{d-1} Y_i |0^i|$  are unsigned decimal integer d-digit BCD words. Fixed-point multiplication (both binary and decimal) consists of three stages

- · generation of partial products

- reduction (addition) of partial products to two operands

- final conversion (usually a carry propagate addition) to a nonredundant 2d-digit BCD representation  $P = \sum_{i=0}^{M_{cons}} \frac{2}{i} P_{i} 10^{i}$ .

## Table 1: Decimal Codings

3

| Zi | Z <sub>i</sub> (BCD) | Z <sub>i</sub> (5421) | Z <sub>i</sub> (4221) | Z <sub>i</sub> (5211) | Z <sub>i</sub> (4311) | Z <sub>i</sub> (3321) |

|----|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0  | 0000                 | 0000                  | 0000                  | 0000                  | 0000                  | 0000                  |

| 1  | 0001                 | 0001                  | 0001                  | 0001 0010             | 0001 0010             | 0001                  |

| 2  | 0010                 | 0001                  | 0100 0010             | 0100 0011             | 0011                  | 0010                  |

| 3  | 0011                 | 0011                  | 0101 0011             | 0101 0110             | 0100                  | 0100 1000 0011        |

| 4  | 0100                 | 0100                  | 0110 1000             | 0111                  | 1000 0110 0101        | 1001 0101             |

| 5  | 0101                 | 1000                  | 0111 1001             | 1000                  | 1001 0111 1010        | 1010 0110             |

| 6  | 0110                 | 1001                  | 1010 1100             | 1010 1001             | 1011                  | 1100 1011 0111        |

| 7  | 0111                 | 1010                  | 1011 1101             | 1011 1100             | 1100                  | 1101                  |

| 8  | 1000                 | 1011                  | 1110 1101             | 1110 1101             | 1110 1101             | 1110                  |

| 9  | 1001                 | 1100                  | 1111                  | 1111                  | 1111                  | 1111                  |

Extension to decimal floating-point multiplication involves exponent addition, rounding of  $P=X\times Y$  to fit the required precision, sign calculations and exception detection and handling.

In Table 1 diverse BCD codings are represented. For BCD–8421,  $r_j = 2^j$ . BCD– 4221 and BCD–5211 are the coding schemes characterized by the use of redundancy in decimal digit representation. As we have mentioned, the use of BCD–8421 to represent decimal digits means introducing costly decimal corrections in the partial product reduction binary CSA tree to obtain the correct decimal carry and sum. To avoid these corrections we use the BCD–4221 coding of Table 1 to represent partial product digits which will be later discussed in detail.

#### 2.2 EXISITING METHODS

Proposed methods for the generation of decimal partial products follow mainly two approaches. The first alternative performs a digit by digit multiplication of the input operands, using digit by digit lookup table methods .In this magnitude range reduction of the operand digits by a signed-digit radix-10 recoding (from [0, 9] to [-5,5]) is suggested. This recoding of both operands speeds up and simplifies the generation of partial products. Then, signed-digit partial products are generated using simplified tables and combinational logic. This class of methods is only suited for serial implementations, since the high hardware demands make them impractical for parallel partial product

generation. The second approach generates and stores all the required multiplicand multiples. Next, multiples are distributed to the reduction stage through multiplexers controlled by the BCD multiplier digits ([0; 9]). This approach requires several wide decimal carry-propagate additions to generate some complex BCD multiplicand multiples {3X,6X,7X,8X,9X}. Usually only even multiples {2X; 4X; 6X; 8X} are computed and stored. Odd multiples {3X: 5X: 7X: 9X} are obtained on demand. A reduced set of BCD multiples {X; 2X; 4X; 5X} is pre-computed without a carry propagation. All the multiples can be obtained from the sum of two elements of this set. The other alternative is that 2X and 5X multiples can be computed in few levels of combinational logic. Negative multiples require an additional 10's complement operation

Decimal carry-save addition methods use two BCD words to represent sum and carry or a BCD sum word and a carry bit per digit. The first group implements decimal addition mixing binary CSAs with combinational logic for decimal correction. A scheme of two levels of 3:2 binary CSAs is used to add the partial products iteratively. Since it uses BCD to represent decimal digits, a digit addition of +6 or +12 (modulo 16) is required to obtain the decimal carries and to correct the sum digit. In order to reduce the contribution of the decimal corrections to the critical path, three different techniques for multioperand decimal carry-save addition were proposed. Two of them perform BCD corrections (+6 digit additions) using combinational logic and an array of binary carrysave adders (speculative adders), although a final correction is also required. A sequential decimal multiplier based on these techniques uses BCD invalid combinations (overloaded BCD representation) to simplify the sum digit logic. The other approach basically a nonspeculative adder uses a binary CSA tree followed by a single decimal correction. Among these proposals, the non-speculative adders present the best area-delay figures and are suited for tree topologies. Another recent proposal uses a binary carry-free tree adder and a subsequent binary to BCD conversion to add up to N d-digit BCD operands.

The second group of methods uses different topologies of 4-bit radix-10 carrypropagate adders to implement decimal carry-save addition. A serial multiplier can be implemented using an array of radix-10 carry look-ahead adders (CLAs). A CSA tree using these radix-10 CLAs is implemented in the using combinational decimal parallel

6

# CHAPTER 3 DECIMAL FIXED- POINT ARCHITECTURES

In this chapter we present a general overview of the architectures for d-digit (4dbit) BCD decimal fixed-point parallel multiplication. These designs are based on the techniques for partial product generation and reduction as mentioned earlier. The main feature of these architectures is the use of codes (4221) and (5211), instead of BCD, to represent the partial products. This improves the reduction of decimal partial products with respect to other proposals, in terms of both area and latency.

# 3.1 Signed Digit Radix-10 Architecture

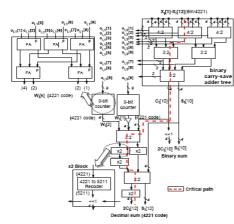

The architecture of the d-digit SD radix-10 multiplier is shown in Fig. 2. The multiplier consists of the following stages: generation of decimal partial products coded in (4221) (generation of multiplicand multiples and SD radix-10 encoding of the multiplier), reduction of partial products, and a final BCD carry-propagate addition.

The generation of the d + l partial products is performed by an encoding of the multiplier into d SD radix-10 digits and an additional leading bit. Each SD radix-10 digit controls a level of 5:1 muxes, which selects a positive multiplicand multiple {0;X; 2X; 3X; 4X; 5X} coded in (4221). The generation of these multiples is detailed in Section 4.3. To obtain each partial product, a level of XOR gates inverts the output bits of the 5:1 muxes when the sign of the corresponding SD radix-10 digit is negative.

Before being reduced, the d+1 partial product, coded in (4221), are aligned according to their decimal weights. Each p-digit column of the partial product array is reduced to two (4221) decimal digits using one of the decimal digit p:2 CSA trees described in chapter 5. The number of digits to be reduced for each column varies from p d+1 to p = 2. Thus, the d+1 partial products are reduced to two 2d digit operands S and H coded in (4221).

The final product is a 2d-digit BCD word given by P = 2H + S. Before being added, S and H need to be processed. S is recoded from (4221) to BCD excess-6 (BCD value plus 6, which requires practically the same logical complexity as a recoding to

multiplier and to optimize the partial product reduction, they also use an array of decimal digit counters

The reduction of all decimal partial products in parallel requires the use of efficient multioperand decimal tree adders. Among the different schemes, the most promising ones for fast parallel addition seem to be those using binary CSA trees or some parallel network of full adders due to their faster and simpler logic cells (full adders against SD adder cells or radix-10 CLAs). These methods assume that decimal digits are coded in BCD. However, BCD is highly inefficient for implementing decimal carry save addition using binary arithmetic because of the need to correct the invalid 4-bit combinations (those not representing a decimal digit). The previous methods use different schemes to perform these BCD corrections. Moreover, the BCD carry digit must be multiplied by 2, which requires additional logic. We also implement multioperand decimal tree adders using a binary CSA tree, but with operands coded in decimal codings that are more efficient than BCD, namely (4221) or (5211). These multioperand decimal CSA trees are detailed in later chapters.

7

Ge ration of multiples (4221) Y (BCD) 4d 🕻 Y5;Y4; Y3; Y2;Y1; SD Radix-1 + d+ SD radix-10 dig 4(d+3) 1 PP[i] (4221) 4(d+3)-bit x (d+1) pp d+1 Partial Product duction Tree (4221) 🕻 80 🛔 8d S (4221) ור <u>+6</u> ∦ 8d (BCD) \$ 8d S (BCD exc 2H ligit BCD Q-T 2d-Ł 80 ь/ BCD)

Figure 2: Combinational SD radix-10 architecture.

BCD). The H  $\times$  2 multiplication is performed in parallel with the recoding of S. This  $\times 2$ block uses a (4221) to (5421) digit recoder and a 1-bit wired left shift to obtain the operand 2H coded in BCD.

For the final BCD carry-propagate addition, we use a quaternary tree (Q-T) adder based on conditional speculative decimal addition. It has low latency (about 10 percent more than the fastest binary adders) and requires less hardware than other alternatives.

#### 3.2 Signed Digit Radix-5 Architecture

The dataflow of the d-digit SD radix-5 architecture is shown in Fig. 3. The multiplier consists of the following stages: generation of decimal partial products (generation of multiplicand multiples and SD radix-5 encoding of the multiplier),

reduction of partial products, and a final BCD carry-propagate addition. SD radix-5 recoding, described in Section 4.2, generates 2d decimal partial products, half coded in (4221) and the other half in (5211). This improved scheme only requires the generation of simple multiplicand multiples {-2X;-X;X; 2X} coded in (4221), as shown in Section 4.2. The reduction of the aligned partial products is carried out using the mixed (4221/5211) decimal digit *p*:2 CSA trees ( $2 \le p \le 2d$ ) described in chapter 5. As in the SD radix-10 architecture, the 2d-digit operands S and H are processed before being assimilated in the 2d-digit BCD carry-propagate adder.

Fig. 4 shows the block diagram of the generation of one partial product using the SD radix-10 recoding. This recoding transforms a BCD digit  $Y_i \in \{0, \ldots, 9\}$  into an SD radix-10  $Yb_i \in \{-5, \ldots, 5\}$ . The value of the recoded digit  $Yb_i$  depends on the decimal value of  $Y_i$  and on a signal  $ys_{i-1}$  (sign signal) that indicates if  $Y_{i-1}$  is greater than or equal to 5. Thus, the *d*-digit BCD multiplier Y is recoded into the *d*+*l*- digit SD radix-10 multiplier  $Yb \equiv \sum_{i=0}^{d} Yb_i \, 10^i$  with  $Yb_d = ys_{d+0} \in \{0, 1\}$ .

Table 2: SD radix-10 selection signals.

| Dec    | BCD              | $Y_{i\text{-}1}\!\geq\!5$ | SD radix-10 digit | Hot one code signals            |

|--------|------------------|---------------------------|-------------------|---------------------------------|

| Value  | $\mathbf{Y}_{i}$ | $ys_{i-1}$                | $Yb_i$            | $ys_i y5_i y4_i y3_i y2_i y1_i$ |

| 0      | 0000             | 0                         | 0                 | 000000                          |

| 0 0000 |                  | 1                         | 1                 | 000001                          |

| 1      | 0001             | 0                         | 1                 | 000001                          |

| 1      | 0001             | 1                         | 2                 | 000010                          |

| 2      | 0010             | 0                         | 2                 | 000010                          |

| 2      | 0010             | 1                         | 3                 | 000100                          |

| 2      | 0011             | 0                         | 3                 | 000100                          |

| 3      | 0011             | 1                         | 4                 | 001000                          |

|        | 0100             | 0                         | 4                 | 001000                          |

| 4      | 0100             | 1                         | 5                 | 010000                          |

| ~      | 0101             | 0                         | -5                | 110000                          |

| 5      | 0101             | 1                         | -4                | 101000                          |

|        | 0110             | 0                         | -4                | 101000                          |

| 6      | 0110             | 1                         | -3                | 100100                          |

| 7      | 0111             | 0                         | -3                | 100100                          |

| 7      | 0111             | 1                         | -2                | 100010                          |

| 0      | 1000             | 0                         | -2                | 100010                          |

| 8      | 1000             | 1                         | -1                | 100001                          |

| 9      | 1001             | 0                         | -1                | 100001                          |

| 9      | 1001             | 1                         | 0                 | 100000                          |

# CHAPTER 4 DECIMAL PARTIAL PRODUCT GENERATION

For simplified multiplication we aim for parallel generation of a reduced number of partial products coded in (4221) or (5211). This is achieved with the recoding of the d- digit BCD multiplier and the generation of a reduced and simple set of multiplicand multiples. We present two different schemes with good trade-offs between fast generation of partial products and the number of partial products generated. A minimally redundant SD radix-10 recoding of the multiplier (with digits in  $\{-5; \ldots; 0; \ldots; 5\}$ ) produces only d+1 partial products but requires a carry-propagate addition to generate complex multiples 3X and -3X. A second scheme, named SD radix-5 recoding, encodes each BCD digit  $Y_i$  of the multiplier into two digits  $Y_i^U \in \{0; 1; 2\}; \quad Y_i^L \in \{-2; -1; 0; 1; 2\}$  such that  $Y_i = Y_i^U \cdot 5 + Y_i^{\Sigma}$ . It generates 2d partial products (2 digits per radix-10 digit), but all multiplicand multiples are produced in a few levels of combinational logic. Furthermore, the (4221) and (5211) codes are self-complementing. Thus, an advantage with respect to previous schemes, which use BCD multiples, is that the 9's complement of each digit can be obtained by inverting its bits. This simplifies the generation of the negative multiplicand multiples from the positive ones. In addition, the previous methods based on the decomposition  $Y_i = Y_i^{U} \cdot 5 + Y_i^{L}$  require combinational logic to generate the 5X multiple. We use mixed (4221/5211) decimal codings to remove this logic.

# 4.1 SD Radix-10 Recoding

Figure 4: Partial product generation for SD radix-10.

11

Each digit Yb<sub>i</sub> generates a partial product PP[i] selecting the proper multiplicand multiple coded in (4221). This is performed in a similar way to a modified Booth recoding: Y bi is represented as five "hot one code" signals {y1<sub>i</sub>; y2<sub>i</sub>; y3<sub>i</sub>; y4<sub>i</sub>; y5<sub>i</sub>} and a sign bit ys<sub>i</sub>. "Hot one code" refers to a group of bits among which the legal combinations of values are only those with a single high (1) bit and all the others low (0). These signals are obtained directly from the BCD multiplier digits Y<sub>i</sub> using the following logical expressions:

$$\begin{split} y_{5i} &= y_{i,3} \lor \ y_{i,2} \bullet (y_{i,1} \lor y_{i,0}) \\ y_{5i} &= y_{i,2} \bullet \overline{y_{i,1}} \bullet (y_{i,0} \lor y_{5i+1}) \\ y_{4i} &= y_{5i+1} \bullet y_{i,0} \bullet (y_{i,2} \bigoplus y_{i,1}) \lor \overline{y_{5i+1}} \bullet y_{i,2} \bullet \overline{y_{i,0}} \\ y_{3i} &= y_{i,1} \bullet (y_{i,0} \lor y_{5i+1}) \\ y_{2i} &= \overline{y_{5i+1}} \bullet \overline{y_{i,0}} \bullet (y_{i,3} \lor \overline{y_{i,2}} \bullet y_{i,1}) \lor y_{5i+1} \bullet \overline{y_{i,3}} \bullet \ y_{i,0} \bullet \overline{y_{i,2}} \bigoplus \overline{y_{i,1}} \\ y_{1i} &= \overline{y_{i,2}} \lor \overline{y_{i,1}} \bullet (y_{i,0} \lor y_{5i+1}) \end{split}$$

Symbols V, •, and  $\bigoplus$  indicate Boolean operators OR, AND, and XOR, respectively. The five "hot one code" signals are used as selection control signals for the 5:1 muxes to select the positive d+l- digit multiples {0;X; 2X; 3X; 4X; 5X}. The generation of the positive multiples {X; 2X; 3X; 4X; 5X} coded in (4221) from the BCD multiplicand is detailed in Section 4.3. To obtain the correct partial product, the selected positive multiple is 10's complemented if ys<sub>i</sub> is one. This is performed simply by a bit inversion of the positive (4221) decimal-coded multiple using a row of XOR gates controlled by ys<sub>i</sub>. The addition of one *ulp* (unit in the last place) is performed enclosing a tail-encoded bit ys<sub>i</sub> (hot one) to the next significant partial product PP[*i*+1], since it is shifted a decimal position to the left from PP[*i*]. To avoid a sign extension, and thus, to reduce the complexity of the partial product reduction tree, the partial product sign bits ys<sub>i</sub> are encoded at each leading position into two digits as

| $(PP [i]_{d+2}, P\underline{P} [i]_{d+2}) =$ | { | (ys <sub>0</sub> . ys <sub>0</sub> ys <sub>0</sub> ys <sub>0</sub> ys <sub>0</sub> ),<br>(0,111 ys <sub>i</sub> ),<br>(0,0000), | i = 0,<br>0 < i < d-1,<br>i = d -1. |

|----------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|----------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

Therefore, each partial product PP[i] is at most of (d+3) - digit length.

# 4.2 SD Radix-5 Recoding

Fig. 5 shows the diagram for partial product generation using the SD radix-5 recoding scheme. Each BCD digit of the multiplier is encoded into two digits  $Y_t^{ij} \in \{0, 1; 2\}$  and  $Y_t^{ik} \in \{-2, -1, 0, 1, 2\}$  so that  $Y_i = Y_t^{ijk} \cdot 5 + Y_t^{ik}$ . SD radix-5 "hot one code" selection signals are obtained from the BCD input digits using the following equations

$Y_{i}^{\mu} \begin{cases} y \mathbb{I}_{i}^{\mu} &= y_{i,3}; \\ y \mathbb{I}_{i}^{\mu} &= y_{i,2} \lor y_{i,1} \bullet y_{i,0}; \end{cases}$

$$\begin{split} \gamma_{t}^{Z} & \begin{cases} y_{t}(+2)_{t}^{Y} = y_{i,1} \cdot (y_{i,2} \cdot y_{i,0} \vee y_{i,2} \cdot y_{i,0}) \\ y_{t}(+1)_{t}^{Y} = \overline{y}_{i,3} \cdot y_{i,2} \cdot y_{i,1} \cdot y_{i,0} \sqrt{y_{i,2}} \cdot y_{i,1} \cdot y_{i,0} \\ y_{t}(-1)_{t}^{Y} = y_{i,3} \cdot y_{i,0} \sqrt{y_{i,2}} \cdot y_{i,1} \cdot y_{i,0} \\ y_{t}(-2)_{t}^{Y} = \overline{y_{i,3}} \cdot y_{i,0} \vee y_{i,2} \cdot y_{i,1} \cdot y_{i,0} \end{cases} \end{split}$$

Each multiplier digit  $Y_i$  generates two partial products  $PP[i]^U$  and  $PP[i]^L$ . Therefore, this scheme generates 2d partial products for a d-digit multiplier. The advantage of this recoding is that it uses a simple set of multiplicand multiples {-2X,-X,X, 2X} coded in (4221). This decimal partial product generation is comparable in latency to binary Booth radix-4, due to a faster generation of multiples.

14

in (5211). The 2d partial products generated are at most of d+2- digit length, d of them coded in (5211) (PP(i)<sup>L</sup>) and the other half in (4221) (PP(i)<sup>L</sup>).

#### 4.3 Generation of Multiplicand Multiples

All the required decimal multiplicand multiples, except the 3X multiple, are obtained in a few levels of combinational logic using different digit recoders and performing different fixed m-bit left shifts ( $Lm_{shift}$ ) in the bit-vector representation of operands. The structure of these digit recoders is discussed in Section 4.4.

Figure 6: Generation of multiplicand multiples for SD radix-10

Fig. 6 shows the block diagram for the generation of the positive multiplicand multiples  $\{X, 2X, 3X, 4X, 5X\}$  for the SD radix-10 recoding. All these multiples are coded in (4221). The X BCD multiplicand is easily recoded to (4221) using the logical expressions

# $(w_{i,3},\,w_{i,2},\,w_{i,1},\,w_{i,0}) = (x_{i,3} \lor \ x_{i,2};\,x_{i,3};\,x_{i,3} \lor \ x_{i,1};\,x_{i,0});$

where,  $x_{i,j}$  and  $w_{i,j}$  are, respectively, the bits of the BCD and (4221) representations of X. The generation of multiples is as follows:

Multiple 2X: Each BCD digit is first recoded to the (5421) decimal coding shown in Table 1 (the mapping is unique). An  $L1_{shift}$  is performed to the recoded multiplicand, obtaining the 2X multiple in BCD. Then, the 2X BCD multiple is recoded to (4221) using Expressions (4).

# Table 3: SD radix-5 selection signals.

| Dec   | BCD               | Recode  | ed Bits |                                |     |                 | Hot one signals |       |                    |          |

|-------|-------------------|---------|---------|--------------------------------|-----|-----------------|-----------------|-------|--------------------|----------|

| Value | (Y <sub>i</sub> ) | $Y_i^U$ | $Y_i^L$ | $\mathcal{Y}^{\Sigma_{i}^{N}}$ | y1¥ | $y(+2)_{1}^{2}$ | y(+1)           | y(-1) | y(−2) <del>{</del> | $ys_i^1$ |

| 0     | 0000              | 0       | 0       | 0                              | 0   | 0               | 0               | 0     | 0                  | 0        |

| 1     | 0001              | 0       | 1       | 0                              | 0   | 0               | 1               | 0     | 0                  | 0        |

| 2     | 0010              | 0       | 2       | 0                              | 0   | 1               | 0               | 0     | 0                  | 0        |

| 3     | 0011              | 1       | -2      | 0                              | 1   | 0               | 0               | 0     | 1                  | 1        |

| 4     | 0100              | 1       | -1      | 0                              | 1   | 0               | 0               | 1     | 0                  | 1        |

| 5     | 0101              | 1       | 0       | 0                              | 1   | 0               | 0               | 0     | 0                  | 0        |

| 6     | 0110              | 1       | 1       | 0                              | 1   | 0               | 1               | 0     | 0                  | 0        |

| 7     | 0111              | 1       | 2       | 0                              | 1   | 1               | 0               | 0     | 0                  | 0        |

| 8     | 1000              | 2       | -2      | 1                              | 0   | 0               | 0               | 0     | 1                  | 1        |

| 9     | 1001              | 2       | -1      | 1                              | 0   | 0               | 0               | 1     | 0                  | 1        |

Moreover, the generation of  $PP[i]^U$  (positive) only requires multiples {X, 2X}.. To obtain the correct value of  $PP[i]^U$ , the multiples selected by  $Y_t^U$  must be first multiplied by 5. This is performed by shifting 3 bits to the left the bit vector representation of the (4221) coded multiples {X, 2X}, producing, respectively, the multiples {5X; 10X} but coded in (5211). We denote by  $Lm_{abif}$  a left arithmetic binary shift of *m* bits, implemented with fixed wiring. The negative multiples {-X; -2X} are obtained by bit inverting the multiples {X; 2X}, coded in (4221), and adding an *ulp* as a hot one in the corresponding partial product. The sign bits  $ys_t^2$ , given by

$\mathcal{Y} \mathbf{S}_{i}^{\underline{r}} \qquad \qquad = \qquad \mathbf{y}_{i,3} \lor \mathbf{y}_{i,2} \bullet \overline{\mathbf{y}_{i,1}} \bullet \overline{\mathbf{y}_{i,0}} \lor \overline{\mathbf{y}_{i,2}} \bullet \mathbf{y}_{i,1} \bullet \mathbf{y}_{i,0};$

are encoded to the left of  $PP[i]^L$  and  $PP[0]^U$  as

$$\begin{array}{rcl} \boldsymbol{PP}[\boldsymbol{i}]_{d\neq 1}^{L} & = \begin{cases} (1, 1, 1, \overline{ys_{1}^{L}}) & \text{if } (0 \leq i < d - 1) \\ (0, 0, 0, 0) & \text{if } (i = d \cdot 1) \end{cases} \\ \boldsymbol{PP}[\boldsymbol{0}]_{d\neq 2}^{U} & = & (0, 0, 0, \overline{ys_{0}^{L}}) \end{cases}$$

The hot ones produced by the 10's complement of the partial products,  $(0,0,0,3^{*}2^{*})$  are just placed in the least significant digit of PP[i]<sup>U</sup> and **PP[i**]<sup>U</sup> which have a value of 0 or 5 coded

15

Multiple 4X: It is obtained as  $2X \times 2$ , where the 2X multiple is coded in (4221). The second  $\times 2$  operation is implemented as a digit recoding from (4221) to code (5211), followed by an L1<sub>abin</sub>. The design of the (4221) to (5211) digit recoders is described in Section 4.4. The  $\times 2$  operation, with input operands coded in (4221) or (5211), is also implemented in the decimal CSA trees used for partial product reduction, and therefore, it is more detailed in Section 5.1.

Multiple 5X: It is obtained by a simple  $L3_{shift}$  of the (4221) recoded multiplicand, with resultant digits coded in (5211). Then, a digit recoding from (5211) to (4221) is performed (see Section 4.4). Fig. 7 shows an example of this operation.

Figure 7: Calculation of ×5 for decimal operands coded in (4221).

Multiple 3X: It is evaluated by a carry-propagate addition of BCD multiples X and 2X in a *d*-digit BCD adder. The BCD sum digits are recoded to (4221) as indicated by previous expression. The latency of the partial product generation for the SD radix-10 scheme is constrained by the generation of 3X.The generation of (4221) decimal-coded multiples {-2X;-X; X; 2X} for the SD radix-5 recoding is shown in Fig. 8. The BCD multiplicand is first recoded to (4221) using Expressions (4). The 2X multiple is implemented as a digit recoding from (4221) to (5211) followed by an  $L1_{shift}$ . The negative multiples {-X;-2X}, coded in (4221), are obtained inverting the bits of the (4221) decimal-coded positive multiples and encoding the sign as described in Section 4.2.

Figure 8: Generation of multiplicand multiples for SD radix-5.

## 4.4 Implementation of Digit Recoders

The design of efficient digit recoders is a critical issue, due to their high impact on the performance and area of the whole multiplier. Digit recoders are used to compute the decimal multiplicand multiples and in the reduction of partial products (Section 5) to compute  $\times 2^n$  (n > 0) operations.

The logical implementation of digits recoders for BCD, BCD excess-6, and (5421) decimal codes is straightforward; since there is only a mapping of decimal digits to these codes (each decimal digit has a single 4-bit representation). However, due to the redundancy of (4221) and (5211) decimal codes, there are several choices for the digit recoding to (4221) or (5211). The sixteen 4-bit vectors of a coding can be mapped (recoded) into different subsets of 4-bit vectors of the other decimal digit. These subsets of the (4221) and (5211) codes are also decimal codings.

Among all the subsets analyzed, the non-redundant decimal codes (4221s) and (5211s) (subsets of ten 4-bit vectors), shown in Table 2, present interesting properties. In particular, these codes verify

#### $2Z(4221s) = L1_{shift}[Z(5211s)],$

that is, after shifting 1 bit to the left an operand Z represented in (5211s), the resultant bitvector represents the decimal value of 2Z coded in (4221s). This fact simplifies the implementation of ×2<sup>n</sup> operations for n > 1. Specifically, for a decimal operand Z(4221),  $Z \times 2^n$  is implemented by a first level of  $Z_i$ (4221) to  $Z_i$ (5211s) digit recoders followed by n - 1 levels of  $Z_i$ (4221s) to  $Z_i$ (5211s) digit recoders. The output of each level of digit

18

# recoders is shifted 1 bit to the left such that the most significant bit of each (5211s) digit (weight 5) is shifted out to the next decimal position (weight 10).

| Table 4 | Selected | Decimal | Codes | for the | Docodod | Digite |

|---------|----------|---------|-------|---------|---------|--------|

|         |          |         |       |         |         |        |

| Sciecte                |      |      |      |      | coucu I |

|------------------------|------|------|------|------|---------|

| Zi                     | 0    | 1    | 2    | 3    | 4       |

| Z <sub>i</sub> (4221s) | 0000 | 0001 | 0010 | 0011 | 1000    |

| Z <sub>i</sub> (5211s) | 0000 | 0001 | 0100 | 0101 | 0111    |

| Zi                     | 5    | 6    | 7    | 8    | 9       |

| Z <sub>i</sub> (4221s) | 1001 | 1010 | 1011 | 1110 | 1111    |

| Z <sub>i</sub> (5211s) | 1000 | 1001 | 1100 | 1101 | 1111    |

Moreover, in some cases, the ×2 may be simplified. In particular, the recoding given by Expression (4) maps the BCD representation into the subset (4221s). Therefore, the subsequent ×2 operations in Figs. 5 and 7 are implemented using a level of simpler (4221s) to (5211s) digit recoders. A (4221) to (5211s) digit recoder has a hardware complexity of about 27 NAND2 gates, and its critical path has (roughly) the delay of a full adder. The (4221s) to (5211s) digit recoder has a simpler hardware complexity (about 19 NAND2 gates) with 25 percent less latency.

Additionally, the inverse digit recoding (from (5211) to (4221)) is easily implemented using a single full adder, since

$$Z_i(5211) = z_{i,3} \bullet 4 + z_{i,2} \bullet 2 + z_{i,2}^* \bullet 2 + z_{i,1}^* ;$$

with  $z_{i,1}^* \bullet 2 + z_{i,0}^* = (z_{i,3} + z_{i,1} + z_{i,0}) \le 3.$

This recoder is used to generate the  $\times$ 5 multiple for the (4221) coding and in mixed (4221/5211) multioperand CSAs to convert a (5211) decimal-coded operand into the equivalent (4221) coded one.

# CHAPTER 5 PARTIAL PRODUCT REDUCTION

First, the partial product arrays are generated by the SD radix-10 and SD radix-5 encodings. Each column of p digits is reduced to two digits by means of a decimal digit p:2 CSA tree. Also, decimal carries are passed between adjacent digit columns. Here, we present the set of preferred decimal codings and the method for decimal carry-save addition. We propose the use of the (4221) and (5211) decimal codings instead of BCD for an efficient implementation of decimal carry-save addition with binary CSAs or full adders. The use of these codes avoids the need for decimal corrections, so we only need to focus on the ×2 decimal multiplications. The implementation of decimal 3:2 CSAs for the proposed codings is also described in Section 5.2. To reduce the latency of the p:2 CSA trees, we make use of the decimal digit adders introduced in Section 5.3.These digit adders, implemented with bit counters, reduce up to 9 digits coded in (4221) or (5211) to 4 digits coded in (4221). Finally, we detail the design of the proposed p:2 decimal CSA trees implemented in the SD radix-10 (in Section 5.4) and SD radix-5 architecture (in Section 5.5). We present schemes optimized for area and for delay

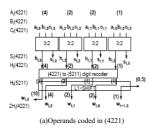

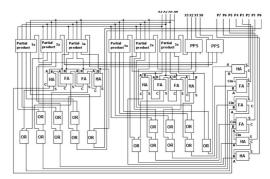

#### 5.1. Partial Product Arrays

The SD radix-10 architecture produces d + l partial products coded in (4221) of d + 3 digit length. Before being reduced, the d + l partial products PP[i] are aligned according to their decimal weights by 4i-bit wired left shifts (PP[i]× 10<sup>4</sup>). The resultant partial product array for 16-digit input operands is shown in Fig. 9. In this case, the number of digits to be reduced varies from p = 17 to p = 2. In particular, the highest columns can be reduced with the area-optimized or delay-optimized decimal 17:2 CSA trees presented in Section 5.4.

partial products: 16+3 digits wide max

S: Sign Encoding H: Hot-One 10's complement encoding X: Regular 4221 digit F: Extra digit position to support the width of multiplicand multiples

For the SD radix-5 architecture, the number of partial products generated is equal to 2*d*, *d* of them coded in (5221) and the other *d* coded in (4221) (see Section 4.2). Both PP[i]<sup>U</sup> (5211) and PP[i]<sup>L</sup>(4221) have the same weight 10<sup>1</sup>. Thus, for 16-digit input operands, the alignment of the 32 partial products results in the digit array of Fig. 10. The p-digit columns of the SD radix-5 partial product array are reduced using the mixed (4221/5211) decimal *p*:2 CSA trees presented in Section 5.5. The worst case for *d* = 16 corresponds to a column of *p* = 32 digits, reduced using a mixed (4221/5211) decimal 32:2 CSA.

Figure 10: Partial product arrays generated for 16-digit operands in the case of SD radix-5 architecture

In this figure, S: Sign Encoding H: Hot-One 10's complement encoding V: Regular 4221 digit B: Regular 5211 digit F: Extra digit position to support the width of multiplicand multiples

# 5.2. Method for Decimal Carry-Save Addition

Decimal carry-save addition methods use a two BCD word to represent sum and carry or a BCD sum word and a carry bit per digit. The first group implements decimal addition mixing binary CSAs with combinational logic for decimal correction.

22

Figure 11: BCD carry-save addition using a 4-bit 3:2 CSA

multioperand decimal tree adders using a binary CSA tree, but with operands coded in decimal codings that are more efficient than BCD.

# 5.3. Alternative Decimal Digit Encodings

Among all the possible decimal codes defined by Expression (1) in Section 2, there is a family of codes suitable for simple decimal carry-save addition. This family of decimal codings verifies that the sum of their weight bits is 9, that is,

# $\sum_{j=0}^{n} r_j = 9$

which includes the (4221), (5211), (4311), and (3321) codes, shown in Table 1. Some of these decimal codings are already known, but we use them in a different context, to design components for decimal carry-save arithmetic. Moreover, they are redundant codes, since two or more different 4-bit vectors may represent the same decimal digit. These codes have the following two properties

All the sixteen 4-bit vectors represent a decimal digit (Z<sub>i</sub> ∈ [0,9]). Therefore, any Boolean function (AND, OR, XOR) operating over the 4-bit vector representation of two or more input digits produces a 4-bit vector that represents a valid decimal digit (input and output digits represented in the same code).

In another scheme two levels of 3:2 binary CSAs is used to add the partial products iteratively. Since it uses BCD to represent decimal digits, a digit addition of +6 or +12 (Modulo 16) is required to obtain the decimal carries and to correct the sum digit. In order to reduce the contribution of the decimal corrections to the critical path, three different techniques for multioperand decimal carry-save addition were proposed. Two of them perform BCD corrections (+6 digit additions) using combinational logic and an array of binary carry-save adders (speculative adders), although a final correction is also required. A sequential decimal multiplier using these techniques uses BCD invalid combinations (overloaded BCD representation) to simplify the sum digit logic. The other approach (non-speculative adder) uses a binary CSA tree followed by a single decimal correction. In the non-speculative adder, preliminary BCD sum digits are obtained using a level of 4-bit carry propagate adders after the binary CSA tree. Finally, decimal carry and sum digit corrections are determined from the preliminary sum digit and the carries passed to the next more significant digit position in the binary CSA tree. Decimal correction is performed using combinational logic (its complexity depends on the number of input operands added) and a 3-bit carry propagate adder per digit. Among these proposals, the non-speculative adders present the best area-delay figures and are suited for tree topologies.

The addition of all decimal operands in parallel requires the use of efficient multioperand decimal tree adders. Among the different schemes, the most promising ones for fast parallel addition seem to be those using binary CSA trees or some parallel network of full adders, due to their faster and simpler logic cells (full adders against SD adder cells or radix-10 CLAs). These methods assume that decimal digits are coded in BCD. However, BCD is highly inefficient for implementing decimal carry-save addition by by means of binary arithmetic, because the need to correct the invalid 4-bit combinations (those not representing a decimal digit). Fig. 11 shows an example of the addition of 3 BCD digits using a 4-bit binary 3:2 CSA directly. In this case, the 4-bit representation (1100) of the decimal sum digit ('12') is an invalid BCD value and must be corrected to avoid overflows in subsequent BCD carry-save additions. The previous methods use different schemes to perform these BCD corrections. Moreover, the BCD carry digit must be multiplied by 2, which requires additional logic. We also implement

23

The 9's complement of a digit Z<sub>i</sub> can be obtained by inverting their bits (as a 1's complement) since

$$9\text{-}Z_i = \sum_{j=0}^{3} r_j = \sum_{j=0}^{3} z_{i,j} r_j = \sum_{j=0}^{3} (1\text{-}z_{i,j}) r_j$$

=  $\sum_{i=0}^{n} \overline{z_{i,j}} r_j$

Negative operands can be obtained by inverting the bits of the positive bit vector representation and adding a 1 *ulp*, that is,

$$-Z(r_3,r_2,r_1,r_0) = Z(r_3,r_2,r_1,r_0) + 1$$

Next, we show how these codes can be used to improve multioperand decimal carry-save addition/subtraction using these two properties

## 5.4. Algorithm

Using the first property of these alternative decimal codings, we perform fast decimal carry-save addition using a conventional 4-bit binary 3:2 CSA as

$$A_i + B_i + C_i = \sum_{i=1}^{3} (a_{i,i} + b_{i,i} + c_{i,i}) r_i$$

$$= \underline{\sum}_{j=0}^{s} s_{i,j}r_j + 2 \times \underline{\sum}_{j=0}^{s} h_{i,j}r_j = S_i + 2 \times H_i$$

with  $(r_{3f_2f_1f_0}) \in \{(4221); (5211); (4311); (3321)\}$ ,  $s_{ij}$  and  $h_{i,j}$  are the sum and carry bit of a full adder, and  $H_i \in [0, 9]$  and  $S_i \in [0, 9]$  are the decimal carry and sum digits at position *i*. No decimal correction is required because the 4-bit vector expressions of  $H_i$  and  $S_i$  represent valid decimal digits in the selected coding.

However, a decimal multiplication by 2 is required before using the carry digit  $H_i$ for later computations. Here, we restrict the analysis of decimal carry-save addition to only (5211) and (4221) decimal codes, since the generation of multiples of two for operands coded in (4311) and (3321) is more complex. Fig. 12 shows an example of  $\times 2$ multiplications for decimal operands represented in (4221) and (5211) decimal codes. To simplify the notation, we use H for the carry vector coded in (4221) and W for the carry vector coded in (5211). Thus, we have that

$$2H = 2 \times H = L1_{shift}[W]$$

Figure 12: Calculation of ×2 for decimal operands coded in (4221) and (5211).

The resultant bit vector after shifting 1 bit to the left W represents the double of H. The operand 2H is coded in (4221), since the weight bits of W are multiplied by 2 after the 1-bit left shift. The whole 2 × H multiplication is performed by a digit recoding of H<sub>i</sub> into W<sub>i</sub> followed by an L1<sub>shift</sub>[W]. The bits of W<sub>i</sub> are denoted by w<sub>i,j</sub>. The bit shifted out (w<sub>i,3</sub>) represents a decimal carry out (weight 10) to the next digit position, while the bit shifted in (w<sub>i+1,3</sub>) is a decimal carry input (weight 1).

To subtract a decimal operand coded in (4221) or (5211) using a carry-save adder, we first invert the bits of the operand and add one ulp (unit in the last place). This ulp can be placed in the free room at the least significant bit position that results from the left shift of the carry operand H.

In the following Sections, we describe how to design decimal CSAs of any number of input operands coded in (4221) or (5211). We first detail the implementation of decimal 3:2 and 4:2 CSAs using the proposed method.

#### 5.5. Decimal 3:2 and 4:2 CSAs

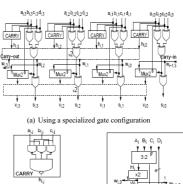

In this Section we detail the proposed implementations of a decimal 3:2 and 4:2 CSAs. We also describe the gate level implementation of the digit recoders required to perform conversions between different decimal codings. These recoders are the core logic components to compute  $\times 2^n$  multiplications, which are also required for partial product generation in multiplication.

26

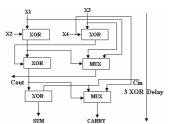

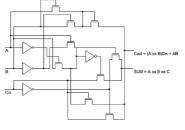

Figure15: Alternative Implementation of 4:2 Compressor with 3 XOR Delay

## 5.5.2. Gate level implementation

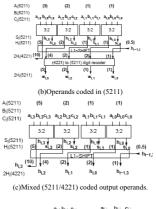

The proposed decimal 3:2 CSAs adds three decimal operands (A,B,C) coded in (4221) or (5211) and produce a decimal sum word (S) and a carry word (H) multiplied by 2 (2 × H) coded in (4221) or (5211), such that A + B + C = S + 2H. Depending on the decimal coding of the operands, we have three possible implementations of a decimal digit 3:2 CSA using a 4-bit binary 3:2 CSA, as shown in Fig. 16

The 4:2 compressor structure actually compresses five partial products bits into three [1, 2, 3]. The architecture is connected in such a way that four of the inputs are coming from the same bit position of the weight j while one bit is fed from the neighboring position j-1(known as carry-in). The outputs of 4:2 compressor consists of one bit in the position j and two bits in the position j+1. This structure is called compressor since it compresses four partial products into two(while using one bit laterally connected between adjacent 4:2 compressors). Figure 13 shows the block diagram of 4-2 compressors (full adders) in series and involves a critical path of 4 XOR delays as shown in Figure 14. An alternative implementation is shown in Figure 15. This implementation is better and involves a critical path delay of three XOR's, hence reducing the critical path delay by 1 XOR. The output C<sub>outb</sub> being independent of the input C<sub>m</sub> accelerates the carry save summation of the partial products

11 12

Figure 16(a)-(e): Proposed decimal digit (4-bit) 3:2 CSAs.

Input operands and output operands (S, H, 2H) coded in (4221) (Fig. 16(a)). The weight bits in Fig. 16 are placed in brackets above each bit column. In this case, the decimal digit 3:2 CSA consists of a 4-bit binary 3:2 CSA and a digit recoder from (4221) to (5211). In this section we show two gate level implementations of a 1-bit 3:2 CSA: one with a fast carry output (Fig. 16(d)) and one with a fast input (Fig. 16(c)). The output of the digit recoder (H<sub>i</sub>(5211)) is then left shifted by one

bit position ( $L1_{ship}$ [H<sub>4</sub>(5211)]). The recoder is placed in the carry path, so choosing an appropriate gate implementation of the binary 3:2 CSA, in this case the fast carry output configuration (Fig. 16(d)), part of the recoder delay can be hidden.

- Input and output operands coded in (5211) (Fig. 16(b)). The implementation of the (5211) decimal digit 3:2 CSA is similar to the (4221) case, except that here the 4-bit carry vector H<sub>i</sub>(5211) is 1-bit left shifted before the digit recoding.

- Input operands coded in (5211), S, H coded in (5211) but 2H coded in (4221) (Fig. 16(c)). The decimal digit 3:2 CSA consists only of a level of 4-bit 3:2 CSA with the carry output shifted 1-bit to the left.

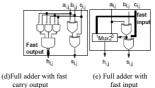

The gate level implementation of two decimal 4:2 CSAs for input and output operands coded in (4221) is shown in Fig. 17. The first decimal 4:2 CSA (Fig. 17(a)) uses a specialized gate configuration. The carry bit-vector H is computed as in binary from operands A, B and C coded in (4221). The intermediate decimal carry operand W is then obtained as  $2 \times H$ . The sum operand S (coded in (4221)) is obtained by XOR-ing the bits of A, B, C, D and W (approximately in 4 XOR gate delays). The decimal carry operand V is obtained (approximately in 6 XOR gate delays) by selecting the appropriate bits of D or W, depending on the xor of A, B, C and D, and multiplying the resulting bit vector (coded in (4221)) by 2.

The second decimal 4:2 CSA (Fig. 17(b)) is designed by interconnecting two decimal 3:2 CSAs (Fig. 17(a)). The blocks labeled as 3:2 represent a 4-bit binary 3:2 CSA. The intermediate decimal carry W is connected to a fast input of the second full adder (indicated by a letter F in Fig. 17(b)) to reduce the delay of the critical path. Thus, both implementations present a similar critical path delay (6 XOR gate delays in the carry path).

(b) Using two decimal 3:2 trees Figure 17: Proposed decimal (1-digit slice) 4:2 CSAs

## 5.5.3. Implementation of digit recoders

Carry-out

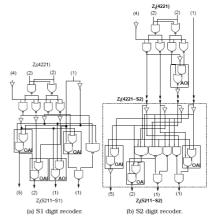

The design of efficient digit recoders is a critical issue, due to their high impact on the performance and area of a decimal multiplier. Due to the redundancy of (4221) and (5211) decimal codes, there are many choices for the digit recoding between (4221) and (5211). The sixteen 4-bit vectors of a coding can be mapped (recoded) into different subsets of 4-bit vectors of the other decimal coding representing the same decimal digit. These subsets of the (4221) and (5211) codes are also decimal codings. Among all the subsets analyzed, we have selected the non-redundant decimal codes (subsets of ten 4bit vectors) shown in Table 2 to represent the recoded digits. These codes lead to two

30

different configurations of digit recoders (S1 and S2) for the recoding from (4221) to (5211):

• The first group of codes,  $SI = \{(4221-S1), (5211-S1)\}\$  leads to a simpler implementation of a digit recoder when all the sixteen 4-bit input combinations are possible. Therefore, in general, a  $\times 2$  block is implemented by digit recoding Z(4221) into Z(5211-S1) and shifting the output one bit to the left. The gate level implementation of a S1 digit recoding of  $Z_i(4221)$  to  $Z_i(4221-S1)$  and  $Z_i(4221-S1)$  into  $Z_i(5211-S1)$ . This operation can be seen as a two-step digit recoding of  $Z_i(4221-S1)$  and  $Z_i(4221-S1)$  and  $Z_i(4221-S1)$  into  $Z_i(4221-S1)$  and  $Z_i(4221-S1)$  into  $Z_i(5211-S1)$ . The digit recoding between  $Z_i(4221-S1)$  and  $Z_i(5211-S1)$  is very simple, since the 4-bit vectors representing each decimal digit value in both decimal codes are almost similar.

| $Z_i$ | Z <sub>i</sub> (4221-S1) | Z <sub>i</sub> (5211-S1) | Z <sub>i</sub> (4221-S1) | Z <sub>i</sub> (5211-S1) |

|-------|--------------------------|--------------------------|--------------------------|--------------------------|

| 0     | 0000                     | 0000                     | 0000                     | 0000                     |

| 1     | 0001                     | 0001                     | 0001                     | 0001                     |

| 2     | 0100                     | 0100                     | 0010                     | 0100                     |

| 3     | 0101                     | 0101                     | 0011                     | 0101                     |

| 4     | 0110                     | 0111                     | 1000                     | 0111                     |

| 5     | 1001                     | 1000                     | 1001                     | 1000                     |

| 6     | 1010                     | 1010                     | 1010                     | 1001                     |

| 7     | 1011                     | 1011                     | 1011                     | 1100                     |

| 8     | 1110                     | 1110                     | 1110                     | 1101                     |

| 9     | 1111                     | 1111                     | 1111                     | 1111                     |

|       | Table 4. Se              | lected decimal           | codes for the            | recoded digits           |

• The second group of codes, S2 = {(4221-S2), (5211-S2)} verifies  $2Z(4221-S2) = L1_{shift}[Z(5211-S2)]$

that is, after shifting one bit to the left an operand represented in (5211-S2), the resultant digits are represented in (4221-S2). This fact simplifies the implementation of  $\times 2^n$  operations with |n|>1. Specifically,  $2^n\times Z$  can be

31

implemented recoding each digit  $Z_i(4221)$  to  $Z_i(4221-S2)$  followed by n stages of  $Z_i(4221-S2)$  to  $Z_i(5211-S2)$  digit recoders. The implementation of this S2 digit recoder is shown in Fig. 18(b) (the  $Z_i(4211-S2)$  to  $Z_i(5211-S2)$  recoder is shown inside the dashed line box). Moreover, when input digits into a 4-bit binary 3:2 CSA are coded in a S2 decimal coding then the resultant carry digit  $H_i$  is represented in the same S2 coding. In this case, 2×H is implemented as a row of the simpler  $H_i(4211-S2)$  to  $H_i(S211-S2)$  digit recoders with outputs or inputs 1-bit left shifted.

Figure 18: Gate level implementation of the (4221) to (5211) digit recoders. Additionally, the inverse digit recoding (from (5211) to (4221)) is easilyimplemented using a single full adder as shown in Fig. 19, since

$$\begin{split} &Z_i(5211) = z_{i,3}\left(4+1\right) + z_{i,2} \bullet 2 + z_{i,1} + z_{i,0} = z_{i,3} \bullet 4 + z_{i,2} \bullet 2 + \pi_{i,0}^* + 2 + \pi_{i,0}^* = z_{i,3} \bullet 4 + z_{i,2} \bullet 2 + \pi_{i,0}^* + 2 + \pi_{i,0}^* = z_{i,3} \bullet 2 + \pi_{i,1}^* + z_{i,0} = z_{i,3} \bullet 2 + \pi_{i,1}^* + z_{i,1} \bullet 2 + \pi_{i,1} \bullet 2 + \pi_$$

Figure 19: Implementation of a (5211) to (4221) digit recoder.

# CHAPTER 6 PROPOSED ARCHITECTURE -COMBINED DECIMAL/BINARY CARRY SAVE ADDER

In this implementation the whole binary carry-save adder tree is shared for both binary and decimal operations. The latency of the binary operation is unaffected by the incorporation of hardware support for decimal and there is reduction in the power consumption also apart from the additional area required. This additional hardware computes a decimal correction amount which is added to the binary sum to produce the correct decimal result. Since the most part of this computation is overlapped with the binary carry-save addition, the maximum overhead delay of decimal multioperand addition is bounded approximately by 10 XOR gate delays. In this design decimal correction is completely separated from the binary carry-save adder, so that decimal hardware can be easily turned off to reduce power consumption in binary operation mode. Furthermore, it has a very regular and simple structure, which facilitates the integration of the proposed method into a CAD tool for automatic synthesis.

# 6.1 ALGORITHM

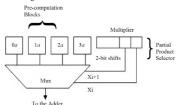

The block diagram of a 1-digit (4-bit) decimal 3:2 carry-save adder is detailed in Fig. 20. The blocks labeled as FA, 3:2, and  $\times 2$  are respectively full adders with a fast

35

operand C coded in 4221 2 as a 1-bit left shift (C <<1), that is, as a binary doubling. This would allow us to compute both binary and decimal carry-save additions in the same fashion, just by left shifting the carry output of the binary 3.2 carry-save adder.

However, since a left shift of a 4221 decimal coded operand C does not produce exactly its double 2C, we have to estimate a correction amount to be added to the binary result in order to get the correct decimal sum. Thus, a left shift of a p-digit decimal operand C coded in 4221 produces that each digit C<sub>i</sub> is modified as  $(C_i \ll 1) = c_{i,3} \cdot 10 + c_{i,2} \cdot 4 + c_{i,1} \cdot 2 + c_{i,0} \cdot 2$

On the other hand, the double of a 4221 decimal coded digit is given by

$C_i \times 2 = c_{i,3} (10-2) + c_{i,2} \bullet 4 + c_{i,1} (2+2) + c_{i,0} \bullet 2$ The operand  $2C = C \times 2$  (represented in code 4221) and the 1-bit shifted operand (C <<1) are then related by:

$2C = (C <<1) + 2 \times \sum_{k=0}^{m-2} (C_{i,1} - C_{i,3}) \times 10^{i}$ Therefore, we have to increment the decimal correction amount *W* into +2 units at digit W<sub>i</sub> if the carry bit c<sub>i,1</sub> is one or decrement it by -2 if the carry bit c<sub>i,3</sub> is one. For multi-operand addition, each intermediate carry operand C[k] of the binary carrysave adder contributes to the decimal correction amount, but not for the final carry operand, which is multiplied by 2 for decimal. A functional scheme of the proposed method for 4p-bit binary/p-digit decimal 4221 coded operands is shown in Fig. 15. For simplicity, we consider in Fig. 15 that the m input operands X[k] are aligned to the decimal point and that the sum does not overflow. For m operands, the number of intermediate carry operands C[k] generated in a binary m : 2 carry-save adder is m - 3.

The decimal correction amount W is computed in parallel with the binary carrysave addition using an array of bit counters and a decimal carry-save addition. We separate the positive ( $c[k]_{i,1}$ ) and the negative ( $c[k]_{i,3}$ ) carry bits, as soon as they are generated in the binary carry-save addition, in groups of 9 bits at most for each decimal position *i*. These groups of bits are added as

34

input (of 1 XOR delay, indicated with an F), 4-bit binary 3:2 carry save adders and decimal digit doubling units. A fixed left shift of one bit is denoted by <<1.

A binary/decimal 3:2 carry-save-adder is build in by a straightforward modification of the digit doubling unit of Fig. 20: a 4-bit 2:1 multiplexer is placed after each digit recoder and selects either the carry output of the 3:2 carry-save adder for binary mode or the output of the digit recoder for decimal mode. The output of the multiplexer is shifted one bit to the left. A combined multi-operand adder is implemented as a tree of these modified carry-save adders. Fig. 21 shows an example for 12 operands. The binary/decimal doubling units require an additional input signal dec to indicate the operation mode (dec=1 for the decimal mode).

Figure 21: Combined multi-operand adder tree: (1 digit/4-bit column)

For further area savings a more interesting alternative would be to fully reuse the binary carry-save adder for both binary and decimal multi-operand additions. In this Section we present a method to implement decimal multi-operand addition using any binary carry-save adder (such as a binary 4:2 compressor tree) and separate hardware for decimal correction. The key idea is to perform the decimal doubling  $C \times 2$  of the carry using 2q rows of 9-bit counters (or simpler counters) with output coded in 4221, where q = [(m - 3)/9] and *l* goes from 1 to q. The 4-bit sum value of a 9-bit counter represents a decimal digit W<sub>i</sub>[*l*]  $\in$  [0, 9] coded in 4221, so that the output of each row of counters is a decimal operand W[2*l*-1] or W[2*l*] of p digits coded in 4221. The decimal correction amount W is given by

## $W = 2 \times \sum_{l=1}^{n} (W[2l] - W[2l - 1])$

Since the representation 4221 is self-complementing the negative operands -W[2l - 1] are obtained by a bit inversion of W[2l - 1] and a subsequent addition of a unit in the least significant place, i.e. as if they are two's complement operands. To obtain the final sum

38

S[2q+m-2] and carry  $C[2q+m-2] \times 2$  operands, we add the 2q operands  $W[2l] \times 2$  and  $-W[2l-1] \times 2$  to the result of the binary carry-save addition S[m-2],  $C[m-2] \times 2$ . Since all operands are in 4221 code, we use binary 3:2 carry-save adders and decimal doubling units to perform a decimal (2q + 2) : 2 carry-save addition.

# 6.2 Implementation of combined decimal/binary carry save adder