# AUTOMATIC STARTING OF COMMERCIAL PUMPSETS

415

PROJECT REPORT

Submitted By

**A.SUYAMPULINGAM**

K.RAJANIKANTH

**R.RAMPRAGASH**

**C.VISWANATH**

Guided by

Mrs.RANI THOTTUNGAL, M.A., M.E., MISTE Lecturer in EEE

\* \* \*

1999 - 2000

Submitted in partial fulfillment of the requirements for the award of the Degree of BACHELOR OF ENGINEERING IN ELECTRICAL AND ELECTRONICS ENGINEERING Branch of the Bharathiar University, Coimbatore – 641046.

Department of Electrical & Electronics Engineering

Kumaraguru College of Technology

Coimbatore - 641006.

#### Department of Electrical & Electronics Engineering Kumaraguru College of Technology Coimbatore - 641006.

#### CERTIFICATE

This is to certify that the project entitled

AUTOMATIC STARTING

OF

COMMERCIAL PUMPSETS

has been submitted by

Mr.A.SUYAMPULINGAM Mr.K.RAJANIKANTH Mr.R.RAMPRAGASH Mr.C.VISWANATH

In partial fulfillment of the requirements for the award of degree of Bachelor of Engineering in the Electrical & Electronics Engineering branch of the Bharathiar University, Coimbatore – 641006 during the academic year 1999 – 2000.

| A in it of                          | Os. K. a. VALANISWA 887 a e o au jenig a e<br>Mile dang di .<br><b>Professor abo</b> Meaa |

|-------------------------------------|-------------------------------------------------------------------------------------------|

| Guide                               | department agine class                                                                    |

|                                     | Kumareguru Codega at Texasology                                                           |

|                                     | Colmbatore 621 909                                                                        |

| Certified that the candidate with U | niversity Registration No                                                                 |

|                                     |                                                                                           |

| was examined in Project Work Viv    | va-Voce held on                                                                           |

|                                     |                                                                                           |

|                                     | ••••••••••                                                                                |

| Internal Examiner                   | External Examiner                                                                         |

# ACKNOWLEDGEMENT

#### **ACKNOWLEDGEMENT**

We express our heartfelt gratitude to our guide Mrs.Rani Thottungal, M.A., M.E., MISTE, Lecturer in EEE who guided us with pleasure whenever we are in need and who stood with us always, without which it would have been difficult in finishing the project successfully

We profusely thank our most revered Professor and Head of the Department, Dr.K.A.Palaniswamy, B.E., M.Sc. (Engg)., Ph.D., C.Eng (I), MISTE, FIE, for his valuable guidance and encouragement and for providing all the facilities in the department to carry out the project.

We are much grateful to our Principal Dr.K.K.Padmanabhan, B.Sc.(Engg), M.Tech., Ph.D., for his encouragement.

We are extremely thankful to TamilNadu State Council for Science and Technology (TNSCST) for sponsoring this project.

We thank all the staff members and non-teaching staff for their kind cooperation. Also we extend our heartfelt thanks to our student friends for their help and cooperation in making the project a successful one.

# SYNOPSIS

#### **SYNOPSIS**

In domestic and industrial fields, water level controllers play a very important role. It is used to maintain the water levels in both the overhead tank and the underground sump. Whenever the water in the overhead tank is low, the motor automatically starts and pumps the water from the sump to the overhead tank, provided there is minimum water in the sump, i.e., the water level is above the foot valve. Similarly, if the water in the overhead tank is full, the motor automatically gets stopped. This is the existing system, which is useful in the rural areas.

The newly designed water level controller automatically switches ON the motor for the above conditions and for the following three new conditions.

The first condition is that whenever the water comes from the water supply board, the motor automatically switches ON and pumps the water from the sum to the overhead tank. This ensures maximum water storage utility. The next is that the motor senses the dry run due to air lock, thereby switching OFF the motor along with a beep sound to indicate the dry run. The next important feature is that it checks for over load and low voltage variations, thereby preventing the motor from damage.

# CONTENTS

#### **CONTENTS**

| CHAPTER | TITLE                      | PAGE NO |    |

|---------|----------------------------|---------|----|

|         | Certificate                | ii      |    |

|         | Acknowledgement            | V       |    |

|         | Synopsis                   | vii     |    |

|         | Contents                   | ix      |    |

| I       | INTRODUCTION               | 14      |    |

|         | 1.1 Principle of Operation |         |    |

|         | 1.2 Features               |         |    |

|         | 1.3 Voltage Protection     |         |    |

|         | 1.4 Electrodes             |         |    |

| II      | SOFTWARE DESCRIPTION       |         | 18 |

|         | 2.1 Introduction           |         |    |

|         | 2.2 Truth Table            |         |    |

|         | 2.3 Karnaugh Map           |         |    |

|         | 2.4 Logic circuit          |         |    |

| Ш  | HARDWARE DESCRIPTION             | 25 |

|----|----------------------------------|----|

|    | 3.1Introduction                  |    |

|    | 3.2 Operational Amplifiers       |    |

|    | 3.3Timers and Relays             |    |

|    | 3.4 Comparator                   |    |

|    |                                  |    |

| IV | REGULATED POWER SUPPLY           | 29 |

|    | 4.1 Introduction                 |    |

|    | 4.2 Power supply circuit         |    |

|    | 4.3 Heat sink and its purpose    |    |

|    |                                  |    |

| V  | VOLTAGE COMPARATOR               | 33 |

|    | 5.1 Introduction                 |    |

|    | 5.2 Upper and lower comparators  |    |

|    | 5.3 Comparator Circuit Operation |    |

| VI    | DRY RUN CIRCUIT                 | 37 |

|-------|---------------------------------|----|

|       | 6.1 Introduction                |    |

|       | 6.2 Timer circuit design        |    |

|       | 6.3 Driver stage                |    |

|       | 6.4 Darlington pair             |    |

|       | 6.5 Transistor sensor circuit   |    |

|       |                                 |    |

| VII   | OVERALL CIRCUIT OPERATION       | 44 |

|       |                                 |    |

| VIII  | CONCLUSION                      | 48 |

|       |                                 |    |

| REFER | ENCE                            | 50 |

|       |                                 |    |

| APPEN | DIX I                           |    |

|       | PIN CONFIGURATIONS OF IC's USED |    |

| APPEN | DIX 1I                          |    |

|       | COST DETAILS                    |    |

# **CHAPTER 1**

# INTRODUCTION

# CHAPTER I INTRODUCTION

#### 1.1 PRINCIPLE OF OPERATION

Water level controllers are most prevalent in the market today. These are best used for wells. The purpose of water level controller is to automatically pump the water from the sump to the overhead tank, whenever the water storage is less in the overhead tank and to cutoff the supply whenever the water reaches maximum level in the overhead tank.

#### 1.2 FEATURES

In addition to the above mentioned features, this water level controller provides the facility of maximum storage utility which is nothing but pumping of water to the overhead tank, whenever water comes from the municipality water board

This water level controller is also used to check the dry run, which occurs in the motor when water is not pumped due to air lock. The controller senses and switches OFF the supply along with a beep sound to indicate dry run. This saves the wastage of power.

Another feature is that timing for dry run checking can be varied depending on the head. So this water level controller can be used for buildings having larger head.

#### 1.3 VOLTAGE PROTECTION

Normally there are voltage fluctuations prevailing during peak hours. During these periods, the input voltage usually will be very low. So when there is an voltage drop, electrical appliances of higher ratings should not be used. If used there may be damage to the appliance or the fuse goes off. In order to prevent the motor from switching ON due to the conditions in the overhead tank and sump, the voltage sensing circuit is used. This circuit checks the voltage variations and switches OFF automatically. The motor runs only between 180V to 240V.

Voltage regulator is used to regulate the voltage given as input to the circuit. The regulator circuit consists of a step down transformer and IC 7812. This ensures regulated power supply to the circuit for safer operation.

#### 1.4 ELECTRODES

This water level controller uses special type of electrodes for sensing the water levels both in the over head tank and the sump. The electrodes are made of stainless steel and are non-corrosive. Another advantage of using stainless steel electrodes is that it is free from maintenance. The conductivity of stainless steel is also very high.

#### 1.5 IC's USED

The IC's used in this circuit are of Complementary Metal Oxide Semiconductor (CMOS) type. The advantage of using this type of IC's is that it can withstand up to 15V. The IC's normally used can withstand only up to 5V. So the need for using a 5V step down transformer eradicated. This also makes the circuit compact and less in cost. Heat sinks are provided for regulator IC and for Darlington pair in order to prevent the component from thermal runaway.

# **CHAPTER II**

# SOFTWARE DESCRIPTION

#### **CHAPTER II**

#### SOFTWARE DESCRIPTION

#### 2.1 INTRODUCTION

The "Automatic Starting of Commercial Pumpset" project is designed to switch ON and OFF the motor pumpset depending upon the level of the overhead tank and sump, flow of incoming water and input voltage. The electrodes sense the above conditions, which is made by stainless steel, and gives the signal to the sensing circuit. Hence a logic circuit is designed to satisfy the following conditions:

- ✓ Depending on the water levels in the overhead tank and sump the pumpset is switched ON and OFF.

- ✓ The pumpset should be started whenever there is incoming water.

- ✓ The motor should automatically shutdown whenever there is dry run during operation.

- ✓ The pumpset should switch OFF for over voltages and low voltages.

#### 2.2 TRUTH TABLE

The "Automatic starting of commercial pumpset" project is designed to switch ON and OFF the motor pumpset depending upon the levels of the overhead tank, sump level, flow of incoming water and voltage cutoff.

These levels are sensed by the electrodes, which is made of stainless steel gives the signals to the logic circuit. To design the logic circuit these water level signals are named as follows:

OHUL - P - OverHead tank Upper Level

OHLL – Q - OverHead tank Lower Level

UGLL – R - UnderGround tank Lower Level

MSU – S – Maximum Storage Utility

The different conditions for switch ON and OFF stage of motor is given in the form of truth table 1. In the truth table P, Q, R, S are the inputs of the logic circuit. In the input conditions '1' denotes the presence of water levels and '0' denotes the absence of water in the fixed or indicated levels.

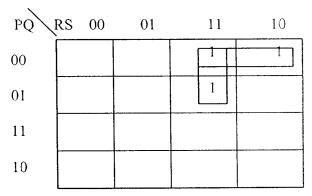

Let 'Y' be the output of the circuit. In the output column, 'I' denotes the ON condition of motor pumpset and '0' denotes the OFF condition of motor pumpset. The output equation gives the relationship between the input and output conditions. The output equation or logic equation derived by forming the Karnaugh map (Fig 2.1) for the truth table. By using the output equation logic circuit is designed.

TRUTH TABLE 1

| OHUL | OHLL | UGLL | MSU    | OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P    | Q    | R    | S      | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 0    | 0    | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 0 .  | 0    | 1      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 0    | 1    | 0      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 0    | 1    | 1      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 1    | 0    | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 1    | 0    | 1      | О                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 1    | 1    | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 1    | 1    | 1      | The state of the s |

| 1    | 0    | 0    | 0      | INV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | 0    | 0    | 1      | INV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | 0    | 1    | 0      | INV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | 0    | 1    | 1      | INV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | 1    | 0    | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1    | 1    | 0    | Bernad | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1    | 1    | 1    | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1    | 1    | 1    | A      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

In the truth table 'INV' indicates the invalid condition. The upper level in the overhead tank is reached only after passing through the lower level. Hence P=1, Q=0 is an impossible or invalid condition, because this cannot be obtained

#### 2.3 KARNAUGH MAP

The logic circuit is designed for four input conditions. So, Karnaugh map (Fig 2.1) of 4 x 4 size is drawn for designing the logic circuit in a simplified manner.

Fig 2.1Karnaugh Map

#### **LOGIC EQUATION**

$$Y = P'RS+P'Q'R - (2.1)$$

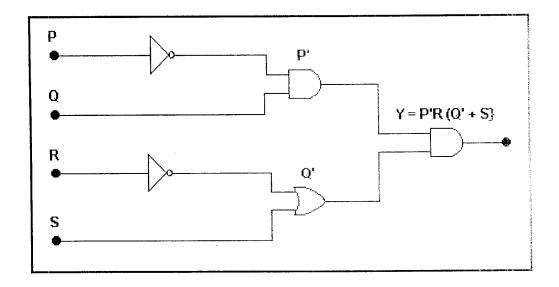

$$Y = P' R (S + Q') - (2.2)$$

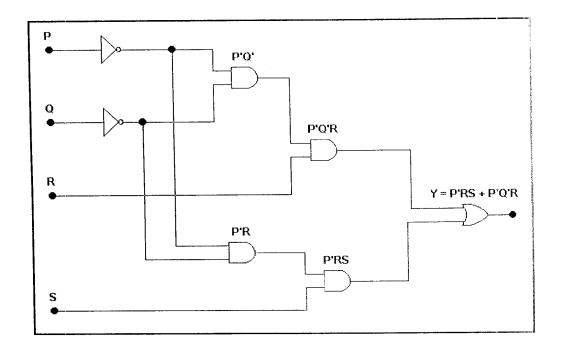

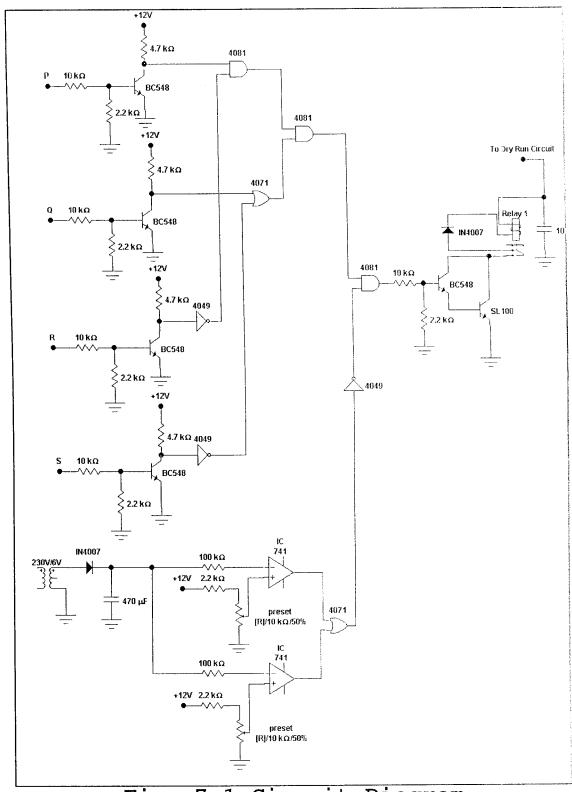

The circuit in Fig 2.2 is the logic circuit for the required logic equation.

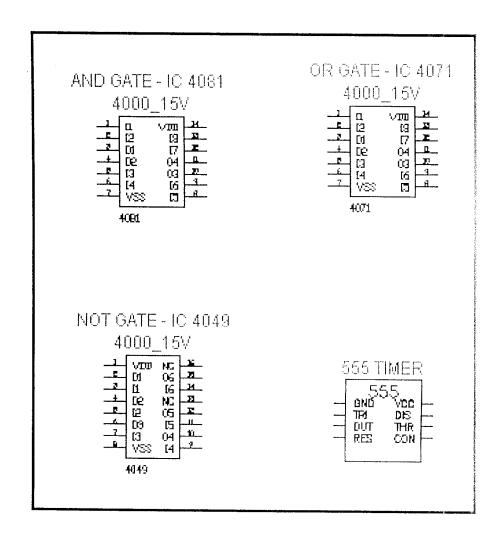

The various logic IC's used are:

AND Gate - IC 4081

OR Gate - IC 4071

NOT Gate - IC4049

The output signal is from the AND gate is anded with the voltage cutoff circuit output. This logic circuit is designed using transistors and CMOS logic IC's. Transistors act as inverters. So when there is no supply the transistor output will be in the high state. This principle is used for sensing the levels in the overhead tank and sump. CMOS logic IC's are used because it can withstand up to 15V. So the need for a 250V/5V step down transformer is eradicated.

Fig 2.2 Logic Circuit

Fig 2.3 Simplified Logic Circuit

# **CHAPTER III**

### HARDWARE DESCRIPTION

#### **CHAPTER III**

#### HARDWARE DESCRIPTION

#### 3.1 INTRODUCTION

This chapter provides the details of the various hardware components used in this project and its operation.

#### 3.2 OPERATIONAL AMPLIFIERS

An operation amplifier (OpAmp) is a direct coupled high gain amplifier consisting of one or more differential amplifiers, followed by a level translator and an output stage. There are five basic terminals: two input terminals, one output terminal and two supply terminals.

The operational amplifier, IC 741, used here is of dual inline package with 8 pins. It is used in linear applications such as adder, subtractor, voltage to current converter, etc and non-linear applications such as clipper, clamper, rectifier, etc. In this circuit we have used it as a comparator to check the variations in input voltage

#### 3.3 COMPARATOR

One such application of operational amplifier (pin configurations in Annexure I ) operating in non-linear manner is voltage comparator. A comparator is a circuit, which compares a signal voltage applied at on input of an operational amplifier with a known reference voltage at the other input. In this project, operational amplifiers are used as a comparator to check the variations in the input voltage applied to the circuit. The circuit is discussed in detail in chapter IV

#### 3.4 RELAYS

A relay is a device, which disconnects or connects the working system from the supply. The relay has on relay coil and one moving contact. When the relay contact is energized, the contact will move accordingly.

There are two types of relays available, one is normally open type and another one is normally closed type. In former type the relay contact is always in open state and when the coil is energized, it will close the circuit. Whereas in the latter type, the contact is always in closed state and when the coil is energized it will open the circuit. Here two contact relays are also used. They are used to switch ON and OFF the supply.

Relays are used in the dry run circuit.

#### 3.5 TIMERS

The 555 timer is a highly stable device for generating accurate time delay or oscillations. The 555 timer (Pin configuration in Annexure I) can be used with supply voltage in the range of +5V to +18V and can drive load up to 200mA. It is compatible with both TTL and CMOS logic circuits.

The CMOS logic circuit is employed here, because of wide range of power supply voltage. The 555 timer is versatile and easy to use in various applications such as oscillator pulse generator, ramp and square wave generator, monoshot multivibrator, burglar alarm, traffic light control, voltage monitor, etc. Timers are used in the dry run circuit, which is discussed in chapter V.

### **CHAPTER IV**

### REGULATED POWER SUPPLY

#### **CHAPTER IV**

#### **REGULATED POWER SUPPLY**

#### 4.1 INTRODUCTION

The power supply circuit is used to provide a constant regulated power supply to the sensing circuit and the electrodes. This circuit safeguards the electronic components used in other circuits from high voltage fluctuations and voltage drop. In this chapter, the power supply circuit and the purpose of using heat sinks are discussed.

#### 4.2 POWER SUPPLY CIRCUIT

Power supply circuit contains a 230v/18-0-18v step-down, center tapped transformer, which gives 18v secondary voltage. This voltage is rectified and the rectified dc output voltage is given to IC 7812 regulator. The regulator supplies the +12v dc voltage to the whole circuit. The function of a voltage regulator is to provide a stable dc voltage for powering other electronic circuits.

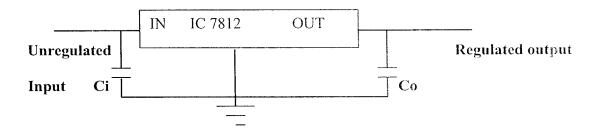

Fig 4.1 Standard Representation of IC 7812

IC 7812 is a three terminal, positive fixed voltage regulator. It is an 12v regulator. The unregulated dc voltage is given to the input terminal and the regulated output is obtained through output terminal.

The capacitor circuit is usually connected between input terminal and ground to cancel the inductive effects due to long distribution leads. The output capacitor improves the transient response.

It gives low cost, high reliability, and reduction in size and excellent performance.

#### 4.3 PURPOSE OF HEAT SINK

The IC 7812 has a temperature sensor, which turns off the IC when it becomes too hot. In order to dissipate the heat, a heat sink is provided for IC 7812. The IC is usually provided with a heat sink, to

provide the rated maximum output current and to prevent the thermal shut down problem.

#### 4.4 HEAT SINK FOR TRANSISTOR

The unstable condition owing to rise in temperature, the collector current continues to increase is known as thermal runaway.

Thermal runaway must always be avoided, otherwise the transistor may be damaged. To overcome this problem the heat sink will be provided.

Transistors handle large currents. They always heat up during operation. Since transistor is a temperature dependent device, the heat generated must be dissipated to the surroundings in order to keep the temperature within permissible limits. Generally the transistor is fixed on a metal sheet so that additional heat is transferred to the aluminium sheet. The metal sheet that serves to dissipate the additional heat from the transistor is known as heat sink.

### **CHAPTER V**

# **VOLTAGE COMPARATOR**

#### **CHAPTER V**

#### **COMPARATOR CIRCUIT**

#### **5.1 COMPARATOR**

A comparator is the open-loop configuration of op-amp.

It is a circuit, which compares a signal voltage applied at one of the input of an op-amp with a known reference voltage at the other input.

Types Of Comparator:

- Inverting

- Non-Inverting

#### **5.2 OPERATION**

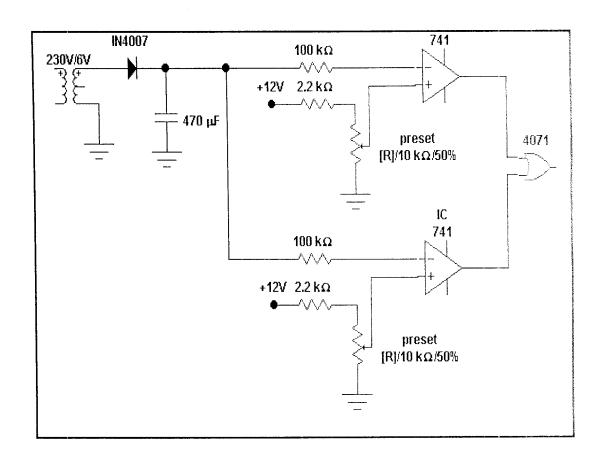

Voltage cutoff circuit contains two comparators, that is, lower and upper comparator (Fig 5.1). Reference voltage is obtained by rectifying the 6v-ac signal, which is from 230v/6v transformer as shown in fig 5.1.

Lower comparator is the inverting comparator, which senses the lower limit of the voltage supply by providing 12v to the inverting terminal of IC 741 through preset.

Upper comparator is the non-inverting comparator, which senses the upper limit of the supply voltage by giving 12V to the non-inverting terminal of op-amp through preset.

of the comparator will be '0'. Otherwise we will get the output as '1' at the sixth pin of the op-amp. If the voltage is below 180 or more than 240 the comparator output will be '1'. The output of the comparators are given to the OR gate as the input. Then the output of this gate is inverted by an inverter and then the output of the inverter is given as input to the AND gate.

If the voltage is between 180 to 240 then the output of the OR gate is '0' and the output of the inverter is '0'. If any one of the input of OR is '1', we get '0' output at the input of the AND gate, because the output of the OR gate is '1'.

Fig 5.1 Comparator Circuit

# **CHAPTER VI**

# DRY RUN CIRCUIT

#### **CHAPTER VI**

#### **DRY RUN CIRCUIT**

#### 6.1 NEED FOR DRY RUN CIRCUIT

The dry run circuit is used to sense whether the water flows in the outlet pipe present in the overhead tank, when the motor is switched ON. This problem occurs when there is a leak in the pipe. It may also be due to improper fitting or damage of foot valve. So when the motor pumpset runs, only air will be pumped instead of water. This may lead to loss of power and damage of coil. In order to prevent this from happening, we go for dry run sensing circuit. This circuit consists of a sensing part, which is the transistor, a timer circuit and relay circuit.

#### **6.2 TRANSISTOR (SENSING) CIRCUIT**

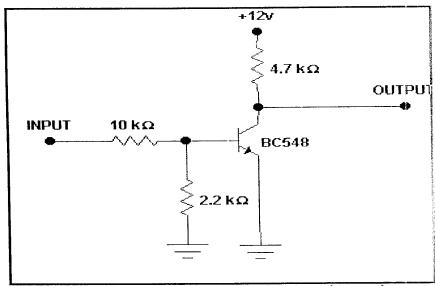

To sense the presence of water at various conditions the transistor logic circuit is used. Two electrodes are used to sense the signal. One electrode is a common electrode to which 12V supply is given to it. Another electrode is the input electrode. These two electrodes are placed in parallel with each other. So when water flows between them, the circuit becomes closed. The signal voltage acts as input voltage of transistor, that

is,  $V_{BE}$ . Now the output voltage  $V_{CE}$ , will be zero. The emitter terminal is grounded. If there is no water flow in the outlet, the output voltage will be '1' as there is no contact between the electrodes. Here the transistor acts as sensor, amplifier and inverter. The transistor amplifies, senses and inverts the input base voltage.

#### **6.3 TIMER CIRCUIT DESIGN**

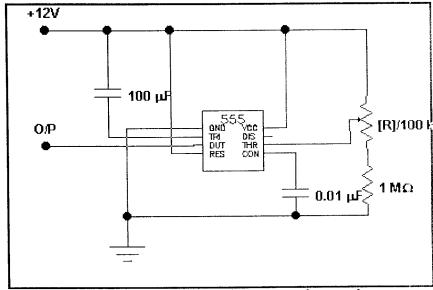

The timer circuit is designed for sensing the dry run condition of the motor. Practically, the overhead tank height from the sump varies drastically in all places i.e., for multistoried buildings the head varies depending on the number of floors. So the time for the water to reach the overhead tank from the sump varies with respect to head. In order to fix the time duration depending on the head we go for a variable time delay.

Let T be the time delay, R be resistance and C be the capacitance.

For monostable multivibrator, T = 1.1RC.

For two minutes delay, choose  $R = 1 \text{ M}\Omega$ ,  $C = 100 \mu f$ .

When the motor is switched ON the input signal is given to the timer. The signal will be in the high state for the specified time delay depending on the value of R and C as mentioned above. The signal returns to the normal state and the output of timer is given as input to the logic gate to energize the relay.

If there is no water supply in the outlet, the logic gate output will be '1' and the relay switches OFF the motor. If there is water supply in the outlet, the motor will continue to run as the logic gate output is '0'. To vary the time delay, depending upon the head of the water, the variable resistor  $100k\Omega$  pot is connected in series with the resistor. By varying the potentiometer we can change the time delay.

#### **6.4 DARLINGTON PAIR**

The stage that immediately proceeds the output stage is called driver stage. It operates as a Class A power amplifier and supplies the drive for the output stage, i.e. relay circuit. Here to drive the relay circuit, a Darlington pair is used. It amplifies the output power.

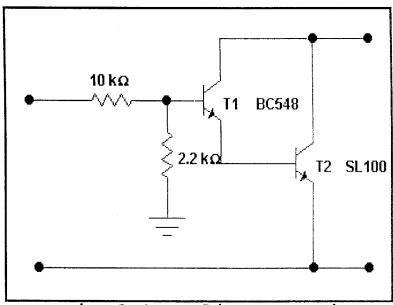

Darlington pair shown in Fig 6.4 consists of two common emitter configuration transistors, T1 (BC548) and T2 (SL100), with emitter of T1 connected to the base of T2. The collectors of both the transistors are joined together and the emitter of T2 forming the common emitter terminal. This pair amplifies the voltage and power level of the output signal to the relay circuit. It also has two resistors, which acts as a pull down resistors.

Fig 6.1 Sensing Circuit

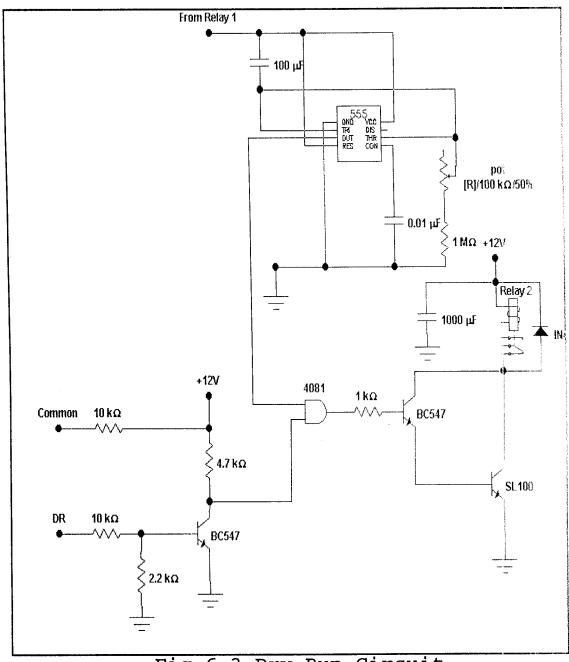

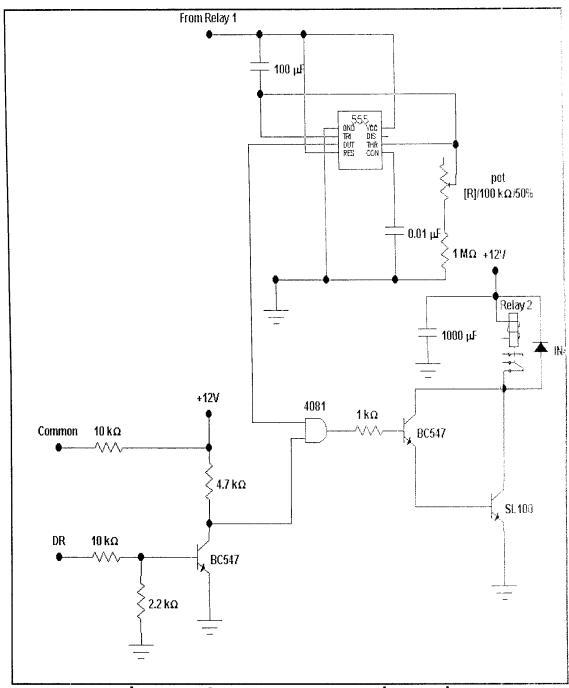

Fig 6.2 Timer Circuit

Fig 6.3 Dry Run Circuit

Fig 6.4 Darlington Pair

## **CHAPTER VII**

## FABRICATION AND TESTING OF CIRCUIT

#### **CHAPTER VII**

#### FABRICATION AND TESTING OF THE CIRCUIT

The circuit shown in Fig 7.1 and 7.2 are fabricated together to form overall control kit. The signals from the electrodes are given as inputs P, Q, R and S to the logic IC's. The output of the electrodes P and R are inverted and given as input to an AND gate. The output of the electrodes Q and S are inverted and given as input to an OR gate. Depending on the conditions in the overhead and underground tanks the logic output varies. The output of the two gates are given as input to an AND gate. The output of this gate is considered as the final output of the transistor or sensing circuit. The output will be as shown in the truth table.

In the comparator circuit, the output of the upper and lower comparators are given to an OR gate, which is inverted and given as input to an AND gate. The output of the sensing circuit is also given to this logic gate. The output of this gate is used to energize the relay through the Darlington pair.

The power supply circuit provides a constant regulated supply of power. The circuit consists of a 230/18V transformer and regulator IC 7812. The IC is provided with a heat sink, in order to prevent it from damage due to thermal runaway.

In the dry run circuit, timer and sensing circuits are used. The 555 timer gives a time delay for a particular time interval, designed using T=1.1RC. The output of the timer is given as a input to an AND gate. The output of the sensing circuit is also given as input to this gate. The output of this gate energizes the relay, which in turn switches ON or OFF the motor according to the conditions prevailing in the upper and lower tanks.

The above operation is carried out using nine stainless steel electrodes. We use five electrodes in the overhead tank and four electrodes in the sump. The electrodes are connected through multistranded wires from the kit. The kit consists of a rectangular printed circuit board, two sterp down transformers and a switch to turn ON the motor manually, in case of any problem in the kit.

The cabinet is made of steel with a highly coated mica to prevent rusting or damage due to rough handling. The printed circuit board

is tested by taking any one of the conditions in the truth table, as listed in chapter two. The test is carried for all the conditions in the truth table. Similarly the voltage comparator circuit is tested for changes in the input voltage by using an auto transformer.

The dry run circuit is tested by making the dry run electrode output '0', that is motor runs without pumping any water to the over head tank. After one minute, the motor stops along with a continuous beep sound till the kit is reset.

All the above testing is carried out using two aquarium glass tanks, one as the overhead tank and the other as the sump. A 0.5HP motor is used to pump the water for the above conditions mentioned in the truth table. Thus the circuit is designed, fabricated, tested and found work satisfactorily.

Fig 7.1 Circuit Diagram

Fig 7.2 Dry Run Circuit

# **CHAPTER VIII**

# CONCLUSION

#### **CHAPTER VIII**

#### **CONCLUSION**

The automatic starting of commercial pumpsets has been developed with an aim of minimizing the cost, external features and to make it compatible so that it will be useful for commercial purposes.

The main features of this project are:

- ✓ It is of low cost

- ✓ Very compact

- ✓ Reliable

- ✓ Maintenance free

- ✓ Highly non-corrosive stainless steel electrodes

- ✓ CMOS logic circuit

- ✓ Dry run detection and alarm

- ✓ Maximum storage utility

- ✓ Automatic voltage cut off

- ✓ Variable time delay for various heads

- ✓ Bypass switch for manual operation

# REFERENCES

#### **ANNEXURE I**

### PIN CONFIGURATIONS OF IC's USED

### ANNEXURE II

### TOTAL COST FOR PROJECT KIT

| S.No | Particulars     | Cost in Rs. |

|------|-----------------|-------------|

| 1    | Components      | 550.00      |

| 2    | PCB Fabrication | 350.00      |

| 3    | Cabinet         | 100.00      |

| 4    | Electrodes      | 100.00      |

| 5    | Miscellaneous   | 150.00      |

|      | Total           | 1250.00     |