# ECONOMIC VERSION OF OVERHEAD CLEANER CONTROLLER

PROPERTY STATES

PROJECT REPORT

SUBMITTED BY

P.BHARATHI N.KATHIRESH KUMAR P.G.MAGENDRAN V.RAJESH

UNDER THE GUIDANCE OF

MR.P.RAJENDRAN M.Tech., ASSISTANT PROFESSOR, DEPT OF MCE

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE OF

BACHELOR OF ENGINEERING IN

**MECHATRONICS ENGINEERING**

OF BHARATHIAR UNIVERSITY, COIMBATORE

DEPARTMENT OF MECHATRONICS ENGINEERING

KUMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE-641006

## KUMARAGURU COLLEGE OF TECHNOLOGY

COIMBATORE - 641 006

## DEPARTMENT OF MECHATRONICS ENGINEERING

#### CERTIFICATE

This is to certify that this project entitled

## ECONOMIC VERSION OF OVERHEAD CLEANER CONTROLLER

has been submitted by

| In partial fulfillment of the requirements for the award of the degree of                              |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bachelor of Engineering in Mechatronics Engineering                                                    |  |  |  |  |  |  |

| Branch of Bharathiar University, Coimbatore - 641 046 during the                                       |  |  |  |  |  |  |

| Academic year 2002-2003                                                                                |  |  |  |  |  |  |

| (Guide) (Head of the Department)  Certified that the candidate was examined by us in the project work. |  |  |  |  |  |  |

| Viva-Voce examination held on                                                                          |  |  |  |  |  |  |

| University Register Number                                                                             |  |  |  |  |  |  |

| ••••••                                                                                                 |  |  |  |  |  |  |

|                                                                                                        |  |  |  |  |  |  |

| ·                                                                                                      |  |  |  |  |  |  |

| ·                                                                                                      |  |  |  |  |  |  |

(Internal Examiner)

(External Examiner)

## **ELECTRIC AND INDUSTRIES LIMITED**

: MULLIPADI VILLAGE, TAMARAIKULAM PO, POLLACHI - 642 109. COIMBATORE DISTRICT (04259) 259351, 259352, 259213, 259585, 259586

12/03/2003

## PROJECT COMPLETION CERTIFICATE

is to certify that Ms P.Bharathi, Mr.N.Kathiresh Kumar, Mr.P.G.Magendran Mr.V.Rajesh of IV B.E. Mechatronics Engineering, Kumaraguru College Of nology has successfully completed the project titled "Economic Version Overhead Cleaner Controller" as part of their curriculum from 29th 2002 to 20th February 2003.

conduct was good and performance was upto our satisfaction during their are. We wish them all the best for a prosperous future.

> SWARASAMY Sr.MANAGER-WORKS

## )TE:

Due to technical reasons and contract regulations we are not in a sition to offer the software in executable form or the coding.

GD. OFFICE :"ELGI TOWERS", P.B No.7165, 737-D, GREEN FIELDS, PULIAKULAM ROAD, COIMBATORE - 641045, 7. OFFICE . ELGI 104VERG , F.B NO. 710, 707-D, GREEN I IEEBO, I GERNARDER ROOM, GOMBATORE PARTIES OF 191-0422 - 2311711, Fax: 2314411, Email: elgletectric@el.jet.co.in, Website: www.elgletectric.com.

## **ACKNOWLEDGEMENT**

We express our sincere thanks to our project guide Mr.P.Rajendran, M.Tech.,

Assistant Professor in Mechatronics Engineering Department for his parallel support, guidance and

zeal offered in completing this project successfully.

We profusely thank Dr.V. Gunaraj, Head of the Department of Mechatronics Engineering, who has given his consent to our project and for his valuable advice and encouragement.

We also express our profound and sincere gratitude to our beloved Principal,

Dr. K. K. Padmanaban, B,Sc. (Engg), M.Tech, PH.D., M.I.S.T.E, and F.I.E., who has extended his goodwill by allowing us to utilize all the college facilities.

We would like to express our thanks to Mr. Easwaraswamy, Manager, ELGI ELECTRIC AND INDUSTRIES LTD, Coimbatore for permitting us to do the project.

We would like to thank Mr.S. Madhurangan, Deputy Manager, ELGI ELECTRIC AND INDUSTRIES LTD, Coimbatore for his services rendered in developing this project.

We would like to thank Mr. Saravanan, Technical Services, ELGI ELECTRIC AND INDUSTRIES LTD, Coimbatore and Mr. Saravana Kumar of PRICOL LTD for their suggestions regarding this project.

Finally we also thank all the staff members and non teaching staff members who have readily rendered their helping hand towards the project.

#### **SYNOPSIS**

The main objective of this project is to design and implement a microcontroller based 'Economic Version Of Overhead Cleaner Controller'.

Overhead travelling cleaners are widely used in textile spinning & weaving units to collect the waste cotton called as fluff, which not removed properly may affect the quality of thread weaved & also creates an unpleasant environment for the workers.

In the current scenario, overhead cleaners are provided with an electronic control to ensure high reliability and better rated performance when compared to the traditional cleaning systems, but the disadvantage being the cost involved which may not be affordable for small scale units.

With rapid development in the field of electronics, this economic version of overhead cleaner controller opts in making a compromise on price with acceptable performance. The overhead cleaner controller uses a 20 pin AT892051 microcontroller to control the operation of the overhead cleaner.

The flash memory microcontroller performs its task efficiently remaining flexible and cost effective. This equipment is versatile and compatible with industrial (real time) requirements and hence to be sought by textile mills. This modified version of overhead cleaner controller is believed to reduce the cost involved in maintaining a dust free environment in textile units.

We are very sure that the execution of this project with so much cost savings to the clients will fetch not only good name to the company but also number of orders and thereby the company can establish a good market in providing cleaning solutions to textile mills.

| HP .    | CONTENTS                              | PAGE NO |  |

|---------|---------------------------------------|---------|--|

|         | ACKNOWLEDGEMENT                       |         |  |

|         | SYNOPSIS                              |         |  |

|         | O DI OTI OBI                          | 1       |  |

| 1.      | INTRODUCTION                          | 2       |  |

| 2.      | FUNCTIONAL DESCRIPTION                |         |  |

|         | 2.1 OVER HEAD CLEANER                 |         |  |

|         | 2.2 OVER HEAD CLEANER CONTROLLER      | 4       |  |

| 3.      | SYSTEM DESCRIPTION                    |         |  |

|         | 3.1 BLOCK DIAGRAMOF OHCC              |         |  |

|         | 3.2 DESCRIPTION                       |         |  |

|         | 3.3 SYSTEM LAYOUT                     | 12      |  |

| 4.      | HARDWARE DESCRIPTION                  | 12      |  |

|         | 4.1 OPTOCOUPLER                       |         |  |

|         | 4.2 TRIAC                             |         |  |

|         | 4.3 MOTORS                            |         |  |

|         | 4.4 POWER SUPPLY                      | 40      |  |

| 5.      | SYSTEM WORKING                        | 18      |  |

|         | 5.1 RESPONSE OF OHCC TO INPUT SIGNALS |         |  |

|         | 5.2 FIELD WORKING                     |         |  |

| 6.      | LOGICAL CONTROL FLOW                  | 22      |  |

| 7.      | COMPARATIVE STUDY                     | 27      |  |

| 8.      | FRATURES                              | 29      |  |

|         | 8.1 SPECIAL FEATURES                  |         |  |

|         | 8.2 OPTIONAL FEATURES                 |         |  |

|         | 8.3 SAFETY                            |         |  |

| 9.      | CONCLUSION                            | 31      |  |

| <i></i> |                                       |         |  |

## REFERENCE

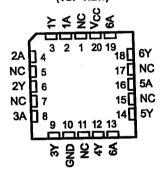

APPENDIX: 1 PIN DESCRIPTION OF AT89C2051

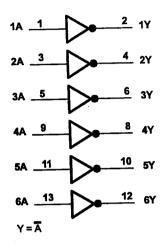

APPENDIX: 2 DATASHEET OF OPTOCOUPLER

APPENDIX: 3 DATASHEET OF TRIAC

APPENDIX: 4 DATASHEET OF DRIVER

APPENDIX: 5 INSTRUCTION SET

#### CHAPTER 1

#### INTRODUCTION

In textile industries where cotton is made into thread, unwanted cotton dust called fluff is formed. The so formed fluff disperses out in the surroundings and creates an uncomfortable environment for the people working there. This affects the employee's health, company's productivity and also reduces the performance of the machine. So, some preventive measures become indispensable.

Hence cleaning being an integral part of every textile mill, an over head cleaner offers state - of - the - art solution to cleaning. It is an equipment that moves parallely above the spinning machine on a track, absorbing the cotton dust in the premises.

The over head cleaner can be driven by a microcontroller or a microprocessor. This project uses AT892051 microcontroller as the basic controlling element to enhance the working of the over head cleaner, with a simple programming logic.

The overview of the over head cleaner controller and the detailed functional description of the type of control employed, are dealt with in the forth coming chapters.

## **FUNCTIONAL DESCRIPTION**

#### **CHAPTER 2**

## **FUNCTIONAL DESCRIPTION**

## 2.1 OVER HEAD CLEANER:

The overhead cleaner is divided into two basic units according to their functions. They are:

- ➤ Mobile unit

- Sucking unit

#### 2.1.1 MOBILE UNIT:

This unit is responsible for the circular or translatory motion of the cleaner. It is controlled by a driver motor.

## 2.1.2 SUCKING UNIT:

This is similar to a vacuum cleaner. It absorbs and accumulates cotton dust to discharge later. The collected cotton can be reused. This unit is controlled by a fan motor.

As there is a need for overhead cleaner, the automation of its working proves to be useful. The over head cleaner is controlled by an electronic logic board called the 'Over bead cleaner controller'.

## 2.2 OVER HEAD CLEANER CONTROLLER:

The over head cleaner controller has the following functions:

- > It drives the cleaner and reverses it at the ends. The controller senses the 'START' signal and operates the over head cleaner. As soon as the OHC reaches the ends of the trail, the controller reverses the direction of motion of the OHC.

- $\triangleright$  The ends of track are sensed by using sensors.

- > In case of endless loop system, the OHCC can stop OHC for discharging, in the middle.

- > Sensors are used to recognize the obstacles and OHCC reverses the direction of OHC if any obstacle is detected.

SYSTEM DESCRIPTION

#### **CHAPTER 3**

#### SYSTEM DESCRIPTION

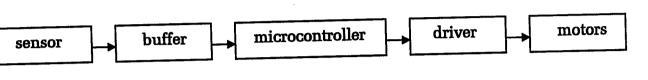

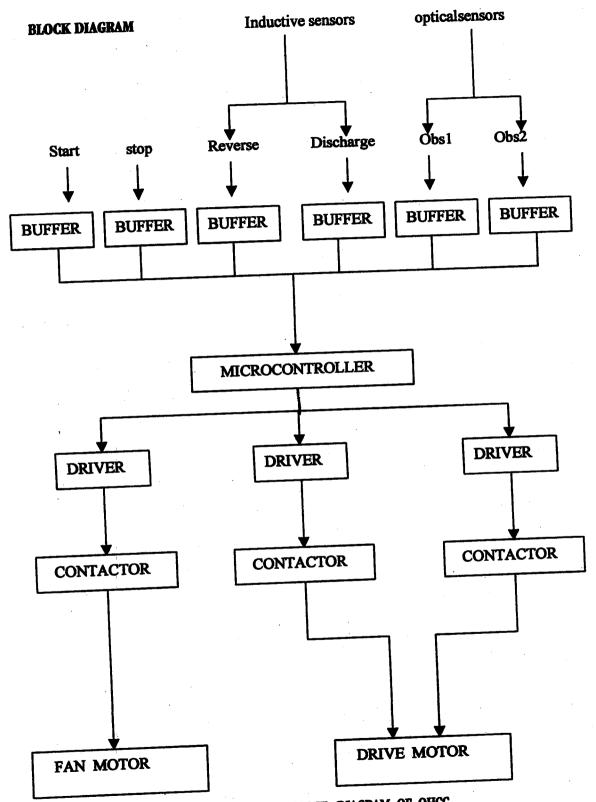

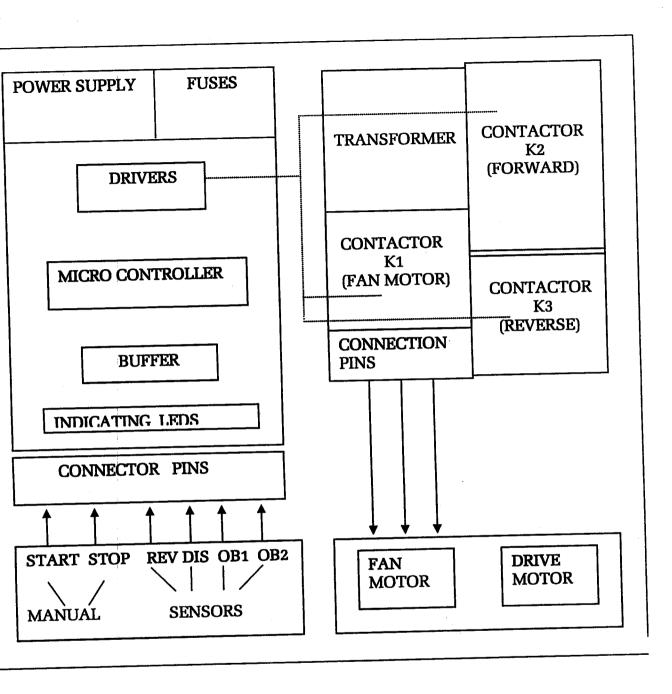

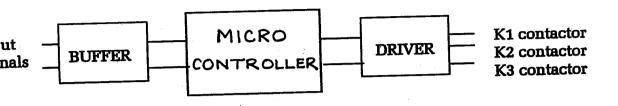

## 3.1 BASIC BLOCK DIAGRAM OF OHCC:

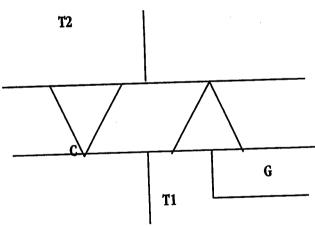

Fig: 3.1

The system working is better understood by having a detailed study of individual components.

## 3.2 DESCRIPTION:

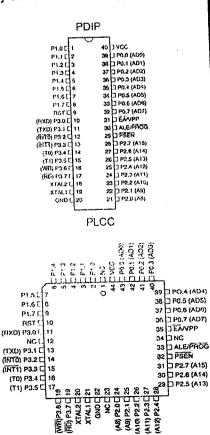

The OHCC consists of the following blocks:

- 1. Input signals

- 2. Buffer

- 3. Microcontroller

- 4. Driver

- 5. Contactor

## 3.2.1. INPUT SIGNALS:

The OHCC controls the over head cleaner according to the input signals . There are totally five input signals viz.,

- ➤ Start

- ➤ Stop

- > Auto Reverse

- Discharge

- ➤ Obstacle 1 & 2

#### $\triangleright$ START:

This signal literally starts the OHC. The OHCC energizes the sucking unit first and then the mobile unit later (i.e.) after a small delay.

#### > STOP:

This signal brings the OHC to an off condition. As soon as this signal is received, the OHCC disables the sucking unit and mobile unit.

## > AUTO REVERSE:

When the OHCC receives this signal it allows OHC to stop and wait for a time called 'reversing delay'. After this delay the OHC starts to travel in an opposite direction. The sucking unit stays on for this delay period.

#### > DISCHARGE:

When the OHCC receives this signal it stops OHC for a pre-set time called 'discharge delay'. After this delay the OHC continues to travel in the same direction.

The sucking unit is disabled during this time and the OHC discharges the collected cotton dust.

#### > OBSTACLE 1:

This signal indicates the presence of an obstacle in the forward path of the cleaner. This signal is sensed by OHCC and it changes the direction of motion of the OHC.

#### > OBSTACLE 2:

This signal indicates the presence of an obstacle in the reverse path of the OHC. The OHCC senses this signal and reverses the direction of OHC.

Out of these signals the start and stop signals are generated manually using push button switches, the reverse and discharge signals are generated by proximity sensors and the obstacle signals are given by optical sensors.

These five signals define the basic working of cleaner. Apart from these, a number of other input signals can also be included to make the cleaner perform additional functions.

FIG 3. 2 DETAILED BLOCK DIAGRAM OF OHCC

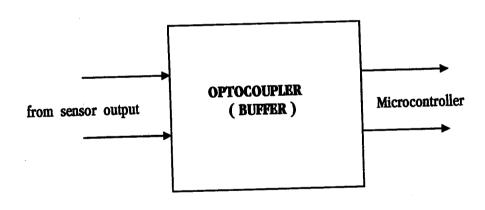

## 3.2.2. BUFFER:

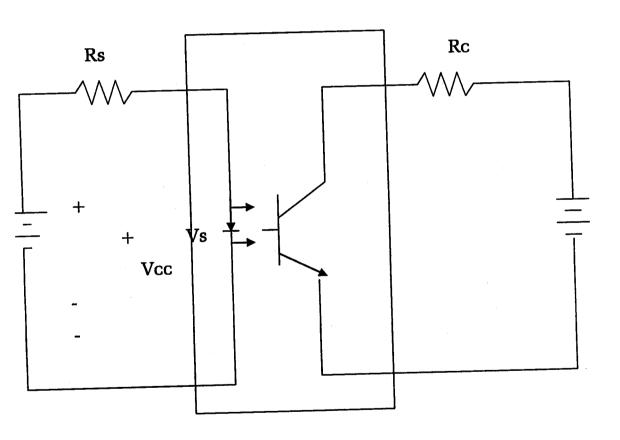

The buffer can be called as a 'matching unit'. In OHCC the buffer acts as a step down transformer. It couples the sensor outputs with the input of the microcontroller.

As opto coupler acts as a buffer in this case. It couples the sensors working with 24V supply voltage to the microcontroller working with 5V supply.

Each sensor needs a buffer unit to get connected to the microcontroller.

FIG 3.3 BLOCK OF OPTOCOUPLER

## 3.2.3. MICROCONTROLLER:

The microcontroller controls the entire working of the OHC depending on the signals received. The tasks corresponding to the input signals are stored as programs in the microcontroller. As soon as the OHCC is switched on the microcontroller runs the corresponding subroutine of the input signals that gets high. Thus it controls the movement of the cleaner using motors. This mechanism goes on until OHC is switched off.

## 3.2.4. DRIVER:

As the microcontroller cannot drive the motors directly, a drive stage is necessary in between them. The driver can be a transistor, operated as a switch for DC contactors. It couples the microcontroller to the contactor working at 24V supply, (i.e.) it drives the contactors. This project uses a TRIAC as a driver to drive the AC contactors.

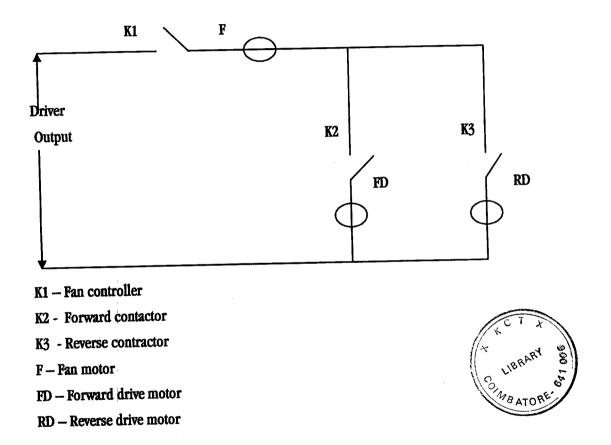

FIG: 3.4 CONTACTOR - DRIVER CONNECTION

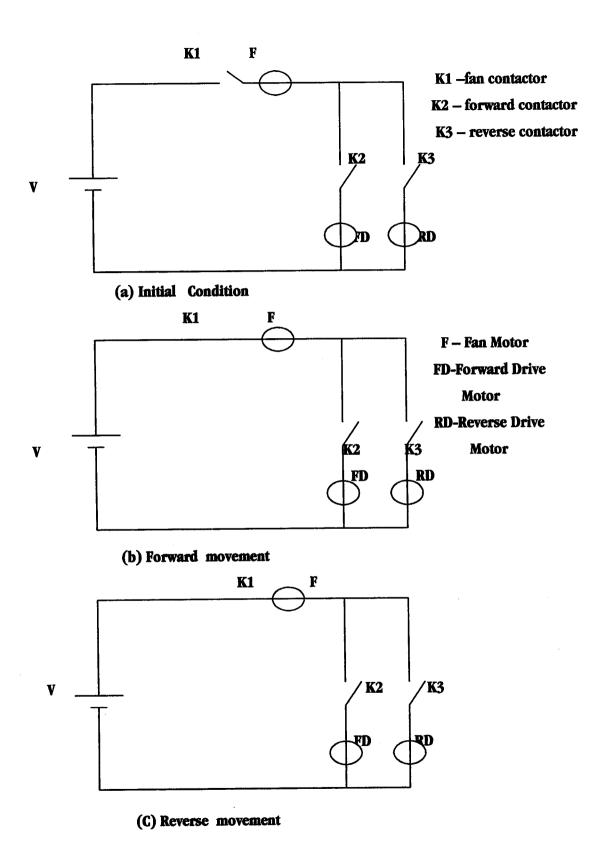

#### 5. CONTACTOR:

The contactor runs the fan and drive motors as required. It is actually a relay working at higher voltages. As the contactor is energized, the corresponding motor will run. Depending on which contactor is energized the OHC will move in forward or reverse direction.

Fig 3.5 Equivalent Circuit for Contactors & Motors switching

#### SYSTEM LAYOUT:

Fig 3.6 Layout of OHCC

The system layout gives an overall idea of the cleaner controller. The LEDS indicate the corresponding input signal from the sensor. The fan & drive motor are controlled by their respective contactors.

## HARDWARE DESCRIPTION

## **CHAPTER 4**

## HARDWARE DESCRIPTION

The prime use of microcontroller is to control the operation of a machine using a fixed program that is stored in ROM .

The 8051 microcontroller generic part number actually includes a whole family of microcontrollers that have numbers ranging from 8031 to 8751 and are available in an n-channel Metal Oxide Silicon (NMOS) and Complementary Metal Oxide Silicon (CMOS) construction in a variety of package types. As enhanced version of the 8051, the 8052 also exists with its own family of variations and even includes one member that can be programmed in BASIC.

Some members of 8051 family are given below.

|         |   |                 |   | RAM       |

|---------|---|-----------------|---|-----------|

| 8031    | _ | EPROM less      | - | 128bytes  |

| 8032    | - | EPROM less      | - | 256 bytes |

| 87C51   | - | with EPROM (4K) | - | 128 bytes |

| 0, 0, - |   | (window type)   |   |           |

| 87C52   | - | with EPROM (8K) | - | 256bytes  |

| 87C51   | - | with EPROM (4K) | - | 128 bytes |

|         |   | (flash memory)  |   | 00(1.4    |

| 89C52   | - | with EPROM (8K) | - | 256 bytes |

|         |   | (flash memory)  |   |           |

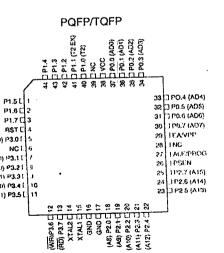

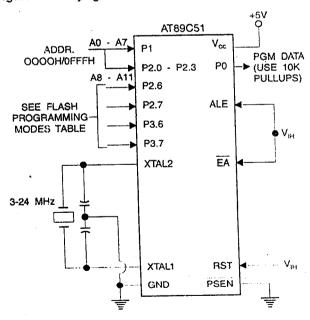

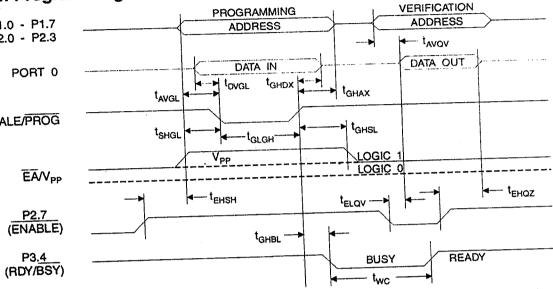

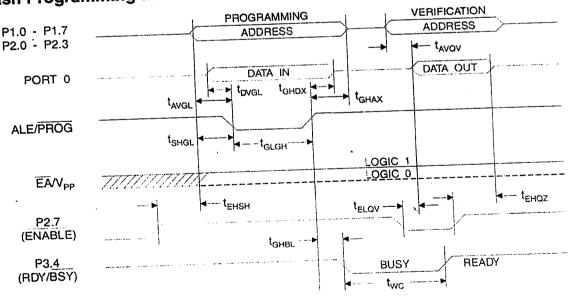

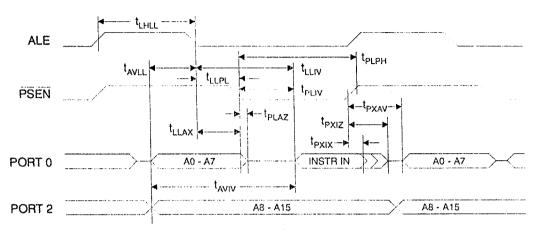

A member of the 8051 family AT89C2051, an 8-bit microcontroller with 2Kilobytes flash memory has been selected for this project.

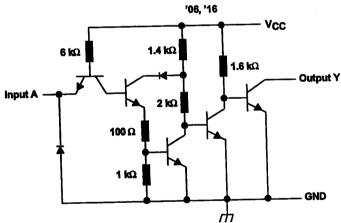

## 4.1 OPTOCOUPLER:

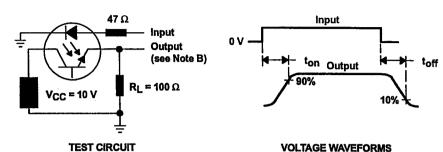

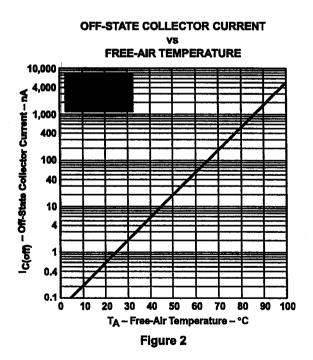

An opto coupler (also called as opto isolator or an optically coupled isolator) combines an LED and a photo transistor in a single package. This opto coupler is used as buffer for coupling the sensor outputs with microcontroller inputs.

This shows an LED driving a photo transistor. This is much more sensitive optocoupler than LED — photodiode. Any change in LED current, changes the current through the photo transistor. In turn, the change in the LED current produces a changing voltage across the Collector — Emitter terminals. Therefore, a signal voltage is coupled from the input circuit to the output circuit. The big advantage of an optocoupler is the electrical isolation, between the input and output circuits. With an optocoupler the only contact between the input and output is a beam of light. Because of this, it is possible to have an insulation resistance between the two circuits in the thousands of megaohms. Isolation like this comes handy in high voltage applications, where the potentials of the two circuits may differ by several thousand voltages.

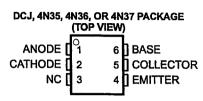

In this project, the buffer action is carried over by the optocoupler 4N35.

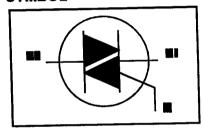

#### 4.2 TRIAC:

A triac is a device equivalent to an inverse parallel connected pair of SCRs, during turn – off, its behaviour is not so clear as SCR. The triac is a member of thyristor family.

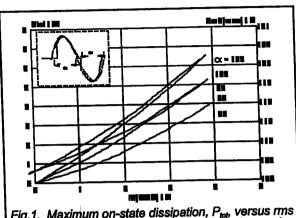

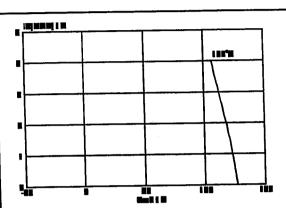

Fig 4.2 Triac

Triac has three terminals, G is the control terminal. The main terminal connected electrically to the envelope is called 'anode' by some manufacturers due to its resemblance with the anode lead of a reverse blocking triode thyristor.

The difference between the operation of a triac and reserve blocking triode thyristor is that triac can conduct when the terminal 2 is positive or negative with respect to T2. This conduction in either direction can be achieved with either gate positive or negative with respect to the main terminal (ie) T1.

## 4.2.1. ADVANTAGES OF TRIAC:

- > The triac needs a single heat sink of slightly larger size, but antiparallel thyristor pair needs two heat sinks of slightly smaller sizes but due to the clearance total space required is more for thyristors.

- > A triac needs a single fuse for protection, this also simplifies the construction. Triacs can be triggered with positive or negative polarity voltages.

- > In some DC applications SCR is required to be fitted with a parallel diode to protect against reverse voltage. A triac used may work without a diode as such breakdown in either direction is possible.

- > The triac is preferred due to its low cost and advantages.

The triac BT136 is used in this project, overhead cleaner controller.

#### 4.3. **MOTORS**:

Two types of motors used are,

- > Fan motor, which is an induction motor.

- > Drive motor, which is a stepper motor.

#### 4.3.1. FAN MOTOR:

The fan motor operates a fan for the sucking action. It gets started as soon as the START signal is given.

#### 4.3.2. DRIVE MOTOR:

The drive motor is responsible for the working of mobile unit. This motor can be used for both forward and reverse movements of the OHC, by changing polarity of supply. The driver motor gets started after a delay.

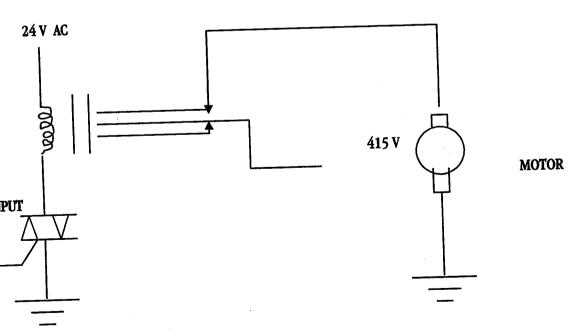

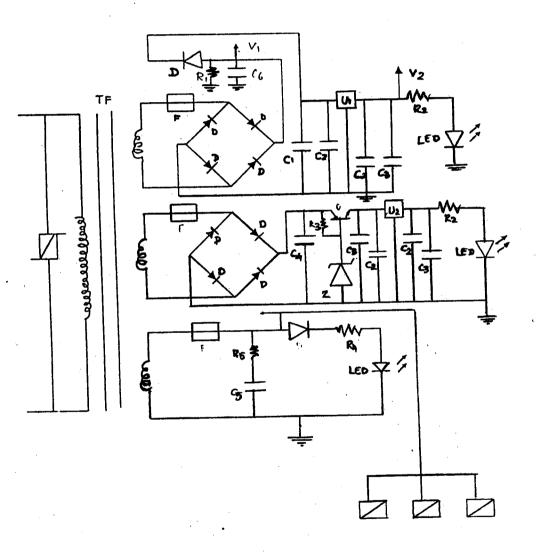

#### 4.4. POWER SUPPLY:

- > The OHCC receives its power supply from voltage regulators .

- > A multitapped transformer is used to provide the input for voltage regulator.

- > Since the microcontroller and the sensors, drivers, etc., working in different (5V or 24V) voltages, two supplies are provided.

- > To avoid overheating of the power components, heat sinks and pre regulator equipments are used.

- > To avoid harmonics or rather noise, capacitors are used at the inputs and the outputs of the regulator.

- > An I.C. combination filter can be used to filter out unwanted noise harmonics.

Fig 2.1 POWER SUPPLY

#### **CHAPTER 5**

## SYSTEM WORKING

- $\triangleright$  The power supply of +5V & +24V is given to the OHCC.

- > Now the OHCC is ready for operation .

- > The start signal is given to the controller using the push button switch.

- > The input signal is indicated by LEDs connected to the input port of the OHCC.

- > The start signal is thus sensed by microcontroller which in turn energizes the contactors K1 and K2 as programmed.

- > Now the microcontroller scans for the rest of the input signals.

- > The working of the OHCC for the other input signals can be explained as follows.

## 5.1. RESPONSE OF OHCC TO INPUT SIGNALS:

#### > OBSTACLE 1:

When the cleaner controller receives this signal from the sensor, it deenergizes the contactor K2 and energizes K3 after a preset delay.

#### > OBSTACLE 2:

When the cleaner controller receives this signal from the sensor, it deenergizes K3 and energizes K2 after a preset delay.

#### > AUTO REVERSE:

Two conditions are possible if auto reverse signal is received .

- If K2 is in 'on' condition and K3 is 'off'.

Under this condition, the cleaner controller de-energizes K2 and energizes K3.

- 2. If K3 is in 'on' condition and K2 is 'off'.

During this condition, the cleaner controller switches off K3 and energizes K2.

#### > DISCHARGE:

The two conditions to be considered in this case are,

- 1. When K2 is 'on' and K3 is 'off'.

During this condition, the cleaner controller de-energizes K2 and switches it 'on' after a preset delay.

- 2. When K3 is 'on' and K2 is 'off'.

Under this condition, the cleaner controller switches off K3 for a preset time and energizes K3 again after the delay.

#### > STOP:

When the cleaner controller receives this signal, it de – energizes the driver contactors followed by the fan contactor.

The OHCC works as explained above, until receives the stop signal.

Fig: 5.1. Eqvivalent relay circuits

#### 5.2. FIELD WORKING:

The working of cleaner controller can be very well understood when the OHC operations are studied.

- > As soon as the OHCC is energized, the fan motor of the cleaner gets started up followed by the forward drive motor.

- > The cleaner moves in the forward direction initially .

- > When an obstruction is sensed by the OHCC, the cleaner moves in the reverse direction to avoid the obstacle.

- > As the ends of the track are sensed by the controller, the cleaner automatically reverses it is direction, (i.e.) it stops for a preset time and automatically reverses it is direction.

- > When the discharge bag is sensed by the cleaner, it stops a preset delay and discharges the collected fluff and continues to travel in the same direction.

- $\triangleright$  The OHC stops when the *stop* switch is pressed .

Thus the OHC works according to the instructions given to the microcontroller of the OHCC.

LOGICAL CONTROL FLOW

## CHAPTER 6

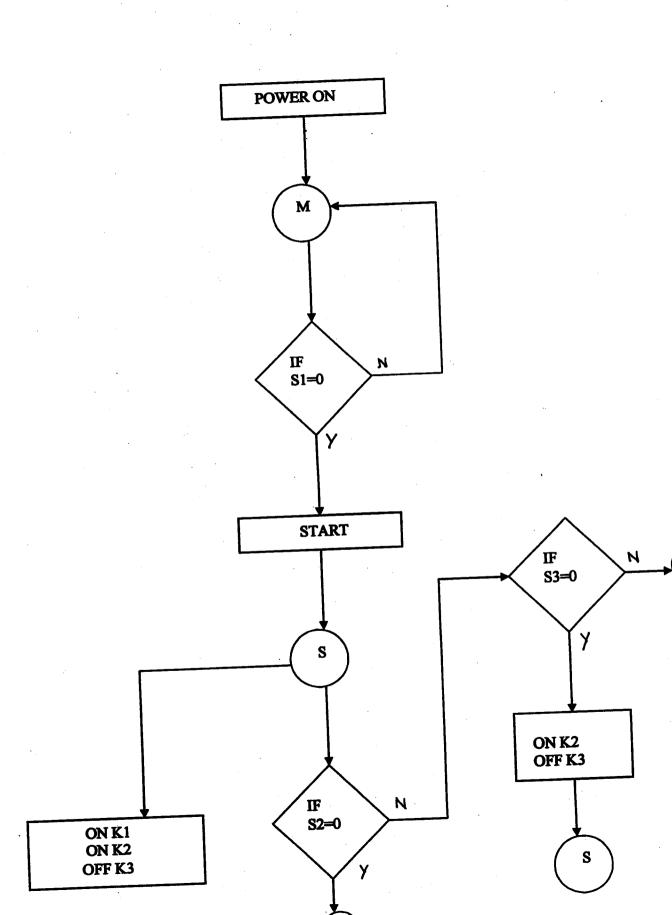

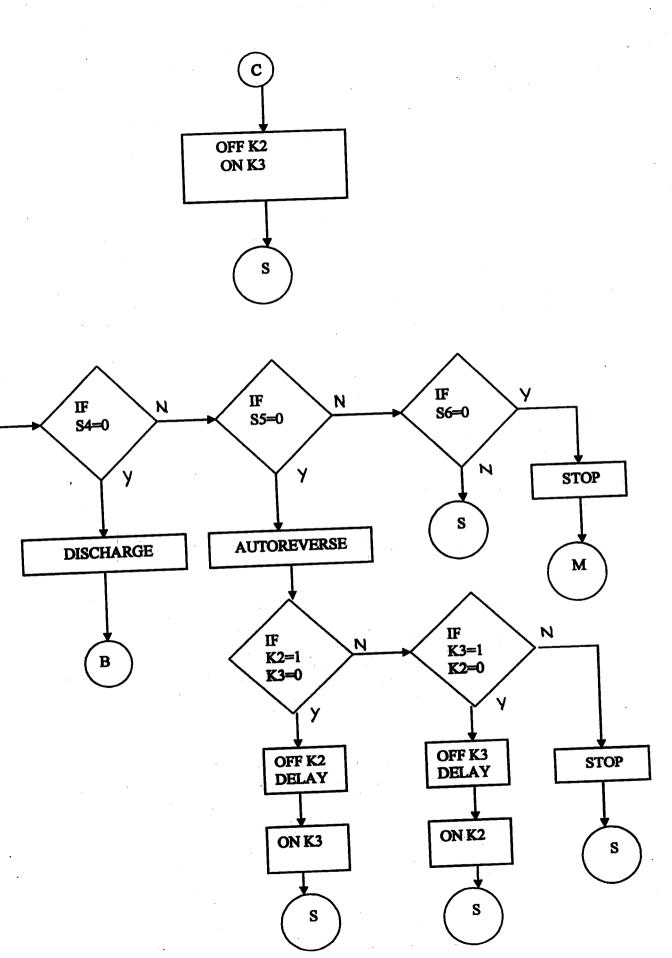

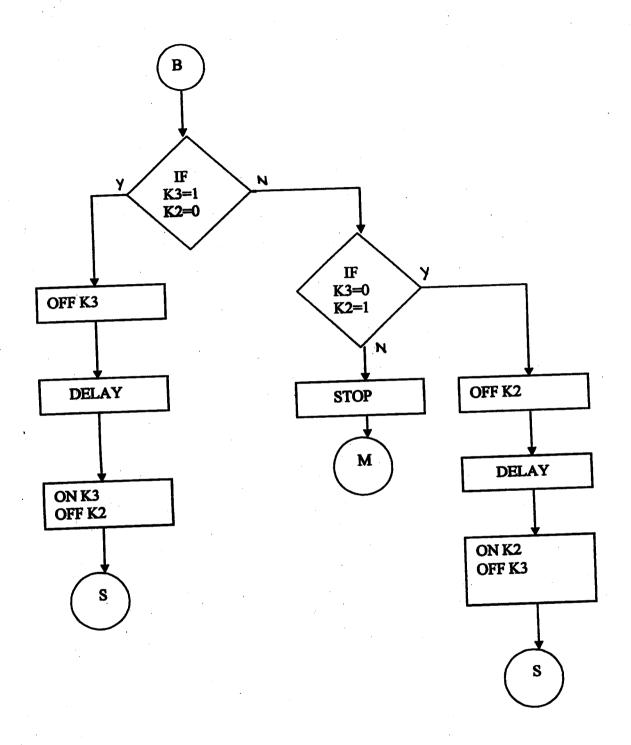

## LOGICAL CONTROL FLOW

Programming the microcontroller is the important task in this project. The instruction given to the microcontroller coordinates all the accessories connected to the controller.

### **Programming Steps:**

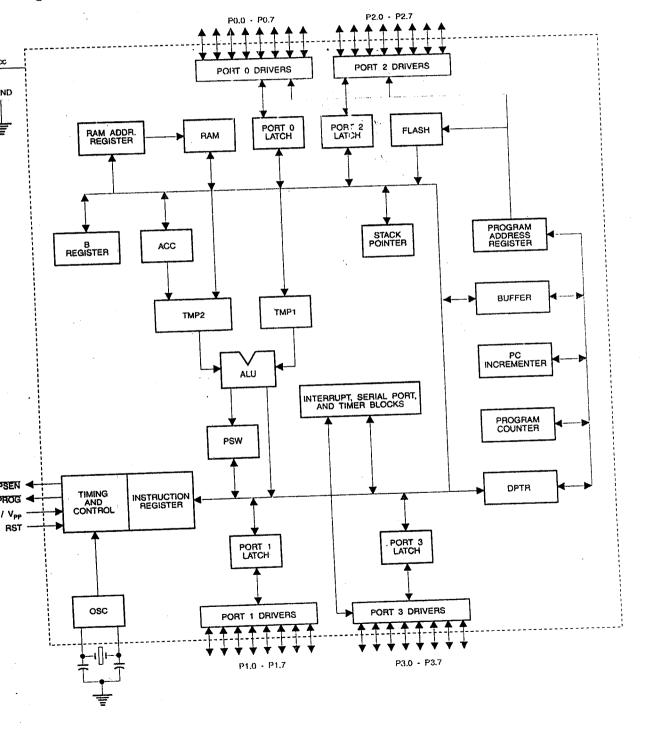

Both the ports of microcontroller (Port 1 & Port 3) are used in the project.

- Step 1: Port 1 bits are designed as input and port 3 bits function as output bits.

- Step 2: The main loop of the program checks for the start signal.

- Step 3:As the microcontroller finds the start bit of port 1 low, the corresponding bits of K1 & K2 (contactors) in port 3 are made low.

- Step 4: Now the microcontroller starts to scan the input bits to see if any input signal is received.

### Step 5:

- > If the input is OBSTACLE 1 then

- 1. K2 bit is made high (off).

- 2. A delay loop is executed.

- 3. K3 bit is made low (on) and control is returned to the main loop.

- > If the input is OBSTACLE 2 then

- 1. K3 bit is made high (off).

- 2. Delay loop is executed .

- 3. K2 bit is made low (on) and control is returned to the main loop.

## > If the input is AUTO REVERSE then

1. A check on K3, K2 bits is performed.

#### Condition 1:

If K2 bit is low and K3 bit is high then K2 is made high, followed by a delay loop execution and K3 is made low.

#### Condition 2:

If K3 bit is low and K2 bit is high then K3 is made high, followed by a delay loop execution and K2 is made low.

2. The control is returned to the main loop.

## > If the input is DISCHARGE then

1. A check on K2, K3 bits is performed.

#### Condition 1:

If K2 is low then K2 is made high and a delay loop is executed for preset number of times and K2 is again made low.

#### Condition 2:

If K3 is low then K3 is made high and delay loop is executed for a preset number of times and K3 is again made low.

2. Control is returned to the main loop.

- $\triangleright$  If the input is STOP then

- 1. K2 and K3 bits are made high followed by K1 after a preset delay.

- Step 6: The required subroutine is executed and the control again comes to the main loop.

- Step 7: This looping process continues until the microcontroller finds the stop bit of input port to be high .

# **COMPARATIVE STUDY**

#### **CHAPTER 7**

### **COMPARITIVE STUDY**

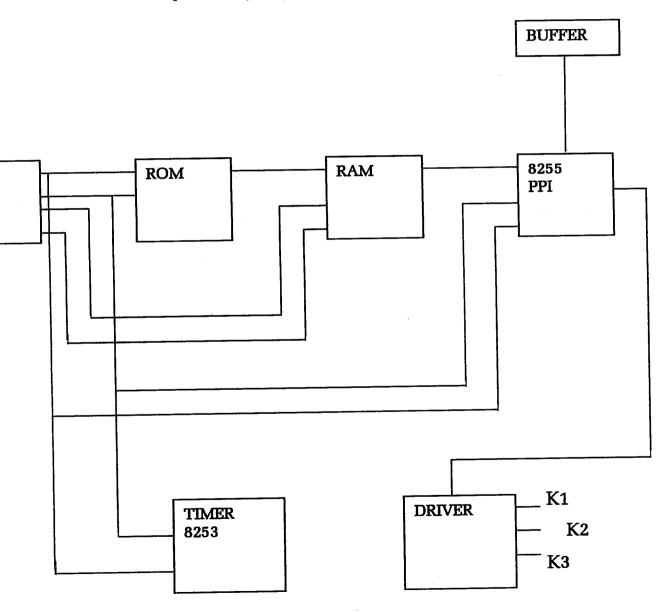

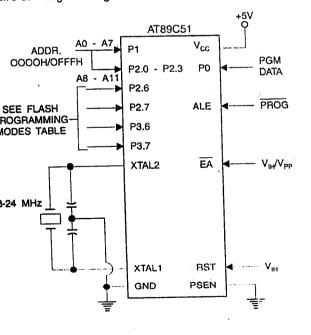

The reason for the usage of microcontroller instead of microprocessor can be best understood from a comparative study using block diagram .

Fig: 7.1.Implementation of OHCC using microprocessor

Fig: 7.2. Block diagram of OHCC using microcontroller

By referring to the above blocks it can be inferred that a microprocessor needs a number of external accessories when compared to a microcontroller and thus requiring a lot of space. Hence the cost of the system increases with a trade of in efficiency.

#### **CHAPTER 8**

#### FEATURES

### 8.1. SPECIAL FEATURES:

- The electronic circuit incorporates microcontroller for low power consumption and high reliability.

- Complete operational status of the electronic system is indicated in the LEDs resulting in easy maintenance and troubleshooting.

- > Inductive sensors enable non-contact reversal at the end of every cycle.

- > Push button switches on both sides of the system for start and stop make manual control possible.

## 8.2.OPTIONAL FEATURES:

- Dip switches can be used to select required program from a number of programs of microcontroller to make OHC perform a desired task.

- > Programmable timer adjustments can be provided for the reversing discharging etc.,

#### 8.3SAFETY:

- > Primary current supply through completely enclosed safety contact rails.

- > Power pack with the mechanical and electrical interlock contactors.

**CONCLUSION**

### CHAPTER 9

#### CONCLUSION

This project was designed and developed using micro controller AT89C2051 and was tested on 'the Cleaner test equipment'. It was found to be efficient and satisfactorily fulfilled the real time requirements without any case of hang over.

The newly developed system is applicable for all sorts of industrial environments and the micro controller can be programmed to include a number of other functions such as intelligent reversal, adjustable delay periods etc.

| NAME: Ramouri. N                                           |

|------------------------------------------------------------|

| ADDRESS : EMSTMAN FASHIONS                                 |

| COAKEADO, TIRUPUR-602                                      |

| RESPONDENT:                                                |

| Managing Director                                          |

| chief Executive                                            |

| Chief Engineer                                             |

| □ Manager                                                  |

| <ul><li>Others</li></ul>                                   |

| Exisiting cleaning system: ANS 220                         |

| Supplier details : ECG/ JACOB/                             |

| Expectation of customer for the product: Low maintainence, |

| Lost effective                                             |

| Rating of features of your product by customer             |

| <b>a</b> Quality                                           |

| n Savings                                                  |

| n Price                                                    |

| □ Warranty                                                 |

| Reliability                                                |

| NAME.       | : R. Ramosubramanian                                   |                                       |

|-------------|--------------------------------------------------------|---------------------------------------|

| ADDRESS     | : R. Ramasubramanian<br>: WC SHNA TEXTILES<br>DINDICUL |                                       |

| RESPONDE    | NT:                                                    |                                       |

| ٥           | Managing Director                                      |                                       |

|             | Chief Executive                                        |                                       |

|             | Chief Engineer                                         |                                       |

| £.          | Manager                                                |                                       |

| τ           | Others                                                 |                                       |

| Exisiting o | leaning system: Root haka                              |                                       |

| Supplier d  | etails :                                               |                                       |

| Expectation | n of customer for the product: Quality                 |                                       |

|             | Wer hierally                                           |                                       |

| Rating of   | features of your product by customer                   |                                       |

| <b>z</b> Qu | ality                                                  |                                       |

| o Sav       | vings                                                  |                                       |

| Pri         | ce                                                     |                                       |

| □ W         | arranty                                                |                                       |

| □ Re        | eliability                                             | R. Ramasubramanian<br>General Manager |

| NAME: G. Raveendran                             |

|-------------------------------------------------|

| ADDRESS: Alagendra Textiles Ltd,<br>Theni-1.    |

| RESPONDENT:                                     |

| □ Managing Director                             |

| □ Chief Executive                               |

| □ Chief Engineer                                |

| Manager (AUM)                                   |

| □ Others                                        |

| Exisiting cleaning system: Pricol XL250         |

| Supplier details: Prical, Coimbatore            |

| Expectation of customer for the product :       |

| - easy to operate -                             |

| Rating of features of your product by customer  |

| <ul> <li>Quality</li> </ul>                     |

| □ Savings                                       |

| u Price                                         |

| □ Warranty<br>G. Raveendran                     |

| Reliability  Asst. General Manager (Production) |

| NAME: S. Morrethachalam                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS: Variajan Terotiles limited                                                                                                   |

| NAME: S. Morrethachalam  ADDRESS: Variage Testiles limited  Thrigher. 628                                                             |

|                                                                                                                                       |

| RESPONDENT:                                                                                                                           |

| Managing Director (VP)                                                                                                                |

| Chief Executive                                                                                                                       |

| Chief Engineer                                                                                                                        |

| Manager                                                                                                                               |

| Others                                                                                                                                |

| Exisiting cleaning system:                                                                                                            |

| Supplier details :                                                                                                                    |

| Exisiting cleaning system: slogi jacobi  Supplier details: Jenerineer, combatane  Expectation of customer for the product: automatic. |

| - law priced                                                                                                                          |

| Rating of features of your product by customer                                                                                        |

| Quality                                                                                                                               |

| Savings                                                                                                                               |

| Price                                                                                                                                 |

| Warranty                                                                                                                              |

| Reliability  Sathguru Maruthachalas  Vice President                                                                                   |

Kurichikara Post, Thrissur - 680 028.

Phones: 0487-695521, 695606,

| NAME: Chellan. S.  ADDRESS: N/S Sivasubrama  Ravipuram. 7-K. | niam Spinning Mills (P) Ltd.          |

|--------------------------------------------------------------|---------------------------------------|

| RESPONDENT:                                                  |                                       |

| <ul> <li>Managing Director</li> </ul>                        |                                       |

| <ul> <li>Chief Executive</li> </ul>                          |                                       |

| a Chief Engineer                                             |                                       |

| <ul> <li>Manager</li> </ul>                                  |                                       |

| Others (GM)                                                  |                                       |

| Exisiting cleaning system :                                  |                                       |

| Supplier details :                                           |                                       |

| Expectation of customer for the pro-                         | duct: <u>law cost</u> and             |

| easy maintainence                                            |                                       |

| Rating of features of your product                           | by customer                           |

| <b>Quality</b>                                               |                                       |

| □ Savings                                                    |                                       |

| Price                                                        |                                       |

| <ul> <li>Warranty</li> </ul>                                 | S. Chellam, M.Teca<br>General Manager |

| n Reliability                                                |                                       |

|                                                              | Sivasubramaniam Spinning Mills        |

Private Limited

| NAME: NallaThambi P.                                                       |                                              |

|----------------------------------------------------------------------------|----------------------------------------------|

| ADDRESS: KK.P. Textules Ud,                                                |                                              |

| Nanakkal-002                                                               |                                              |

| RESPONDENT:                                                                |                                              |

| Managing Director                                                          |                                              |

| □ Chief Executive                                                          |                                              |

| Chief Engineer                                                             |                                              |

| □ Manager                                                                  |                                              |

| □ Others                                                                   |                                              |

| Exisiting cleaning system: Rect, Vescil pl  Supplier details: Kort, madras | us                                           |

|                                                                            |                                              |

| Expectation of customer for the product: 1000 mount                        | tainone                                      |

| and reliability                                                            |                                              |

| Rating of features of your product by customer                             |                                              |

| <ul><li>Quality</li></ul>                                                  |                                              |

| <ul><li>Savings</li></ul>                                                  |                                              |

| Price                                                                      |                                              |

| <ul><li>Warranty</li></ul>                                                 |                                              |

| Reliability KKP                                                            | P. Nallathambi B.Com.,<br>Managing Director. |

Managing Director.

| NAME: MSambandam                                                                |

|---------------------------------------------------------------------------------|

| ADDRESS: TTK Textuley (td) (SD) Madras.                                         |

| RESPONDENT:                                                                     |

| □ Managing Director                                                             |

| Chief Executive                                                                 |

| Chief Engineer                                                                  |

| □ Manager                                                                       |

| <ul><li>Others</li></ul>                                                        |

| Exisiting cleaning system: Stoken, Flori Jarobil  Supplier details: R.K. Amadan |

| Supplier details : R.K. Amcicutes, Wachan                                       |

| Expectation of customer for the product:                                        |

|                                                                                 |

| Rating of features of your product by customer                                  |

| Quality                                                                         |

| □ Savings                                                                       |

| w Price                                                                         |

| <ul> <li>Warranty</li> </ul>                                                    |

| Reliability  M. Sambandam  B.Sc., B.Sc., (Tech.), M.B.A., F.I.E.                |

TTK TEXTILES LTD. SPINNING DIVISION

Price

Reliability

| NAME: T. K. Guncusekaran                       |

|------------------------------------------------|

| ADDRESS: MS Prime Textiles Utcl                |

| Tivapar-603                                    |

| RESPONDENT:                                    |

| □ Managing Director                            |

| chief Executive                                |

| Chief Engineer                                 |

| □ Manager                                      |

| Others (GM)                                    |

| Exisiting cleaning system: Egi-Jacobi          |

| Supplier details :                             |

| Expectation of customer for the product:       |

|                                                |

| Rating of features of your product by customer |

| <ul> <li>Quality</li> </ul>                    |

| n Savings                                      |

| NAME : SUBRAMANIAN, S.C.                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS : SRI AMBAL TEMPLES,                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Courapre -02g                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESPONDENT:                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| □ Managing Director                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chief Executive                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| chief Engineer                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Manager                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul><li>Others</li></ul>                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Exisiting cleaning system:                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Supplier details :                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Expectation of customer for the product: Rice, covice |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rating of features of your product by customer        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |