# AUTOMATED ACCIDENT IDENTIFICATION SYSTEM

P-903

**Project Report**

Submitted by

Bhavna. M Gokila Priya.D Arun Kumar.S Naveed.N

Guided by

Mr. T. Vijayakumar, M.E., Lecturer, Department of EEE.

In partial fulfillment of the requirement for the award of Degree of BACHELOR OF ENGINEERING in ELECTRICAL AND ELECTRONICS ENGINEERING

Department of Electrical and Electronics Engineering

Kumaraguru College of Technology

Coimbatore – 641006.

## DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

## Kum araguru College of Technology

#### COIMBATORE-641006.

## **CERTIFICATE**

This is to certify that the project

## AUTOMATED ACCIDENT IDENTIFICATION SYSTEM

Has been submitted by

| 1. Bhavna.M       | <b>99EEE12</b> |

|-------------------|----------------|

| 2. Gokila Priya.D | <b>99EEE16</b> |

| 3. Arun Kumar. S  | 99EEE07        |

| 4. Naveed.N       | <b>99EEE32</b> |

In partial fulfillment of the requirements for the award of degree of Bachelor of Engineering in Electrical and Electronics Engineering branch of the Bharathiar University, Coimbatore – 641006 during the academic year 2002 - 2003.

Guide 1913/03

Professor and Head

Certified that the candidates mentioned above were examined in project work viva-voce held on 20-03-2003

Internal Evaminer

External Examiner

## **ACKNOWLEDGEMENT**

With deep sense of gratitude we express our heartfelt thanks to our guide Mr.T.Vijayakumar, M.E., Lecturer in EEE for his guidance, valuable suggestions and constant interest evinced by him throughout the course of the project work.

We are very much indebted to our Head of the Department Dr. T. M. Kameswaran, B.E., M.Sc., (Engg.), Ph.D., MISTE, Sr.M.I.E.E.E., FIE, for the encouragement and guidance he has given us. We are highly grateful to both our assistant professors, Mr.V.Duraisamy, M.E., MISTE, AMIE, MSSI, M.I.E.E.E. and Mr.K.Rajan, M.E., MISTE., for their remarkable support.

Our sincere thanks is due to our principal Dr.K.K. Padmanabhan, B.Sc (Engg.), M. Tech., Ph. D., M.I.S.T.E., F.I.E. for having made available all the facilities to do this project.

We have no words to express our profound gratitude to our class advisor Mrs.R.Mahalakshmi, M.E. for her valuable help in doing the project.

We are indebted to the support, encouragement and help rendered by all the faculty members and non-teaching staff of EEE Department.

Last but not the least we thank our dear friends for helping us a lot with their innovative ideas.

## **SYNOPSIS**

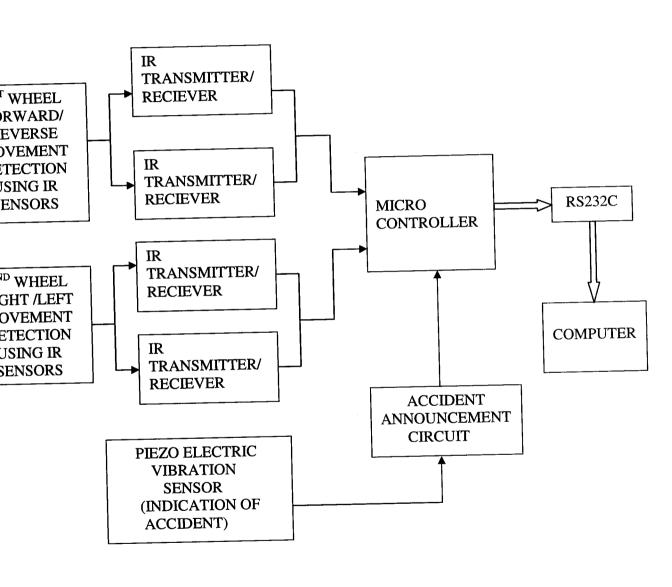

The never-ending saga of accidents happening due to vehicles in India has led to the inevitable loss of life and property. The number of vehicles on road is increasing very rapidly and the numbers of accidents are also on the rise. Though, the requirements of safety is more, we can very much prevent the loss of life by knowing where exactly the accident has occurred so that we can get the injured to the hospital for treatment without any time delay. The project that we are presenting is a miniature model of how the location of the vehicles can be determined using infrared sensors.

Our project compromises these situations and provides suitable identification of any vehicle, which has met with an accident, and its location of accident with precision. The time at which the accident has taken place can also be determined. Incase an accident takes place here simulated by tapping the piezoelectric sensor; the signals given to the micro controller are sent to the PC via RS232C which can be monitored and thereby being able to provide the critical help required under such dire circumstances.

| DEDICATED TO OUR BELOVED PARENTS AND FRIENDS FOR THEIR ENCOURAGEMENT AND SUPPORT. |  |

|-----------------------------------------------------------------------------------|--|

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

## **CONTENTS**

| Chapter                            | Page no. |

|------------------------------------|----------|

| CERTIFICATE                        |          |

| ACKNOWLEDGEMENT                    |          |

| SYNOPSIS                           |          |

| CHAPTER 1                          | 1        |

| 1.1 INTRODUCTION                   | 2        |

| 1.2 NEED FOR THE PROJECT           | 3        |

| CHAPTER 2                          | 5        |

| 2.1 MICRO CONTROLLER BLOCK DIAGRAM | 6        |

| 2.2 HARDWARE DETAILS               | 7        |

| 2.3 FUNCTIONAL ASPECTS             | 25       |

| CHAPTER 3                          | 26       |

| 3.1 MAIN BLOCK DIAGRAM             | 27       |

| 3.2 OVERALL OPERATION              | 28       |

| CHAPTER 4                          | 30       |

| 4.1 HARDWARE DESCRIPTION           | 31       |

| 4.2 INFRARED CIRCUIT               | 32       |

| 4.3 PIEZOELECTRIC SENSOR           | 38       |

| 4.4 ACCIDENT ANNOUNCEMENT CIRCUIT | 40 |

|-----------------------------------|----|

| 4.5 POWER SUPPLY BOARD            | 44 |

| CHAPTER 5                         | 47 |

| 5.1 NEED FOR RS232                | 48 |

| 5.2 HARDWARE DETAILS              | 50 |

| 5.3 FUNCTIONAL ASPECTS            | 53 |

| CHAPTER 6                         | 55 |

| 6.1 MICRO CONTROLLER CODING       | 56 |

| 6.2 C PROGRAM                     | 70 |

| CONCLUSION                        | 80 |

| OUTPUT                            | 83 |

| REFERENCES                        | 84 |

| APPENDIX                          | 86 |

## **CHAPTER 1**

## 1.1 INTRODUCTION

Our project titled Automated Accident Identification System aims at providing a solution to reduce the number of lives lost due to accidents going unnoticed. The vehicle may be a two-wheeler or four-wheeler with a battery connection. The vehicle is simulated by means of two wheels with infrared sensors fixed on either side to monitor direction of movement of the vehicle. The direction is continuously fed into the micro controller and that will be transmitted to PC through digital modulation techniques. Also a vibration sensor is fixed and depending on the amplitude of vibrations an alarm will be set off. On the PC the location of the vehicle can be tracked based on the data being transmitted from the micro controller.

The micro controller that we are using is AT89C51. It is manufactured by ATMEL INC., USA. This micro controller is an advanced version of INTEL8051 micro controller. The advantage of using this micro controller is that it is cost effective, has low power consumption and a 4K flash memory.

## 1.2 NEED FOR THIS PROJECT

The rise in number of vehicles on the road nears 12.5% annually and human population is also steadily increasing. Life has become a race against time without even realizing it. All these factors have lead to a drastic increase in the number of life threatening accidents thereby worsening the complications when lives are at stake. It was also analyzed that most of the people killed in such fatal accidents died before they received any basic medical treatment the main reason being the problem of identifying where exactly the accident has occurred and the time delay in taking the patient to the hospital.

#### STATISTICS TABLE

| Nature    | During 1997,  | During 1998   | During 1999   | During 2000 | During 2001 |  |

|-----------|---------------|---------------|---------------|-------------|-------------|--|

| of        | Number of     | Number of     | Number of     | Number of   | Number of   |  |

| Accidents | accidents and | accidents and | accidents and | accidents   | accidents   |  |

| :         | people        | people        | people        | and people  | and people  |  |

|           | involved      | involved      | involved      | involved    | involved    |  |

| Fatal     | 7947, 8756    | 8510,9801     | 8734, 9653    | 8269, 9300  | 8579,9571   |  |

| Grievous  | 4542, 6557    | 6562, 8525    | 5276, 7287    | 5278, 8496  | 5442, 8354  |  |

| Non       | 8352          | 789           | 6845          | 6239        | 6994        |  |

| Injured   |               |               |               |             |             |  |

A survey done by Government of TamilNadu State Transport Authority has been shown above. It has realized some harsh facts. Thereby this project aims at reducing the number of fatalities involved if not the number of accidents. Our project will not only allow the personals to know whether the accident has occurred or not but also the exact location of where the accident has occurred. For this we have done Automated Accident Identification System.

## **CHAPTER 2**

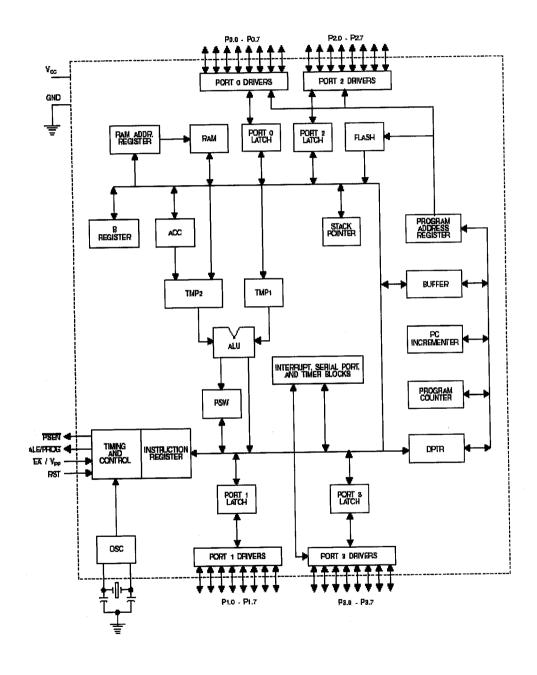

## 2.1 MICRO CONTROLLER BLOCK DIAGRAM:

## 2.2 HARDWARE DETAILS

The AT89C51 is a low power, high performance CMOS 8 bit microcomputer with 4k bytes of flash programmable and erasable read only memory (PEROM). The device has been manufactured using Atmel's high density, nonvolatile memory technology and is compatible with the industry standard MCS- 51 instruction set and pin out. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional non-volatile memory programmer. By combining an 8-bit CPU with Flash on a monolithic chip the Atmel AT89C51 is a powerful microcomputer, which provides a highly flexible and cost-effective solution to many embedded control applications.

## SALIENT FEATURES:

- 1. 8- bit CPU optimized for control applications.

- 2. Extensive Boolean processing capabilities.

- 3. 64 k program memory address space.

- 4. 64 k program memory data space.

- 5. 4 k bytes of on-chip program memory.

- 6. 128 bytes of on-chip data RAM.

- 7. 32 bi-directional and individually addressable input/output lines.

- 8. Two sixteen bit timers/counters.

- 9. Full duplex UART.

- 10. 6- source/5- vector interrupt structure with two priority levels.

- 11. On- chip clock oscillator.

## MEMORY ORGANISATION:

The AT89C51 has separate program and data memory. There are two types of memories available. One is read only memory (ROM) type where in you can only read the data's stored in it. Another type is Read Write memory or Random Access Memory (RAM). The program memory can only be read and not written into. The read strobe for external program memory is the PSEN (Program Store Enable). The data memory allows up to 64 k bytes of external RAM to be addressed. The CPU generates RD and WR signals as needed during external data memory access.

## ACCESSING EXTERNAL MEMORY:

For fetching from the external program memory 16 I/O lines (port 0 and port 2) are dedicated for bus functions. The address size for accessing the program memory is 16-bit and for accessing the data memory

it can be either16-bit or 8-bit depending on the instruction being used. The external memory program is accessed under two conditions:

- 1. When the EA (active low) is active.

- 2. When the program counter contains a number larger than 0FFFH Port 0 provides the lower order 8 bits of the address and Port 2 provides the higher order 8 bits.

## PORT 0:

It is an 8-bit open drain bi-directional I/O port. As an output port, each pin can sink 8 TTL inputs. If 1's are written to port 0 pin, the pin can be used as high impedance inputs. Port 0 can also be configured to act as a lower order data/address bus during access to external program and data memory. It also receives the code bytes during programming and outputs the code bytes during verification.

## PORT 1:

Port 1 is an 8-bit bi-directional I/O port with internal pull-ups.

The port 1 output buffer can sink /source four TTL inputs. When 1's are written to port 1 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally being pulled low

will provide source current (Iii) because of internal pull-ups. Port 1 also receives the lower order bytes during flash programming and verification.

## PORT 2:

It is an 8-bit bi-directional I/O port with internal pull-ups. If 1's are written to port 2 they can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current (I il) because of the internal pull-ups. Port 2 emits the higher order address byte during fetch cycle from external program memory and during accessing from external data memory that also use 16 bit addresses. Port 2 also receives the higher order address bits and some control signals during flash programming and verification.

## PORT 3:

It is an 8-bit bi-directional I/O port with internal pull-ups. The port 3-output buffer can sink four TTL inputs. When 1's are written to port 3 pins they are pulled high by the internal pull-ups and can be used as inputs. Special functions of Port 3 pins:

P3.0- RXD (Serial input port)

P3.1- TXD (Serial output port)

P3.2- INTO (Active low pin – External interrupt 0)

P3.3- INT1 (Active low pin – External interrupt 1)

P3.4- T0 (Timer 0 external input)

P3.5- T1 (Timer 1 external input)

P3.6- WR (active low)

P3.7- RD (active low)

## RST:

Reset Input. A high on this pin for two machine cycles while the oscillator is running will reset the device.

## ALE/PROG:

Address Latch Enable output pulse for latching the lower byte of the address during accesses to external memory. This pin is also the program pulse input during flash programming. In normal operation ALE is emitted at a constant rate of 1/6<sup>th</sup> the oscillator frequency, and may also be used for external timing or clocking purpose. If desired, ALE operations can be disabled by setting bit 0 of SFR location 8Eh. With the bit set ALE is active only during MOV X instruction.

## PSEN:

Program Store Enable is the read strobe to external program memory. While AT89C51 is executing code from external program memory, this pin is activated twice each machine cycle, except that two such activations are skipped during each access to external data memory.

## EA/VPP:

External Access Enable. It must be strapped to GND in order to enable the device to fetch code from external program memory locations starting from 0000H to FFFFH. EA should be strapped to Vcc for internal program executions.

The AT89C51 also contains a number of special function registers. They are

## ACCUMULATOR:

This a main register all data transfer instructions are carried out using this register. Data can be written and stored into the accumulator. It is a multipurpose register.

## **B REGISTER:**

The B register is used during multiply and divide operations. For other instructions it can be used as a scratch pad register. The B register is used in most of the instructions and has almost equal importance.

## PROGRAM STATUS WORD REGISTER:

This register contains program status information. It is an 8-bit register containing the following bits.

| CY    | AC | F0 | RS1 | RS0 | OV | - | P     |

|-------|----|----|-----|-----|----|---|-------|

| (MSB) |    |    | 1   |     |    |   | (LSB) |

CY - Carry Flag

AC - Auxillary Carry

F0 - Available to the user for general purposes

RS1 - Register bank control bits 1 and 0

RS0 - Set/cleared by software to determine working register bank

OV - Overflow Flag

- - User defined flag

P- Parity Flag

#### STACK POINTER:

The stack pointer register is 8-bit wide. It is incremented before data is stored during PUSH and CALL instructions. The stack can reside at point in the RAM. The stack pointer is initialized to 07H.

#### DATA POINTER:

The data pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its function is to hold a 16-bit address. It maybe manipulated as a 16-bit register or as two 8-bit registers.

## SERIAL DATA BUFFER:

The serial data buffer actually consists of two seperate registers a receive buffer and a transmit buffer register. When data is moved to SBUF, it goes to the transmit buffer, where it is held for serial transmission. When data is moved from the SBUF it is from the receive buffer.

## **CONTROL REGISTERS:**

There are a number of special function registers like TCON,

TMOD, SCON, IE, IP etc. These registers contain control and status bits for

the interrupt system, timers/counters and serial port.

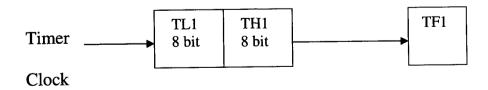

## TIMER REGISTERS:

Register pairs TH0 and TH1 & TL0 and TL1 are the 16-bit counter registers for the timers/counters 0 and 1 respectively.

## TIMERS/COUNTERS:

The AT89C51 has two 16 bit timer/counter registers for Timer 0 and Timer1. They can be configured to work either as a timer or as a counter. As a timer the register is incremented every machine cycle. Thus the register counts machine cycles. Each machine cycle consists of 12 oscillator periods; the count rate is 1/12 of the oscillator frequency. As a counter the register increments if there is a 1 to 0 transition in its corresponding external input pin T0 and T1. There are no restrictions on the duty cycle of the external input signal but it should be held for at least one machine cycle to ensure that a given level is sampled at least once before it changes. Timer0 and Timer1 have four operating modes (13-bit timer, 16-bit timer, 8-bit auto-reload and split timer). The four modes are,

## MODE 0:

Both the timers in mode 0 are 8-bit counters with a divide by 32 prescaler. The timer register acts as a 13-bit register. As the count rolls from

all 1's to 0's, it sets the timer interrupt flag TF1. The counted input is enabled to the timer when TR1=1 and GATE=0 or INT1=1. The 13bit registers consists of all 8 bits of TH1 and lower 5 bits of TL1. Setting the run flag TR1 does not clear the registers. Mode 0 operation is the same for Timer1 and Timer0. There are two different gate bits one for Timer1 and the other for Timer0.

## MODE 1:

Mode 1 is the same as Mode 0 except that here all the 16 bits are used. The clock is applied to the combined high and low timer registers (TL1 and TH1). As clock pulses are received the timer counts up 0000H, 0001H etc. An overflow occurs on the FFFFH to 0000H flag. The timer continues to count.

## MODE 2:

Mode 2 configures the Timer register as an 8-bit counter with automatic reload. Overflow from TL1 not only sets TF1, but also reloads

TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged. Mode 2 operation is the same for Timer/Counter 0.

## TCON REGISTER:

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     |     |     |

TF1- Timer 1 overflow flag

TR1- Timer 1 run control bit

TF0- Timer 0 overflow flag

TR0- Timer 0 run control bit

IE1- Interrupt 1 edge flag

IT1- Interrupt 1 type control bit

IEO- Interrupt 0 edge flag

ITO- Interrupt 0 type control bit

## MODE 3:

Timer1 in mode 3 simply holds its count. The effect is the same as setting TR1=0. Timer 0 in mode 3 establishes TL0 and TH0 as two separate counters. TL0 uses the Timer0 control bits. TH0 is locked into Timer function (counting machine cycles) over the use of TR1 and TF1 from

Timer1. TH0 now controls the Timer1 interrupt. With Timer0 in mode 3 in AT89C51 can appear to have three Timer/Counters. When Timer0 is in mode3, Timer1 can be turned on and off by switching it out of and into its own mode3. In this case, the serial port as a baud rate generator or in any application not requiring an interrupt can still use Timer1.

## TMOD REGISTER:

MSB

LSB

| Gate | C/T  | M1  | M0 | Gate   | C/T | M1 | M0 |

|------|------|-----|----|--------|-----|----|----|

|      | TIME | ER1 |    | TIMER0 |     |    |    |

Gate-gating control when set Timer/Counter X is enabled only while INT X pin is high and TRX control pin is set. When cleared, Timer X is enabled whenever TRX control bit is set.

C/T (T being active low)-Timer or Counter selector cleared for Timer operation (input from internal system clock). Set for Counter operation (input from TX input pin).

M1-mode bit 1

M0-mode bit 0

#### **SERIAL INTERFACE:**

The serial port is full duplex which means it can transmit and receive simultaneously. It is also receive-buffer which means it can begin receiving a second byte before a previously received byte is read. Writing to SBUF loads the transmit register and reading the SBUF accesses the physically separate receive register. It operates in four modes,

## MODE 0:

Serial data enters and exits through RXD. TXD outputs the shift clock. Eight data bits are transmitted/received, with the LSB first. The baud rate is fixed at 1/12 of the oscillator frequency.

#### MODE1:

10 bits are transmitted through TXD or received through RXD.

A start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive; the stop bit goes RB8 in special function register SCON. The baud rate is variable.

## MODE 2:

Here 11 bits are transmitted through TXD and received through RXD; a start bit (0), 8 data bits (LSB first) a programmable ninth data bit

(TB8 in SCON) can be assigned the value of 0 or 1. For example the parity bit can be moved into TB8. On receive the ninth data bit goes into RB8 in Special Function Register SCON, while the stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 of the oscillator frequency.

## MODE 3:

RXD); a start bit (0), 8 data bits (LSB first), a programmable ninth data bit and a stop bit (1). In fact, mode 3 is the same as mode 2 in all respects except baud rate, which is variable in mode 3. In all four modes transmission is initiated by an instruction that uses SBUF as a destination register. Reception is initiated in mode 0 by the condition R1=0 and REN=1.Reception is initiated in the other modes by incoming start bit if REN=1.

## SERIAL PORT CONTROL REGISTER:

|                          |      |       |     |     |     | TI | DI     |

|--------------------------|------|-------|-----|-----|-----|----|--------|

| SM0                      | SM1  | SM2   | REN | TB8 | RB8 | TI | RI     |

| SIVIO                    | Sivi | 31112 |     |     |     |    | 1      |

| _                        |      |       |     |     |     |    | (I CD) |

| (MSB)                    |      |       |     |     |     |    | (LSB)  |

| $(\mathbf{M}\mathbf{M})$ |      |       |     |     |     |    |        |

\_ \_

SM0- Serial port mode bit 0

SM1- Serial port mode bit 1

SM2- Enables the multiprocessor communication in modes 2 and 3. In mode 2 or 3 if SM2 is set to 1 then R1 will not be activated if the received 9<sup>th</sup> data bit RB8 is 0. In mode1 if SM2 = 1, then R1 will not be activated if valid stop bit was not received. In mode 0 SM2 should be zero.

REN- Enable serial reception. Set by software to enable reception and cleared by software to disable reception.

TB8- The 9<sup>th</sup> data bit that will be transmitted in modes 2 and 3. Set or cleared by the software.

RB8- In modes 2 and 3 the 9<sup>th</sup> data bit that was received. In mode 1 if SM2=0, RB8 is the stop bit that was received in mode 0.

TI- Transmit Interrupt flag. Set by hardware at the end of the 8<sup>th</sup> bit time in mode 0 or at the beginning of the stop bits in the other modes, in any serial transmission.

RI- Receive Interrupt flag. Set by hardware at the end of the 8<sup>th</sup> bit time in mode 0 or halfway through the stop bit time in the other modes in any serial reception.

## **INTERRUPTS:**

The AT89C51 provides five interrupt sources, two external interrupts, two timer interrupts and a serial port interrupt. The external interrupts INTO and INT1 can each be either level activated or transition activated, depending on bits ITO and IT1 in register TCON. The flag that actually generates these interrupts are the IEO and IE1 bits in TCON. When the service routine is vectored hardware clears the flag that generated the external interrupt only if the interrupt was transition activated.

The Timer0 and the Timer1 interrupts are generated by TF0 and TF1 which are set by a roll over in their respective Timer or Counter register. When a Timer interrupt is generated, the on-chip hardware clears the flag that generated it when the service routine is vectored.

The logical OR of RI and TI generate the serial port interrupt.

Neither of these flags is cleared by hardware when the service routine is vectored. In fact the service routine must normally determine whether RI or TI generated the interrupt, and the bit must be cleared in software.

## INTERRUPT ENABLE REGISTER (IE):

(MSB)

| EA | <br>ET2 | ES | ET1 | EX1 | ET0 | EX0 |

|----|---------|----|-----|-----|-----|-----|

|    |         |    |     |     |     |     |

(LSB)

## EA - Global Enable/Disable

-Undefined/ Reserved

ET2-Timer2 interrupt enable bit

ES -Serial port interrupt enable bit

ET1-Timer1 interrupt enable bit

EX1-External interrupt 1 enable bit

ET0-Timer 0 interrupt enable bit

EX0-External interrupt 0 enable bit.

## INTERRUPT PRIORITY REGISTER (IP):

(MSB) (LSB)

| <br> | PT2 | PS | PT1 | PX1 | PT0 | PX0 |

|------|-----|----|-----|-----|-----|-----|

|      |     |    |     |     |     |     |

- -Reserved

- -Reserved

- PT2 -Timer 2 interrupt priority bit

- PS -Serial port interrupts priority bit

- PT1 -Timer 1 interrupt priority bit

- PX1 -External interrupt 1 priority bit

- PT0 -Timer 0 interrupt priority bit

- PX0 External interrupt 0 priority bit

## 2.3 FUNCTIONAL ASPECTS:

The micro controller receives the various data from the IR sensors and the vibration sensor (piezo electric plate). The data concerning the direction of rotation of the wheels is given to the port pins P1.0 (Right), P1.1 (Left), P1.2 (Reverse) and P1.3 (Forward). The signal from the vibration sensor is given to the interrupt pin P3.2 (INTO). The port pins P3.0 and P3.1 are used for interfacing with RS-232-C. A crystal clock is connected to pins 18 (XTAL2) and 19(XTAL1) of the IC AT89C51.

# **CHAPTER 3**

# 3.1 MAIN BLOCK DIAGRAM

. . .

# 3.2 OVERALL DESCRIPTION

Our project titled Automated Accident Identification System provides a means of detecting and determining the location of any accident involving vehicles. Since there are practical difficulties in using an actual vehicle to present our idea we have made use of two wheels to simulate the required effect.

Infrared sensors are placed on either side of the wheels for detection of movement. When the wheels are made to rotate due to the hatching made on the wheel surface the following logical combinations of 0 0, 1 0,1 1, 0 1. This logic is obtained as a result of the hatching, which is in black and white. So when a black comes in between the sensors logic 0 is obtained and a white causes logic 1. Four sensors are made use of here and four directions can be determined forward, reverse, right and left. The signals obtained from the IR sensors are sent to the IR transmitter and receiver circuits which process the signals by comparing it to a particular threshold level and switching it to 5 V thus the relevant data is obtained. Based on these data's the direction of movement of the vehicle can be ascertained. These data's are continuously being sent to the micro controller through the port pins.

Forward logic - 0 0, 1 0, 1 1, 0 1

Reverse logic - 0.0, 0.1, 1.1, 1.0

Right logic - 00, 10, 11, 01

Left logic - 0 0, 0 1, 1 1, 1 0

Generally any sudden jerks will cause an abrupt increase in vibrations this concept is made use of here. A piezoelectric plate is made use of here. By tapping the vibration sensor (piezo electric plate) an accident can be simulated. The signal obtained from the piezoelectric plate is sent to the accident announcement circuit where the signal is amplified and compared. If the signal is above a particular level then indication of an accident will result. This signal is sent to the interrupt pin of the micro controller. If even after a particular period of time the vehicle does not move it will indicate that an accident has taken place and an alert will be sent. An RS232 is used for communication between the micro controller and the PC.

# **CHAPTER 4**

# 4.1 HARDWARE DESCRIPTION

The hardware basically consists of four important sections, which perform the processes of obtaining the signals and regulating them. The four sections are the,

- 1. IR Circuit

- 2. Piezo Electric Plate

- 3. Accident Announcement Circuit

- 4. Power Supply Board

# 4.2 IR CIRCUIT

20

#### **INFRARED DIODES:**

Optoelectronics is the integration of optical principles and semiconductor electronics. Optoelectronic components are reliable, cost effective sensors. Infrared emitting diodes are solid-state gallium arsenide devices that emit a beam of radiant flux when forward biased. When the junction is forward biased, electron from the N region will recombine with excess holes of the P material in a specially designed recombination region sandwiched between the P&N type materials.

During this recombination process, energy is radiated away from the device in the form of photons. The generated photons will either be reabsorbed by the structure or leave the surface of the device as radiant energy. A few areas of application of such devices include card and paper tape readers, shaft encoder, data transmission systems and intrusion alarms.

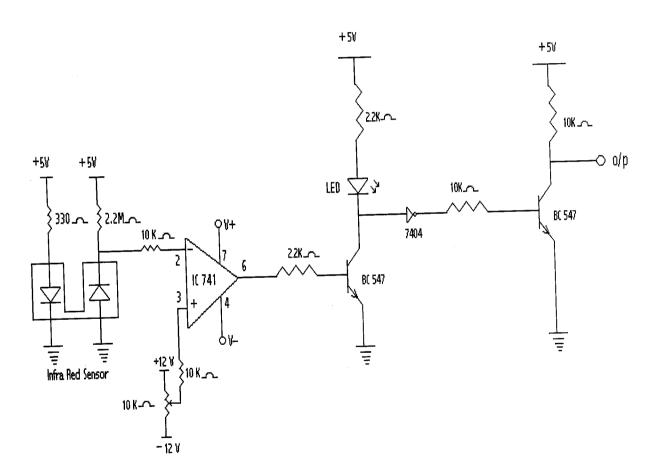

# OVERALL DESCRIPTION:

At the transmitting side, when the IR emits a beam of radiant flux, a voltage will be developed in one input of the comparator. Let that voltage be  $V_1$ . A reference voltage  $V_2$  is developed across the other input. The comparator compares these two voltages  $(V_1 \& V_2)$  and the output of

the comparator is positive and negative going pulses. These pulses are given to the switching circuit to get logic 1 and logic 0. The circuit consists of the following

- 1. Voltage Divider Circuit

- 2. Comparator

- 3. Switching Circuit

#### **VOLTAGE DIVIDER:**

A potential or voltage divider provides a convenient way of getting a variable voltage from a fixed voltage supply. In general, if two resistors with values  $R_1$  and  $R_2$  are connected in series across a supply voltage V and the voltages developed across each are  $V_1$  and  $V_2$  respectively, then, if I is the current flowing, we can say:

$$V_1 = I \times R_1 \dots (1)$$

$V_1 = I \times R_2 \dots (2)$

$V = V_1 + V_2 = I (R_1 + R_2) \dots (3)$

Dividing (1) by (3) we obtain:

$$V_1/V = (I*R_1)/(I*(R_1+R_2))$$

Multiplying both sides by V gives:

$$V_1 = (R_1 * V)/(R_1 + R_2)$$

Similarly from (2) and (3) we get:

$$V_2 = (R_2 * V)/(R1+R2)$$

#### COMPARATOR:

A comparator is a circuit, which compares a signal voltage applied at one input of an op-amp with a known reference voltage at the other input. It is basically an open loop op-amp with an output  $\pm V_{sat}$  (=  $V_{cc}$ ). It may be seen that the change in the output state takes place with an increment in input  $V_1$  of only 2 mV. This is the uncertainty region where output cannot be directly defined. There are basically two types of comparators:

- 1. Inverting comparator

- 2. Non-Inverting comparator

In case of inverting comparator a fixed reference voltage  $V_{ref}$  is applied to (+) input and a time varying signal  $V_i$  is applied to (-) input. The output voltage is at  $+V_{sat}$  for  $V_i < V_{sat}$  and  $V_o$  goes to  $-V_{sat}$  for  $V_i > V_{ref.}$

In case of non-inverting comparator a fixed reference voltage  $V_{ref} \ is \ applied \ to \ (\text{--}) \ input \ and \ a \ time \ varying \ signal \ V_i \ is \ applied \ to \ (\text{+-}) \ input.$  The output voltage is at  $-V_{sat}$  for  $V_i < V_{sat}$  and  $V_o$  goes to  $+V_{sat}$  for  $V_i > V_{ref.}$

#### **SWITCHING CIRCUIT:**

Many solid-state devices are also used in power control applications, and the simplest of these is the discrete bipolar transistor, which is usually used in the switching mode. In the case of the NPN transistor the switch load is wired between collector and supply positive, and in the case of PNP device it is wired between collector and the zero volt. In both cases the switch-driving signal is applied to base via R<sub>1</sub>, which has a typical resistance about twenty times greater than the load resistance value.

In the NPN circuit Transistor Q1 is cut off (acting like an open switch), with its output at the positive supply voltage value, with zero input signal applied, but can be driven to saturation (so that it acts like a closed switch and passes current from collector to emitter) by applying a large positive input voltage, under which condition the output equals Q1's saturation voltage value (typically 200mV to 600 mV). The action of the PNP circuit is the reverse of that described above, and Q1 is driven to

saturation (with its output a few hundred millivolts below the supply voltage value) and passes current from emitter to collector with zero input drive voltage applied, and is cut off (with its output at zero volts) when the input equals the positive supply rail value.

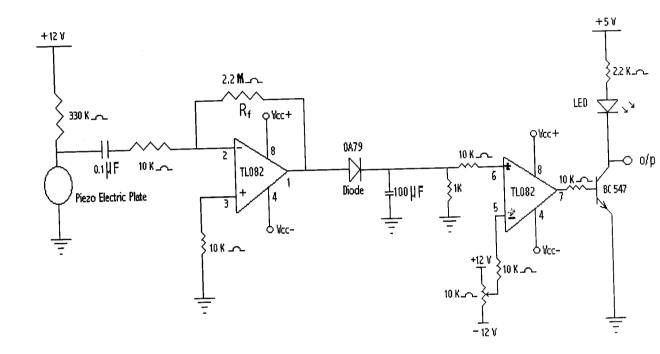

#### 4.3 PIEZO ELECTRIC SENSOR

The piezo electric material is one in which electric potential appears across a certain surface of crystal if the dimensions of the crystal are changed by applying a mechanical force. The potential developed is due to the displacement of the charges. This effect is known as piezo electric effect.

The piezoelectric materials include quartz, ceramics A and B, Rochelle salt, Ammonium dihydrogen phosphate, dipotassium tartarate, lithium sulphate. Except for quartz and ceramics A and B the rest are man made crystals grown from aqueous solution under carefully controlled condition. The ceramic materials are polycrystalline in nature basically made of barium titanate. They do not have piezo electric properties in their original states but these properties are produced by special polarizing treatment.

The piezo electric effect can be made to respond to mechanical deformations of the material in many different modes. The modes are thickness expansion, transverse expansion, thickness shear and face shear. A piezo electric element used for converting mechanical motion to electrical signals maybe thought as charge generator and capacitor. Mechanical

deformation generates a charge and this charge appears as voltage across the terminals. Piezo electric effect is also direction sensitive. Tensile force produces a voltage of one polarity while compressive force produces a voltage of another polarity.

# 4.4 ACCIDENT ANNOUNCEMENT CIRCUIT

This accident announcement circuit is used to determine whether an accident has occurred or not. The accident is simulated by means of tapping the vibration sensor (piezo electric plate). Based on the intensity of vibration a signal will be sent to the micro controller depending upon the output of this circuit. It consists of the following sections.

- 1. Amplifier

- 2. Half wave rectifier

- 3. Comparator

- 4. Voltage divider

- 5. Switching circuit

#### AMPLIFIER:

The piezo electric plate will generate voltage in the range of 5 to 10 mV whenever a mechanical force is applied. This signal is given to the amplifier circuit (non inverting operational amplifier) and gets amplified to about 100 times the original value. The operational amplifier used here is TL082.

#### HALFWAVE RECTIFIER:

The amplified signal is sent to the rectifier, which consists of a diode in which the positive half of the ac signal is allowed to pass and the remaining is cut off. To remove any further ripple content a filter is used.

#### **COMPARATOR:**

A comparator is a circuit, which compares a signal voltage applied at one input of an op-amp with a known reference voltage at the other input. It is basically an open loop op-amp with an output  $\pm V_{sat}$  (=  $V_{cc}$ ). It may be seen that the change in the output state takes place with an increment in input  $V_1$  of only 2 mV. This is the uncertainty region where output cannot be directly defined. There are basically two types of comparators:

- 1.Inverting comparator

- 2.Non Inverting comparator

The operational amplifier used here also is TL082 this is actually a dual operational amplifier and so it performs the operation of both amplifier and comparator in this accident announcement circuit.

#### **SWITCHING CIRCUIT:**

Many solid-state devices are also used in power control applications, and the simplest of these is the discrete bipolar transistor, which is usually used in the switching mode. In the case of the NPN transistor the switch load is wired between collector and supply positive, and in the case of PNP device it is wired between collector and the 0V. In both cases the switch-driving signal is applied to base via R<sub>1</sub>, which has a typical resistance about twenty times greater than the load resistance value.

In the NPN circuit Transistor Q1 is cut off (acting like an open switch), with its output at the positive supply voltage value, with zero input signal applied, but can be driven to saturation (so that it acts like a closed switch and passes current from collector to emitter) by applying a large positive input voltage, under which condition the output equals Q1's saturation voltage value (typically 200mV to 600 mV).

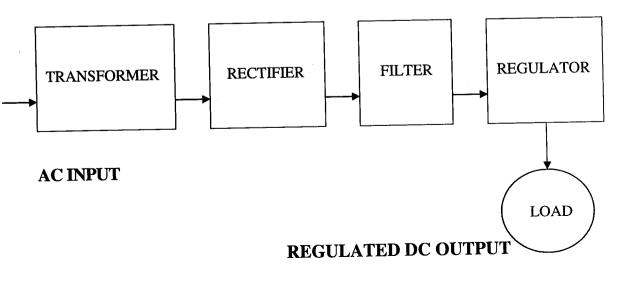

#### 4.5 POWER SUPPLY UNIT

Most electronic circuits work only with low DC voltages so we need a power supply unit that will provide the appropriate voltage. This unit consists of transformer, rectifier, filter and regulator. AC voltage typically 230V rms is given to the primary side of the transformer, which steps the voltage down to the desired level of AC voltage. A diode rectifier is used to obtain a full-wave rectified voltage that is initially filtered by a simple capacitor filter to produce a DC voltage. This resulting DC voltage usually has some ripple or AC voltage variations. A regulator circuit is used to reduce the ripple content and also to maintain the output voltage value constant in spite of variations in the input or at the load.

# **BLOCK DIAGRAM:**

#### TRANSFORMER:

A transformer is a static (or stationary) device for transforming electrical energy from one alternating circuit to another, without changing the frequency. It works with the principle of mutual induction. It can increase or decrease the voltage with a corresponding increase or decrease in current. A transformer can change low voltage to high voltage and high voltage to low voltage but in both cases the frequency remains unchanged. The transformer has no rotating parts hence it is often called a static transformer. A step down transformer can be used for providing necessary supply to the electronic circuits. In our project we are using a 15-0-15 center tapped transformer.

#### **RECTIFIER:**

A rectifier is a device used to convert AC voltage to DC voltage. The DC level obtained from a sinusoidal input can be improved 100% using a process called full-wave rectification. The rectifier uses 4 diodes in a bridge configuration. From the basic bridge configuration we see that during the positive half cycle of the input two diodes (say D2 & D3) are conducting while the other two diodes (D1 & D4) are in "off" state during the period t =0 to T/2. Accordingly during the negative half cycle of the input the

conducting diodes are D1 & D4 and D2 and D3 are in the "off state". Thus the polarity across the load is the same.

#### FILTER:

The filter circuit used here is the capacitor filter circuit where a capacitor is connected at the rectifier output, and a DC is obtained across it. The filtered waveform is essentially a DC voltage with negligible ripples, which is ultimately fed to the load.

# **REGULATOR:**

The output voltage from the capacitor filter will still have ripple content, which has to be further regulated. The voltage regulator is a device, which maintains the output voltage constant irrespective of the change in supply variations, load variation and temperature changes. Here we use two fixed voltage regulators namely LM 7812, LM 7805 and LM7912. The IC 7812 is a +12V regulator IC 7912 is a -12V regulator and IC 7805 is a +5V regulator.

. .

### **CHAPTER 5**

#### **5.1 NEED FOR RS-232-C:**

The RS-232-C was originally set to standardize the interconnections of terminals and host computers through public telephone networks. Modems were used to translate the digital data signals from the computer equipment to analog audio signals suitable for transmission on the telephone network, and back to digital signals at the receiving end.

At that time, each manufacturer of equipment used a different configuration for interfacing a DTE (Data Terminal Equipment) with a DCE (Data Communications Equipment). In 1969, EIA with Bell Laboratories and other parties established a recommended standard for interfacing terminals and data communications equipment. The object of this standard was to simplify the interconnection of equipment manufactured by different firms.

The standard defines electrical, mechanical, and functional characteristics. This standard shortly became RS-232-C (Recommended Standard number 232, revision C from the Electronic Industry Association).

RS-232-C was widely adopted by manufacturers of terminals and computer equipment.

In the 1980's, therapidly growing microcomputer industry found the RS-232-C standard cheap (compared to parallel connections) and suitable for connecting peripheral equipment to microcomputers. RS-232-C quickly became a standard for connecting microcomputers to printers, plotters, backup tape devices, terminals, programmed equipment and other microcomputers. The RS-232-C is so widely available that it is certain to stay with us for some time to come.

By using RS-232-C digital transmission of data is possible, that is transmission of data in the form of 1's and 0's. These increases the speed with which data is transmitted is highly improved thereby providing better communication conditions.

The voltage levels for all RS-232-C signals are as follows. A logic high, or mark, is a voltage between -3V and -15 V under load (-25 V no load). A logic low or space is a voltage between +3 V and +15 under load (+25 V no load). Voltages such as  $\pm 12$  V are commonly used.

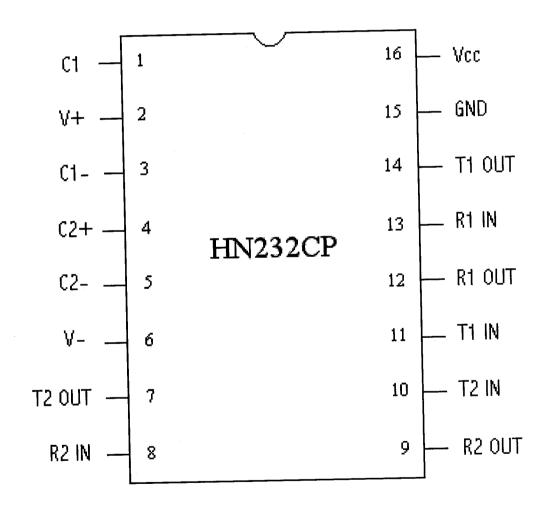

# 5.2 HARDWARE DETAILS:

# PIN DIAGRAM

The various pins in the IC H N232CP are

$V_{cc}$  - Power supply input to the IC 5V +/- 10%

V+ - Internally generated positive supply

V- - Internally generated negative supply

GND- Connected to 0V.

C1+ - External capacitor (positive terminal) is connected to this lead

C1- - External capacitor (negative terminal) is connected to this lead

C2+ - External capacitor (positive terminal) is connected to this lead

C2- - External capacitor (negative terminal) is connected to this lead

$T_{1\text{IN}}$  and  $T_{2\text{IN}}-$  Transmitter inputs

T<sub>10UT</sub> and T<sub>20UT</sub>- Transmitter outputs

R<sub>1IN</sub> and R<sub>2IN</sub>- Receiver inputs

R<sub>10UT</sub> and R<sub>20UT</sub>- Receiver outputs

# The salient features of RS-232-C are

- 1. Requires only a single 5V supply

- 2. High data rate of 120kbps

- 3. Low power consumption

- 4. Low power shutdown function

- 5. Multiple Drivers

- 6. Onboard Voltage/Doubler

- 7. Multiple Receivers these feature hysteresis to greatly improve noise rejection. They can handle up to +/- 30V.

- 8. It can be used for any device that requires a communication port like

- a. Computer Mainframe, Laptop, Portable

- b. Peripherals Printers and Terminals

- c. Instrumentation

- d. Modems.

# **5.3 FUNCTIONAL ASPECTS:**

In our project RS-232-C is used as communication medium between micro controller and PC. A Max level translator is used within the RS-232-C to convert the voltage level (5V) obtained from the micro controller. The UART board in the PC receives the translated voltage (12V) for it's functioning. The pins T 2IN and R20UT are used for interfacing between the micro controller and RS232C.The pins T20UT and R2IN is used for communication between RS-232-C and the PC.

The basic circuit is divided into three sections: The charge pump, Transmitter and Receiver.

# **CHARGE PUMP:**

The charge pump consists of two sections: the voltage doubler and the voltage inverter sections. Each section is driven by a two-phase, internally generated clock to generate +10V and -10V. The normal clock frequency is 16KHz. Each of the capacitors get charged in sequence thereby obtaining the required output. It accepts input voltages up to 5.5V. The output impedance of voltage divider section (V+) is approximately 200

ohms and the output impedance voltage inverter section (V-) is approximately is 450 ohms.

# TRANSMITTER:

They are TTL/CMOS compatible inverters, which translate the inputs to RS232C inputs. The input logic threshold is about 26% of Vcc or 1.3 V for Vcc= 5 V. A logic 1 at the input results in a voltage between -5V and -V at output and a logic 0 results in a voltage between +5V and +V. Each transmitter input has an internal 400 Kohms pull up resistor so any unused input can be left unconnected and its output remains in its low state. The transmitters have an internally limited output slew rate, which is less than 30V/microseconds. The outputs are short-circuited and can be shorted to ground definitely.

# RECIEVERS:

The receiver inputs accept up to +/- 30V while presenting the required 3 Kohms to 7 Kohms input impedance even if the power is off. The output is 0V to Vcc. The output will be low whenever the input is greater than 2.4V and high whenever the input is floating or driven between +0.8V and -30V. The receivers feature 0.5V hysteresis to improve noise rejection.

# **CHAPTER 6**

# 6.1 MICRO CONTROLLER CODING

```

DATA 080H

P0

DATA 090H

P1

DATA 0A0H

P2

DATA 0B0H

P3

0B0H.4

BIT

T0

0D0H.6

AC

BIT

0B0H.5

BIT

T1

0A8H.7

BIT

EA

DATA 0A8H

ΙE

0B0H.7

BIT

RD

0A8H.4

BIT

ES

DATA 0B8H

IΡ

098H.0

BIT

RI

0B0H.2

INTO BIT

0D0H.7

BIT

CY

098H.1

BIT

TI

0B0H.3

INT1

BIT

0B8H.4

BIT

PS

DATA 081H

SP

0D0H.2

OV

BIT

0B0H.6

BIT

WR

SBUF DATA 099H

PCON DATA 087H

SCON DATA 098H

TMODDATA 089H

TCON DATA 088H

088H.1

BIT

TE0

088H.3

BIT

IE1

DATA 0F0H

В

DATA 0E0H

ACC

BIT

0A8H.1

ET0

0A8H.3

ET1

BIT

088H.5

BIT

TF0

088H.7

BIT

TF1

098H.2

RB8

BIT

DATA 08CH

TH<sub>0</sub>

0A8H.0

BIT

EX<sub>0</sub>

0.88H.0

BIT

IT0

DATA 08DH

TH1

```

098H.3

BIT

TB8

```

0A8H.2

BIT

EX1

088H.2

IT1

BIT

0D0H.0

BIT

P

098H.7

SM<sub>0</sub>

BIT

DATA 08AH

TL0

098H.6

BIT

SM1

DATA 08BH

TL1

098H.5

BIT

SM2

0B8H.1

PT0

BIT

BIT

0B8H.3

PT1

0D0H.3

RS<sub>0</sub>

BIT

BIT

088H.4

TR<sub>0</sub>

0D0H.4

BIT

RS1

BIT

088H.6

TR1

0B8H.0

BIT

PX0

0B8H.2

PX1

BIT

DATA 083H

DPH

DATA 082H

DPL

098H.4

BIT

REN

RXD BIT

0B0H.0

0B0H.1

BIT

TXD

0D0H.5

BIT

F0

DATA 0D0H

PSW

SEGMENT CODE

?PR?main?TRACKING

?PR?wheel2?TRACKING SEGMENT CODE

?PR?int0?TRACKING SEGMENT CODE

?PR?ser_init?TRACKING SEGMENT CODE

SEGMENT CODE

?PR?del?TRACKING

?PR?delay?TRACKING SEGMENT CODE

SEGMENT CODE

?C INITSEG

SEGMENT DATA

?DT?TRACKING

CODE (?C_STARTUP)

EXTRN

```

**PUBLIC**

**PUBLIC**

**PUBLIC**

**PUBLIC**

**PUBLIC**

**PUBLIC**

S

p

k

j

i

arr

```

tx4

PUBLIC

tx3

PUBLIC

tx2

PUBLIC

rx4

PUBLIC

tx1

PUBLIC

rx3

PUBLIC

rx2

PUBLIC

rx1

PUBLIC

delay

PUBLIC

del

PUBLIC

ser_init

PUBLIC

int0

PUBLIC

PUBLIC

wheel2

main

PUBLIC

```

### RSEG ?DT?TRACKING

rx1: DS 1 rx2: DS 1 rx3: DS 1 tx1: DS 1 rx4: DS 1 tx2: DS 1 tx3: DS 1 tx4: DS 1

arr: DS 4 i: DS 2

j: DS 2

k: DS 2

p: DS 1

s: DS 2

# RSEG ?C\_INITSEG

DB 002H

DB k

DW 00000H

DB 001H

DB rx1

DB 000H

DB 001H

DB p

DB 000H

; #pragma src;

; #include<reg51.h>

```

; void wheel2();

; void ser_init();

; unsigned int i,j,k=0;

; void ser_init();

; void ser_out();

; void delay();

; void del();

; unsigned char tx1,tx2,tx3,tx4,rx1=0,rx2,rx3,rx4,arr[4],p=0;

; unsigned int s,i;

: main()

RSEG ?PR?main?TRACKING

main:

0

USING

; SOURCE LINE # 12

; {

; SOURCE LINE # 13

: P1=0xff;

; SOURCE LINE # 14

MOV P1,#0FFH

; EA=1;

; SOURCE LINE # 15

SETB EA

; EX0=1;

; SOURCE LINE # 16

SETB EX0

; ser_init();

; SOURCE LINE # 17

ser_init

LCALL

; while(1)

; SOURCE LINE # 18

; {

; SOURCE LINE # 19

; 14:

; SOURCE LINE # 20

?main?14:

; wheel2();

; SOURCE LINE # 21

wheel2

LCALL

; tx1=P1&0x0c;

; SOURCE LINE # 22

MOV A,P1

ANL A,#0CH

MOV tx1,A

; if(tx1!=0)

; SOURCE LINE # 23

```

```

?main?l4

JNZ

; {goto 14;}

; SOURCE LINE # 24

; 11:

; SOURCE LINE # 25

?main?11:

; wheel2();

; SOURCE LINE # 26

LCALL

wheel2

; tx2=P1&0x0c;

; SOURCE LINE # 27

MOV A.P1

ANL A,#0CH

MOV tx2,A

; if(tx2==tx1)

; SOURCE LINE # 28

XRL

A,tx1

?main?l1

JZ

; {goto 11;}

; SOURCE LINE # 29

: 12:

; SOURCE LINE #30

?main?12:

; wheel2();

; SOURCE LINE #31

wheel2

LCALL

; tx3=P1&0x0c;

; SOURCE LINE #32

MOV A,P1

ANL A,#0CH

MOV tx3,A

; if(tx3==tx2)

; SOURCE LINE # 33

A,tx2

XRL

?main?12

JZ

; {goto 12;}

; SOURCE LINE # 34

; 13:

; SOURCE LINE #35

?main?13:

; wheel2();

; SOURCE LINE # 36

wheel2

LCALL

tx4=P1&0x0c;

; SOURCE LINE # 37

MOV A,P1

```

```

ANL A,#0CH

MOV tx4,A

; if(tx4==tx3)

; SOURCE LINE # 38

A,tx3

XRL

?main?13

17.

{goto 13;}

; SOURCE LINE #39

?C0010:

if((tx2==0x04)&&(tx3==0x0c)&&(tx4==0x08))

; SOURCE LINE #41

MOV A,tx2

CJNE A,#04H,?C0011

MOV A,tx3

CJNE A,#0CH,?C0011

MOV A,tx4

CJNE A,#08H,?C0011

{

; SOURCE LINE # 42

SBUF=' F';

; SOURCE LINE # 43

MOV SBUF,#046H

delay();

; SOURCE LINE # 44

delay

LCALL

SCON=0x40;

; SOURCE LINE # 45

del();

; SOURCE LINE # 46

L?0036

LCALL

; }

; SOURCE LINE # 47

?C0011:

; if((tx2==0x08)&&(tx3==0x0c)&&(tx4==0x04))

; SOURCE LINE # 48

MOV A,tx2

CJNE A,#08H,?main?l4

MOV A,tx3

A,#0CH

XRL

?main?l4

JNZ

MOV A,tx4

A,#04H

XRL

?main?l4

JNZ

; {

; SOURCE LINE # 49

```

```

SBUF=' R';

; SOURCE LINE # 50

MOV SBUF,#052H

delay();

: SOURCE LINE # 51

delay

LCALL

SCON=0x40;

: SOURCE LINE # 52

del();

; SOURCE LINE # 53

L?0036

LCALL

; }

; SOURCE LINE # 54

; }

; SOURCE LINE # 55

SJMP ?main?l4

: END OF main

; }

; void wheel2()

RSEG ?PR?wheel2?TRACKING

wheel2:

0

USING

; SOURCE LINE # 58

; {

; SOURCE LINE # 59

; if(k==0)

; SOURCE LINE # 60

MOV A,k+01H

ORL

A,k

?C0014

INZ

; {

; SOURCE LINE #61

; rx1=P1&0x03;

; SOURCE LINE # 62

MOV A,P1

ANL A,#03H

MOV rx1,A

: if(rx1 == 0x00)

; SOURCE LINE # 63

?C0022

JNZ

; {

; SOURCE LINE # 64

; k=1;

```

```

; SOURCE LINE # 65

MOV k,A

MOV k+01H,#01H

; goto retr;

; SOURCE LINE # 66

RET

; }

; SOURCE LINE # 67

; goto retr;

; SOURCE LINE # 68

; }

; SOURCE LINE # 69

?C0014:

; if(k==1)

; SOURCE LINE # 70

MOV A,k+01H

A,#01H

XRL

A,k

ORL

?C0022

JNZ

; {

; SOURCE LINE #71

; rx2=P1&0x03;

; SOURCE LINE #72

MOV A,P1

ANL A,#03H

MOV rx2,A

; if(rx2!=rx1)

; SOURCE LINE #73

XRL A,rx1

?C0022

JZ

; {

; SOURCE LINE #74

arr[p]=rx2;

; SOURCE LINE #75

MOV A,#LOW (arr)

ADD A,p

MOV RO,A

MOV @R0,rx2

rx1=rx2;

; SOURCE LINE #76

MOV rx1,rx2

p++;

; SOURCE LINE #77

INC

p

if(p==3)

; SOURCE LINE #78

```

```

MOV A,p

XRL A.#03H

JNZ

?C0022

{

; SOURCE LINE #79

if((arr[0]==0x01)\&\&(arr[1]==0x03)\&\&(arr[2]==0x02))

; SOURCE LINE #80

MOV A, arr

CJNE A,#01H,?C0020

MOV A,arr+01H

CJNE A,#03H,?C0020

MOV A,arr+02H

CJNE A,#02H,?C0020

{

: SOURCE LINE #81

SBUF=' A';

; SOURCE LINE #82

MOV SBUF,#041H

delay();

: SOURCE LINE #83

LCALL

delay

SCON=0x40:

; SOURCE LINE #84

MOV SCON,#040H

del();

; SOURCE LINE #85

del

LCALL

}

; SOURCE LINE #86

?C0020:

if((arr[0]==0x02)\&\&(arr[1]==0x03)\&\&(arr[2]==0x01))

; SOURCE LINE #87

MOV A,arr

CJNE A,#02H,?C0021

MOV A,arr+01H

CJNE A,#03H,?C0021

MOV A,arr+02H

CJNE A,#01H,?C0021

{

: SOURCE LINE # 88

SBUF=' B';

; SOURCE LINE #89

MOV SBUF,#042H

delay();

; SOURCE LINE # 90

LCALL

delay

```

```

SCON=0x40;

; SOURCE LINE #91

MOV SCON,#040H

del();

; SOURCE LINE # 92

del

LCALL

; SOURCE LINE # 93

?C0021:

p=0;

; SOURCE LINE # 94

CLR A

MOV p,A

k=0;

; SOURCE LINE #95

MOV k,A

MOV k+01H,A

; }

; SOURCE LINE # 96

; }

; SOURCE LINE #97

; goto retr;

; SOURCE LINE #98

; }

; SOURCE LINE #99

; retr:

; SOURCE LINE # 100

?wheel2?retr:

; }

; SOURCE LINE # 102

?C0022:

RET

; END OF wheel2

00003H

CSEG AT

LJMP int0

; void int0(void) interrupt 0

RSEG ?PR?int0?TRACKING

0

USING

int0:

PUSH ACC

PUSH B

```

```

PUSH DPH

PUSH DPL

PUSH PSW

MOV PSW,#00H

PUSH AR0

PUSH AR1

PUSH AR2

PUSH AR3

PUSH AR4

PUSH AR5

PUSH AR6

PUSH AR7

USING

0

; SOURCE LINE # 104

; {

ser_init();

; SOURCE LINE # 106

ser_init

LCALL

SBUF=' X';

; SOURCE LINE # 107

MOV SBUF,#058H

delay();

; SOURCE LINE # 108

delay

LCALL

SCON=0x40;

; SOURCE LINE # 109

MOV SCON,#040H

del();

; SOURCE LINE # 110

LCALL

del

; }

; SOURCE LINE # 111

AR7

POP

AR6

POP

AR5

POP

AR4

POP

AR3

POP

AR2

POP

AR1

POP

AR<sub>0</sub>

POP

PSW

POP

POP

DPL

DPH

POP

POP

В

ACC

POP

RETI

```

```

; END OF int0

; void ser_init()

RSEG ?PR?ser_init?TRACKING

ser_init:

USING

; SOURCE LINE # 114

; {

; SOURCE LINE # 115

: TH1=0x72;

; SOURCE LINE # 116

MOV TH1,#072H

; TMOD=0x20;

; SOURCE LINE # 117

MOV TMOD,#020H

; TR1=1;

; SOURCE LINE # 118

SETB TR1

; delay();

; SOURCE LINE # 119

delay

LCALL

; SCON=0x40;

; SOURCE LINE # 120

MOV SCON,#040H

; }

; SOURCE LINE # 121

RET

: END OF ser_init

; void del()

RSEG ?PR?del?TRACKING

L?0036:

0

USING

MOV SCON,#040H

del:

; SOURCE LINE # 123

; {

; SOURCE LINE # 124

; for(s=0;s=8000;s++)

; SOURCE LINE # 125

CLR A

```

--

```

MOV s,A

MOV s+01H,A

?C0025:

; {}

; SOURCE LINE # 126

s+01H

INC

MOV A,s+01H

?C0033

JNZ

INC

S

?C0033:

CJNE A,#041H,?C0025

MOV A,s

CJNE A,#01FH,?C0025

; }

; SOURCE LINE # 127

?C0028:

RET

; END OF del

; void delay()

RSEG ?PR?delay?TRACKING

delay:

; SOURCE LINE # 129

; {

; SOURCE LINE # 130

: for(j=0;j<=120;j++)

; SOURCE LINE # 131

CLR A

MOV j,A

MOV j+01H,A

?C0029:

; {}

; SOURCE LINE # 132

j+01H

INC

MOV A,j+01H

?C0035

JNZ

INC

j

?C0035:

A,#079H

XRL

ORL

A,i

?C0029

JNZ

; }

; SOURCE LINE # 133

?C0032:

```

RET ; END OF delay

END

#### 6.2 C PROGRAM

```

#include <stdlib.h>

#include<stdio.h>

#include<conio.h>

#include<dos.h>

#include<process.h>

#include<ctype.h>

#include <graphics.h>

void screen(void);

void map(void);

void main()

{

struct time t;

int a,ah,al,result,in=1,mode=2,flag=0,t1,t2;

int gdriver = DETECT, gmode;

void *one;

unsigned int size1;

int key,x1=50,x2,y2,y1=50, maxx, maxy,style=0,userpat;

initgraph(&gdriver, &gmode, "\\TC\\BGI");

maxx = getmaxx() + 1;

maxy = getmaxy() + 1;

x2=x1=276;//maxx/2;

y2=y1=298;//maxy/2;

```

```

setcolor(12);

circle(40,40,3);

setfillstyle(1,5);

floodfill(41,41,12);

size1=imagesize(36,36,44,44);

one=malloc(size1);

getimage(36,36,44,44,one);

cleardevice();

userpat = 100;

setlinestyle(style, userpat,3);

rectangle(10,10,maxx-10,maxy-10);

screen();

setlinestyle(style, userpat,1);

map();

while(!kbhit())

{

setcolor(15);

AH = 0x03;

DX=0x00;

geninterrupt(0x14);

ah=_AH;

al=AL;

gettime(&t);

```

```

t1=t.ti_sec;

if(flag==0)

{

t2=t1;

flag=1;

}

if(abs(t1-t2)>20 && t1<50 && t2<50 && a=4)

if( (ah & 0x01) == 0x01)

{

gettime(&t);

t2=t.ti_sec;

result = inportb(0x3f8);

a=result;

switch (a)

{

case 65:

key=54;

break;

case 66:

key=52;

break;

case 70:

key=50;

```

```

break;

case 82:

key=56;

break;

case 88:

key=0;

break;

//default:

//printf("%d",a);

}

switch (key)

{

case 0:

gotoxy(35,12);

printf("Problem");

break;

case 56:

if(y1>=1)

y1=y1-in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

line(x2,y2,x1,y1);

break;

```

72

```

case 54:

if(x1 < maxx)

x1=x1+in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

line(x2,y2,x1,y1);

break;

case 50:

if(y1<maxy)

y1=y1+in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

line(x2,y2,x1,y1);

break;

case 52:

if(x1>=1)

x1=x1-in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

line(x2,y2,x1,y1);

break;

case 55:

if(x1>=1)

```

```

x1=x1-in;

if(y1>=1)

y1=y1-in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

line(x2,y2,x1,y1);

break;

case 57:

if(x1 < maxx)

x1=x1+in;

if(y1>=1)

y1=y1-in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

line(x2,y2,x1,y1);

break;

case 49:

if(x1>=1)

x1=x1-in;

if(y1<maxy)

y1=y1+in;

//putpixel(x1,y1,15);

//putimage(x1,y1,one,mode);

```

```

line(x2,y2,x1,y1);

break;

case 51:

if(x1 < maxx)

x1=x1+in;

if(y1<maxy)

y1=y1+in;

//putimage(x1,y1,one,mode);

//putpixel(x1,y1,15);

line(x2,y2,x1,y1);

break;

default:

break;

}

x2=x1;

y2=y1;

}

}

getch();

```

}

```

//setfillstyle(1,1);

//floodfill(100,100,12);

setcolor(13);

settextstyle(1,0,2);

outtextxy(546,50,"N");

setcolor(11);

settextstyle(1,0,3);

outtextxy(170,50,"VEHICLE TRACKING SYSTEM");

setcolor(13);

outtextxy(172,48,"VEHICLE TRACKING SYSTEM");

setcolor(3);

line(520,100,580,100);

line(550,70,550,170);

}

void map(void)

{

int r=5;

setcolor(2);

circle(20,450,r);

setfillstyle(1,10);

```

```

floodfill(21,453,2);

setcolor(14);

settextstyle(1,0,1);

outtextxy(21,448,"CRTSR");

setcolor(2);

circle(80,350,r);

setfillstyle(1,10);

floodfill(81,353,2);

setcolor(14);

outtextxy(81,348,"Erode");

setcolor(2);

circle(280,300,r);

setfillstyle(1,10);

floodfill(281,303,2);

setcolor(14);

outtextxy(281,308,"Namakkal");

setcolor(2);

circle(230,130,r);

setfillstyle(1,10);

floodfill(232,133,2);

setcolor(14);

outtextxy(231,138,"Dharmapuri");

setcolor(2);

```

```

circle(280,230,r);

setfillstyle(1,10);

floodfill(281,233,2);

setcolor(14);

outtextxy(281,238,"Salem");

setcolor(2);

circle(420,300,r);

setfillstyle(1,10);

floodfill(421,303,2);

setcolor(14);

outtextxy(421,308,"AMSEC");

setcolor(2);

circle(550,450,r);

setfillstyle(1,10);

floodfill(551,453,2);

setcolor(14);

outtextxy(551,448,"Trichy");

setcolor(2);

circle(530,250,r);

setfillstyle(1,10);

floodfill(531,253,2);

setcolor(14);

outtextxy(531,248,"Thuraiyur"); }

```

#### **CONCLUSION**

The concepts and the software and hardware logic used in this project have been successfully implemented. All the circuits have been tested and the results were satisfactory. Thus by using an embedded system all the initial difficulties faced by the authorities like

- Determining whether an accident has taken place.

- Determining the location of the accident.

- Determining the time of the accident

- Not being able to give the required emergency medical help, which is a must in most accident cases.

can be overcome.

#### SCOPE FOR DEVELOPMENTS:

The project that we have implemented is a wired version a further development on that would be to make the communication between the vibration sensor and the micro controller wireless thereby giving a better perspective. Implementing GPS for determining the location of the vehicle could be a future development for our method of automation. We have used

only one vibration sensor in our project but in real time applications more than one sensor will have to be placed at strategic and vulnerable locations of the vehicle and this depends on the make and design of the vehicle. To conclude the implementation of this concept will be very beneficial to mankind and will be revolutionary in alleviating a lot of undue suffering. We as novices have taken sincere efforts to make this project a successful one.

. \_

OUTPUT

TAGGIDO);

rended then the

Berry

REFERENCES

#### <u>REFERENCES</u>

- The 8051 Micro Controller Architecture and Applications, Kenneth. J. Ayala.

- Handbook of 8 bit micro controller, Intel Corporation 1989 USA.

- 3. Linear Integrated Circuits, D. Roy Choudhury & Shail Jain, New Age International P. Ltd, 1991.

- Microprocessors and Microcomputer Based System Design,

Mohamed Rafiquzzman, UBS Publisher's Distributors Ltd.

- 5. www.atmel.com

- 6. www. Iweil.com/micro/8051/8951atmel.com

- 7. Statistics on road accidents-TamilNadu state transport authority.htm

PIN OUT

### **ATMEL 89C51**

| 그 그 아이스 | P13     | 2 A A 4 5 T 7 8 9 10 9 11 C 13 C 14 15 5 16 17 1 | 40              |

|---------------------------------------------|---------|--------------------------------------------------|-----------------|

| XTAL1   19   22   P2.1 (A9)                 | XTAL2 🗆 | 18                                               | 23   P2.2 (A10) |

| GND   20   21   P2.0 (A8)                   | XTAL1 🗀 | 19                                               | 22   P2.1 (A9)  |

#### controller Instruction Set

rrupt response time information, refer to the hardware description chapter.

ctions that Affect Flag Settings<sup>(1)</sup>

| tion | Flag |              |    | Instruction | Flag |    |       |  |

|------|------|--------------|----|-------------|------|----|-------|--|

| LION | С    | OV           | AC |             | С    | ov | AC    |  |

|      | X    | ×            | Х  | CLR C       | 0    |    |       |  |

|      | X    | X            | X  | CPL C       | X    |    |       |  |

|      | X    | X            | X  | ANL C,bit   | X    |    | ļ<br> |  |

|      | 0    | X            |    | ANL C,/bit  | X    |    |       |  |

|      | 0    | X            |    | ORL C,bit   | X    |    |       |  |

|      | X    |              |    | ORL C,/bit  | X    |    |       |  |

|      | X    | <del> </del> | +  | MOV C,bit   | X    |    |       |  |

|      | X    |              | +  | CJNE        | Х    |    |       |  |

| ·C   | 1    |              |    |             |      |    |       |  |

Operations on SFR byte address 208 or bit addresses 209-215 (that is, the PSW or bits in the PSW) also affect flag settings.

Instruction Set and Addressing Modes

| 156  U | Ction bet and that the state of |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Register R7-R0 of the currently selected Register Bank.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ct     | 8-bit internal data location's address. This could be an Internal Data RAM location (0-127) or a SFR [i.e., I/O port, control register, status register, etc. (128-255)].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 8-bit internal data RAM location (0-255) addressed indirectly through register R1or R0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ta     | 8-bit constant included in instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |